Логические основы микропроцессорной техники

Кроме алфавитно-цифровой информации, которая представляется двоичными константами 1 и 0, в микропроцессорной технике применяется логическая информация. В зависимости от того, истинно ли какое-то событие или нет, переменная, отображающая эту информацию, может принимать два фиксированных значения: да или нет, истина или ложь. Такие переменные называются логическими (булевыми) переменными.

Два значения, которые принимают логические переменные, называются ее логическими константами и обозначаются цифрами 1 и 0. Чтобы не смешивать с двоичными цифрами, эти константы называются логическим нулем и логической единицей.

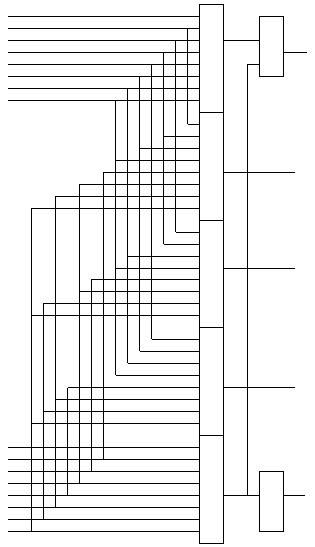

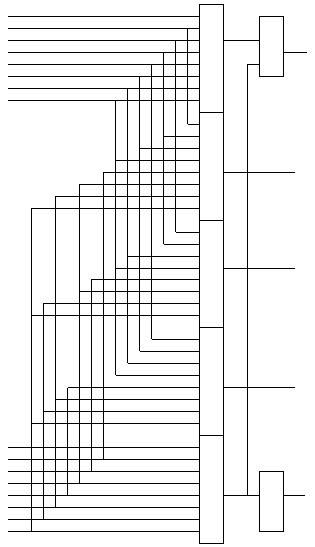

Шифратор – комбинационная схема, предназначенная для преобразования унитарного (однопозиционного) кода в двоичный позиционный код. Типичным примером является шифратор клавиатуры (рисунок 44) для ввода в цифровое устройство кода в шестнадцатеричной системе. При ненажатых клавишах на всех входах шифратора обеспечивается логический ноль, а нажатая клавиша подает на соответствующий вход шифратора логическую единицу. Совокупность сигналов на выходе образует код в двоичной системе, соответствующий нажатой клавише. Шифратор вырабатывает также осведомительный сигнал z при нажатии любой из клавиш. Так, если нажата клавиша, соответствующая символу 8, то, как видно из рисунка 44, Y 1 = Y 2 = Y 4 = 0, а Y 8 = 1. Информационный сигнал z = 1. Если нажата клавиша, соответствующая символу 4, то Y 1 = Y 2 = Y 8 = 0, Y 4 = 1, z = 1. Если же нажата клавиша R, то Y 1 = Y 2 = Y 4 = Y 8 = z = 1.

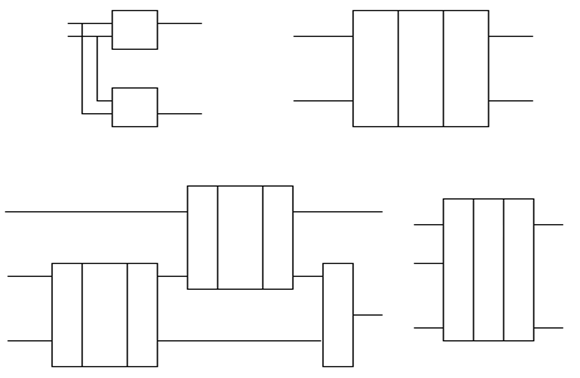

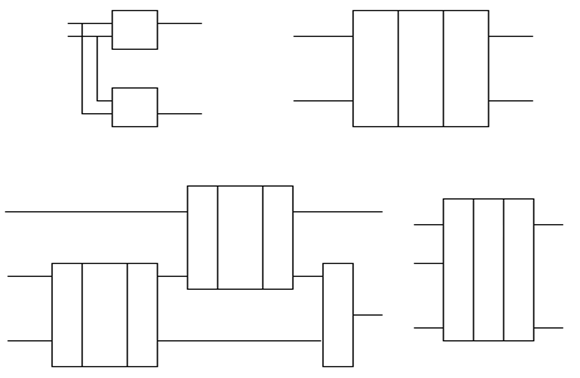

Сумматор – операционный узел, выполняющий арифметическое суммирование кодов чисел. Сложение для i -го разряда осуществляется над цифрами Аi, и Bi тех же разрядов, слагаемых с учетом переноса Сi- 1 из младшего разряда. Схема, реализующая эти уравнения, называется полусумматором (рисунок 45). Пусть Аi = 1, Bi = 0. В соответствии с приведенной схемой на выходе логического элемента ИСКЛЮЧАЮЩЕЕ – ИЛИ имеет место Si = 1, а на выходе логического элемента И – Ci+ 1 = 0.

Рисунок 44 – Шифратор клавиатуры

Полный одноразрядный сумматор можно рассматривать как логическое устройство, имеющее три входа (две цифры слагаемых Аi и Bi и цифра переноса Сi из соседнего младшего разряда) и два выхода (сумма S и перенос в старший разряд Сi+ 1). На рисунке 45 приведены схема и условное графическое обозначение сумматора, построенного на базе двух полусумматоров.

Рисунок 45 – Схемы и условные обозначения полусумматора и сумматора:

а – полусумматор; б – графическое обозначение полусумматора;

в – сумматор; г – графическое обозначение сумматора

Date: 2015-05-04; view: 753; Нарушение авторских прав | Понравилась страница? Лайкни для друзей: |

|

|