Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Построение ЗУ с заданной организацией

|

|

В современных ЭВМ минимальной адресуемой единицей памяти является, как правило, 1 байт. В связи с этим обмен с памятью организуется блоками, кратными этой величине: байтами, словами, двойными словами, учетверенными словами, в зависимости от выполняемой процессором команды и разрядности внешней шины данных. Такой обмен проходит под управлением специальных сигналов, поступающих по системной шине. Преобразование информации из формата ее представления на шине данных в формат, учитывающий организацию конкретных схем памяти, осуществляется специальными интерфейсными схемами. Большие интегральные схемы (БИС), на которых строятся модули памяти, являются изделиями электронной промышленности и могут иметь различную организацию. Разработчики средств вычислительной техники должны учитывать имеющуюся у них номенклатуру БИС памяти, чтобы построить запоминающее устройство необходимой емкости и организации. Для этой цели может проводиться объединение нескольких БИС либо с целью увеличения количества слов в модуле памяти, либо для наращивания разрядности каждого слова, либо с той и другой целью одновременно.

Рассмотрим варианты построения блока памяти необходимой организации при наличии заданных БИС памяти.

- Построить ОЗУ с организацией 8К*8 разрядов на БИС с организацией 1К*8 разрядов (рис.10).

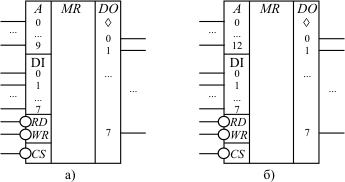

Рис. 10. Условно-графические обозначения запоминающих устройств с различной организацией: а - 1К*8 разрядов; б - 8К*8 разрядов

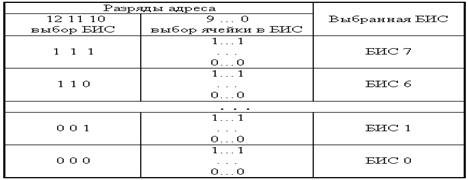

В данном случае требуется построить модуль памяти, имеющий большее число слов, чем в составляющих его БИС. Модуль памяти будет состоять из восьми БИС. Для обращения к модулю памяти используется 13-разрядный адрес (А12 А0), поступающий по шине адреса (ША). Три старших разряда (А12-А10) определяют ту схему, которая в данный момент включается в работу, а каждая ячейка внутри любой БИС определяется 10-ю младшими разрядами адреса (А9-А0) (рис. 10.1).

Рис. 10.1. Организация модуля памяти

При единичном значении сигнала на входе выбора кристалла БИС (CS=1) выходные разряды данных находятся в третьем состоянии, то есть как бы отключены от шины (DO=Z).Таким образом, при любом значении кода на шине адреса всегда в работе находится одна и только одна из восьми БИС (рис. 10.2).

Рис. 10.2. Запоминающее устройство объемом 8К*8 разрядов на БИС с организацией 1К*8 разрядов

В реальных микросхемах шины данных записи и чтения (DI и DO) обычно представляют собой общую двунаправленную шину.

Сигналы на шине управления означают: MW - сигнал записи в память, MR - сигнал чтения из памяти.

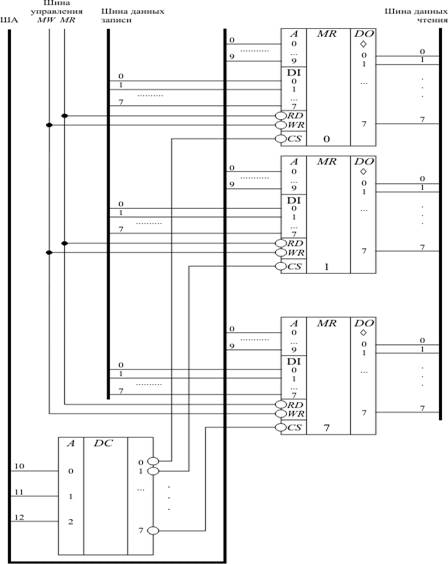

- Построить ОЗУ с организацией 1К*8 разрядов на БИС с организацией 1К*1 разряд (рис.11).

Рис. 11. Условно-графическое обозначение БИС с организацией 1К*1 разряд

В данном случае требуется увеличить разрядность слова памяти. Так как все разряды одного слова должны записываться и считываться одновременно, то все БИС должны работать параллельно. Модуль памяти будет состоять из восьми БИС (рис. 11.1). Если разрабатываемый блок является частью модуля памяти, имеющего объем больше, чем 1К слов (например, 8К), то необходим специальный дешифратор, который будет дешифрировать старшие разряды адреса аналогично тому, как показано на рис. 10.2 и включать в работу данный блок.

Рис. 11.1. Запоминающее устройство объемом 1К*8 разрядов на БИС с организацией 1К*1 разряд

Задача

Представим числа -7310 и -3210 в обратном коде.

Представим число -73 в двоичном коде.

73 = 10010012

Обратный код для положительного числа совпадает с прямым кодом. Для отрицательного числа все цифры числа заменяются на противоположные (1 на 0, 0 на 1), а в знаковый разряд заносится единица.

Двоичное число 1001001 имеет обратный код 1,0110110

Представим число -32 в двоичном коде.

32 = 1000002

Двоичное число 100000 имеет обратный код 1,011111

Сложим числа 10110110 и 1011111

В 1-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 2-й разряд.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

В 2-ом разряде возникло переполнение (1 + 1 + 1 = 11). Поэтому записываем 1, а 1 переносим на 3-й разряд.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

В 3-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 4-й разряд.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

В 4-ом разряде возникло переполнение (1 + 1 + 1 = 11). Поэтому записываем 1, а 1 переносим на 5-й разряд.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

В 5-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 6-й разряд.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

В 6-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 7-й разряд.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

В 7-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 8-й разряд.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

В итоге получаем:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Возник перенос из знакового разряда. Добавим его (т.е. 1) к полученному числу (тем самым осуществляя процедуру циклического переноса).

В 0-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 1-й разряд.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

В итоге получаем:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Результат сложения: 00010110

Получили число 00010110. В десятичном представлении это число имеет вид:

Для перевода необходимо умножить разряд числа на соответствующую ему степень разряда.

00010110 = 27*0 + 26*0 + 25*0 + 24*1 + 23*0 + 22*1 + 21*1 + 20*0 = 0 + 0 + 0 + 16 + 0 + 4 + 2 + 0 = 22

Результат сложения (в десятичном представлении): 22

Билет 15

Вопрос 1

Прямая адресация предполагает, что эффективный адрес является частью команды. Так как ЭА состоит из 16 разрядов, то и соответствующее поле команды должно иметь такую же длину.

При регистровой косвенной адресации эффективный адрес операнда находится в базовом регистре BX или одном из индексных регистров DI либо SI:

Обозначение имени регистра в квадратных скобках указывает на содержимое соответствующего регистра. Фигурные скобки - символ выбора одной из нескольких возможных альтернатив.

При регистровой относительной адресации эффективный адрес равен сумме содержимого базового или индексного регистра и смещения:

Обозначения disp8 и disp16 здесь и далее указывают на 8- или 16-разрядное смещение соответственно.

Эффективный адрес при базово-индексной адресации равен сумме содержимого базового и индексного регистров, определяемых командой:

Наиболее сложен механизм относительной базово-индексной адресации. Эффективный адрес в этом случае равен сумме 8- или 16-разрядного смещения и базово-индексного адреса:

Вопрос 2

Ламповые ЭВМ

В середине 50-ых гг. XX века, когда ламповые компьютеры достигли «насыщения», ряд фирм объявил о работах по созданию транзисторных ЭВМ. Первоначально это вызвало скептицизм из-за того, что производство полупроводников будет сложным и дорогостоящим. Однако этого не случилось — постоянно совершенствовались методы производства транзисторов. В 1955 году в США было объявлено о создании цифрового компьютера TRADIC, построенного на 800 транзисторах и 11 000 германиевых диодах. В этом же году фирма объявила о создании полностью транзисторной ЭВМ. Первая такая машина «Philco-2000» была сделана в ноябре 1958 года, она содержала 56 тыс. транзисторов, 1 200 диодов, но всё же в её составе было 450 электронных ламп. «Philco-2000» выполняла сложение за 1,7 мкс, умножение — за 40,3 мкс.

Транзисторные ЭВМ

В декабре 1961 года специальный комитет фирмы IBM, изучив техническую политику фирмы в области разработки вычислительной техники, представил план-отчёт создания ЭВМ на микроэлектронной основе. Во главе реализации плана встали два ведущих разработчика фирмы — Д. Амдал и Г. Блау. Работая с проблемой производства логических схем, они предложили при создании семейства использовать гибридные интегральные схемы, для чего при фирме в 1963 году было открыто предприятие по их выпуску. В начале апреля 1964 года фирма IBM объявила о создании шести моделей своего семейства IBM-360 («System-360»), появление которого ознаменовало появление компьютеров третьего поколения.

Эпоха интегральных схем

Это поколение ЭВМ связано с развитием микропроцессорной техники. В 1971 году компания Intel выпустила микросхему Intel-4004 — первый микропроцессор и родоначальник доминирующего и самого известного сегодня семейства.

Четвёртое поколение

В 1989 году появляется новая разработка компании Intel — микропроцессор Intel-80486 (Intel-80486DX). Этот процессор ознаменовал начало пятого поколения. Этот процессор был полностью совместим с PC семейством Intel-80x86, кроме того, содержал в себе математический сопроцессор и 8 Кбайт кэш-памяти. Этот процессор был более совершенен по сравнению с микропроцессором Intel-80386, его тактовая частота состояла 33 МГц.

Задача

Представим числа 1710 и -2510 в дополнительном коде.

Представим число 17 в двоичном коде.

17 = 100012

Обратный код для положительного числа совпадает с прямым кодом. Для отрицательного числа все цифры числа заменяются на противоположные (1 на 0, 0 на 1), а в знаковый разряд заносится единица.

Двоичное число 10001 имеет обратный код 0,10001

Дополнительный код положительного числа совпадает с прямым кодом. Для отрицательного числа дополнительный код образуется путем получения обратного кода и добавлением к младшему разряду единицы.

Число 17 представляется в двоичном дополнительном коде как 0,10001

Представим число -25 в двоичном коде.

25 = 110012

Двоичное число 11001 имеет обратный код 1,00110

В итоге получаем:

| 5 | 4 | 3 | 2 | 1 | 0 |

Число -25 представляется в двоичном дополнительном коде как 1,00111

Сложим числа 010001 и 100111

В 0-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 1-й разряд.

| 5 | 4 | 3 | 2 | 1 | 0 |

В 1-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 2-й разряд.

| 5 | 4 | 3 | 2 | 1 | 0 |

В 2-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 3-й разряд.

| 5 | 4 | 3 | 2 | 1 | 0 |

В итоге получаем:

| 5 | 4 | 3 | 2 | 1 | 0 |

Результат сложения: 111000

В старшем бите 1. Следовательно, в результате сложения получили отрицательное число. Переведем его обратно в прямой код. Для этого найдем обратный код (инвертируем все биты, кроме знакового): 00111

Дополнительный код (прибавляем 1):

В 0-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 1-й разряд.

| 4 | 3 | 2 | 1 | 0 |

В 1-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 2-й разряд.

| 4 | 3 | 2 | 1 | 0 |

В 2-ом разряде возникло переполнение (1 + 1 = 10). Поэтому записываем 0, а 1 переносим на 3-й разряд.

| 4 | 3 | 2 | 1 | 0 |

В итоге получаем:

| 4 | 3 | 2 | 1 | 0 |

Получили число 01000. В десятичном представлении это число имеет вид:

Для перевода необходимо умножить разряд числа на соответствующую ему степень разряда.

01000 = 24*0 + 23*1 + 22*0 + 21*0 + 20*0 = 0 + 8 + 0 + 0 + 0 = 8

Результат сложения (в десятичном представлении): -8

Билет 16

Вопрос 1

С целью лучшего понимания архитектуры ЭВМ рассмотрим машинное представление команд различных форматов, использующих различные режимы адресации операндов.

Рассмотрим это на примере операции сложения. Так как в системе команд ЭВМ, базирующихся на микропроцессорах фирмы Intel, результат операции записывается на место первого операнда, то данная операция будет иметь вид: a=a+b.

Для наглядного представления команды будем пользоваться ее символической записью, приближенной к записи на языке Ассемблер. Общий формат ассемблерной команды имеет следующий вид:

[Метка:] Мнемоника_операции Операнд,Операнд [; Комментарий]Метка - это идентификатор, присваиваемый адресу первого байта команды. Наличие метки в команде необязательно. При отсутствии метки двоеточия быть не должно.

Во всех командах необходимо наличие мнемоники, обозначающей выполняемую команду.

Наличие и количество (один или два) операндов зависит от команды. В случае двух операндов они разделяются запятой, при этом первым указывается операнд -приемник, а вторым - операнд -источник. Примеры обозначения операндов при различных режимах адресации будут рассмотрены ниже.

Поле комментария предназначено для пояснения программы и может содержать любую комбинацию символов. При отсутствии комментария точка с запятой может не ставиться.

Date: 2015-09-05; view: 1681; Нарушение авторских прав