Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Распределение памяти предполагает удовлетворение потребностей как пользователей, так и системных средств. Эти требования в большей части противоречивы

|

|

Системные цели заключаются, прежде всего, в увеличении степени использования оперативной памяти при параллельном развитии нескольких процессов в мультипрограммном режиме, а также в реализации защиты информации при развитии этих процессов, обеспечении взаимодействия между процессами и т. д.

Билет №5.

1. Регистр хранения

Регистр — последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, обычно D, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств.

Основой построения регистров являются D-триггеры, RS-триггеры.

Содержание [убрать]

1 Операции в регистрах

2 Классификация регистров

3 Типы регистров

3.1 Параллельные регистры

3.2 Сдвигающие (последовательные) регистры

4 Регистры процессора

5 Троичные регистры

6 Примечания

7 Литература

Операции в регистрах[править | править исходный текст]

Типичными являются следующие операции:

приём слова в регистр;

передача слова из регистра;

поразрядные логические операции;

сдвиг слова влево или вправо на заданное число разрядов;

преобразование последовательного кода слова в параллельный и обратно;

установка регистра в начальное состояние (сброс).

Классификация регистров[править | править исходный текст]

Регистры классифицируются[1] по следующим видам:

накопительные (регистры памяти, хранения)[2][3];

сдвигающие[4][5][6][7][8][9][10][11][12][13][14].

В свою очередь сдвигающие регистры делятся:

по способу ввода-вывода информации:

параллельные - запись и считывание информации происходит одновременно на все входы и со всех выходов[15];

последовательные - запись и считывание информации происходит в первый триггер, а та информация, которая была в этом триггере, перезаписывается в следующий - то же самое происходит и с остальными триггерами[16][17];

комбинированные;

по направлению передачи информации:

однонаправленные;

реверсивные[18][19].

по основанию системы счисления

двоичные

троичные

десятичные

Типы регистров[править | править исходный текст]

Регистры различают по типу ввода (загрузки, приёма) и вывода (выгрузки, выдачи) информации:

С последовательным вводом и выводом информации

С параллельным вводом и выводом информации

С параллельным вводом и последовательным выводом. Например: SN74LS165J(N), SN74166J(N), SN74LS166J(N)

С последовательным вводом и параллельным выводом. Например: SN7416J(N), SN74LS164J(N), SN74LS322J(N), SN74LS673J(N)

Использование триггеров с защёлками с тремя состояниями на выходе, увеличенная (по сравнению со стандартными микросхемами серии) нагрузочная способность позволяют использовать (в микропроцессорных системах с магистральной организацией) регистры непосредственно на магистраль в качестве регистров, буферных регистров, регистров ввода-вывода, магистрального передатчика и т. д. без дополнительных схем интерфейса.

Параллельные регистры[править | править исходный текст]

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, то есть цепи управления. Пример схемы статического регистра, построенного на триггерах типа D с прямыми динамическими входами, имеющего входы сброса и выходы с третьим состоянием, управляемые сигналом EZ.

Сдвигающие (последовательные) регистры[править | править исходный текст]

Последовательные (сдвигающие) регистры представляют собою цепочку разрядных схем, связанных цепями переноса. Основной режим работы — сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала. В однотактных регистрах со сдвигом на один разряд вправо слово сдвигается при поступлении синхросигнала. Вход и выход последовательные (англ. Data Serial Right, DSR).

Согласно требованиям синхронизации в сдвигающих регистрах, не имеющих логических элементов в межразрядных связях, нельзя применять одноступенчатые триггеры, управляемые уровнем, поскольку некоторые триггеры могут за время действия разрешающего уровня синхросигнала переключиться неоднократно, что недопустимо. Появление в межразрядных связях логических элементов, и тем более, логических схем неединичной глубины упрощает выполнение условий работоспособности регистров и расширяет спектр типов триггеров, пригодных для этих схем. Многотактные сдвигающие регистры управляются несколькими синхропоследовательностями. Из их числа наиболее известны двухтактные с основным и дополнительным регистрами, построенными на простых одноступенчатых триггерах, управляемых уровнем. По такту С1 содержимое основного регистра переписывается в дополнительный, а по такту С2 возвращается в основной, но уже в соседние разряды, что соответствует сдвигу слова. По затратам оборудования и быстродействию этот вариант близок к однотактному регистру с двухступенчатыми триггерами.

Примеры:

SN74ALS164 (КР1533ИР8) — восьмиразрядный сдвиговый регистр с последовательной загрузкой и параллельной выгрузкой. Оснащён двумя входами, A и B, что позволяет заперев один из них (установив на нём низкий уровень напряжения по положительному фронту тактового импульса), осуществлять ввод данных в последовательном коде по другому входу.

SN74ALS165 (КР1533ИР9), SN74ALS166 (КР1533ИР10) — восьмиразрядный сдвиговый регистр с последовательной выгрузкой, работающий в двух режимах: параллельной загрузки и сдвига,

SN74198 (КР1533ИР13) — восьмиразрядный реверсивный сдвиговый регистр, имеющий четыре режима работы: параллельная загрузка, сдвиг влево, сдвиг вправо и блокировка.

SN74LS295 (КР1533ИР16) — четырёхразрядный реверсивный сдвиговый регистр с тремя состояниями выходов, имеющий четыре режима работы: параллельная загрузка, сдвиг влево, сдвиг вправо и блокировка.

2. Система управления памятью в ЭВМ

В ЭВМ на основе 32-разрядного микропроцессора при работе в так называемом защищенном режиме, поддерживающем мультипрограммирование и обеспечивающем адресацию операндов в максимально возможном для данной архитектуры диапазоне до 232 байт, виртуальная память организуется на основе сегментно-страничного представления памяти. При этом память разбивается на сегменты переменной длины, выделяемые пользователю под размещение его программ и данных. Сегменты, в свою очередь, делятся на страницы фиксированной длины (4К = 212 байт), используемые системой управления памятью для ее виртуализации 4

Начало каждого сегмента устанавливается операционной системой через соответствующий сегментный регистр и скрыто от пользователя. Пользователь пишет свои программы в адресах относительно начала сегмента, полагая, что он располагает сегментом максимально возможной для данной архитектуры длины (232 байт). Аппаратные средства микропроцессора сначала проводят сегментное преобразование адреса, а затем - страничное.

Механизм формирования физического адреса при сегментно-страничной организации памяти показан на рис. 16.1

Формирование физического адреса при сегментно-страничной организация памяти в 32-разрядном микропроцессоре

Основой получения физического адреса, выдаваемого на адресную шину микропроцессора, служит логический адрес. Он состоит из двух частей: селектора, являющегося идентификатором сегмента, и смещения в сегменте.

Смещение в сегменте (32 разряда) (эффективный адрес) вычисляется по задаваемому в команде режиму адресации операнда и является виртуальным адресом операнда. При обращении к команде в качестве смещения выступает значение регистра-указателя команд.

Селектор размещается в сегментном регистре.Основная его часть представляет собой номер (INDEX), по которому в одной из специальных таблиц дескрипторов можно найти дескриптор (описатель) данного сегмента. Вид используемой таблицы определяется битом TI (table indicator) селектора. Селектор содержит также двухразрядное поле RPL, используемое при организации защиты памяти по привилегиям.

Дескриптор содержит сведения о сегменте. В одном из его полей содержится базовый адрес сегмента. В остальных полях записана дополнительная информация о сегменте: длина, допустимый уровень прав доступа к данному сегменту с целью защиты находящейся в нем информации, тип сегмента (сегмент кода, сегмент данных, специальный системный сегмент и т.д.) и некоторые другие атрибуты.

Сумма полученного из дескриптора базового адреса сегмента и вычисленного смещения дает линейный адрес операнда, который при включенном механизме страничного преобразования представляет собой номер виртуальной страницы (старшие 20 разрядов) и смещение операнда в странице (младшие 12 разрядов линейного адреса в соответствии с объемом страницы в 4 Кбайт).

При преобразовании номера виртуальной страницы в номер физической используются следующие системные объекты: каталог таблиц страниц (КТС) и таблицы страниц (ТС). Структуры этих таблиц сходны между собой.

Сначала по разрядам А31-А22 линейного адреса в КТС выбирается нужный элемент. Каталог таблиц страниц всегда присутствует в ОП и содержит указания по размещению таблицы страниц, относящейся к тому или иному процессу.

Элемент КТС содержит

адрес начала таблицы страниц,

бит присутствия (P) таблицы страниц в оперативной памяти,

бит разрешения чтения/записи (R/W),

бит защиты страницы (пользователь/супервизор (U/S)) и некоторые другие атрибуты.

После получения из выбранного элемента КТС начального адреса таблицы страниц происходит обращение к ТС. В выбранной таблице страниц находится элемент, номер которого определяется разрядами А21-А12 линейного адреса. Структура элемента таблицы страниц аналогична структуре элемента КТС. Элемент ТС в соответствующем поле содержит адрес начала требуемой физической страницы и другие атрибуты, аналогичные элементу КТС.

При P =0 возникает прерывание, необходимая страница подкачивается в ОП, ее адрес заносится в соответствующий элемент ТС, и команда выполняется повторно.

3. --------

Билет №6.

1.Регистр сдвига с линейной обратной связью (РСЛОС, англ. Linear feedback shift register, LFSR) — регистр сдвига битовых слов, у которого входной (вдвигаемый) бит является линейной функцией состояния остальных битов регистра до сдвига. Может быть организован как программными, так и аппаратными средствами и применяется для генерации псевдослучайных последовательностей битов, что находит применение, в частности, в криптографии.

В регистре сдвига с линейной обратной связью выделяют две части (модуля): собственно регистра сдвига и схемы (или подпрограммы) вычисляющих значение вдвигаемого бита. Регистр состоит из функциональных ячеек (или битов машинного слова или нескольких слов), в каждой из которой хранится текущее состояние одного бита. Количество ячеек ~L, называют длиной регистра. Биты (ячейки) обычно нумеруются числами ~0, 1, 2, \dots, L-1, каждая из которых способна хранить ~1 бит, причём в ячейку 0 происходит вдвижение вычисленного бита, а из ячейки ~L-1 извлекается выдвигаемый очередной сгенерированный бит. Вычисление вдвигаемого бита обычно производится до сдвига регистра, и только после сдвига значение вычисленного бита помещается в ячейку 0.

Периодом регистра сдвига называют минимальную длину получаемой последовательности до начала её повторения. Так как регистр из ~L битовых ячеек имеет только 2^{L}-1 разных ненулевых состояний, то, принципиально, период регистра не может превышать это число. Если период регистра равен этому числу, то такой регистр называют регистром максимального периода.

Для РСЛОС функция обратной связи является линейной булевой функцией от состояний всех или некоторых битов регистра. Например, сумма по модулю два или её логическая инверсия является линейной булевой функцией (операция XOR, в формулах обозначают как \oplus) и наиболее часто применяется в таких регистрах.

При этом те биты, которые являются переменными функции обратной связи, принято называть отводами.

Управление регистром в аппаратных реализациях производится подачей сдвигающего импульса (иначе называемого тактового или синхроимпульса) на все ячейки, в программных — выполнением программного цикла, включающего вычисление функции обратной связи и сдвига битов в слове.

В течение каждого такта времени выполняются следующие операции:

содержимое ячейки ~L-1 формирует очередной бит выходной последовательности битов;

новое содержимое ячейки ~0 определяется битом обратной связи, являющегося значением функции обратной связи (обычно сложение по модулю ~2) с определёнными коэффициентами (принимающими значение 0 и 1) битов ячеек ~0, 1, 2, \dots, L-1;

содержимое ~i-й ячейки перемещается в ячейку ~i+1 для любого ~i, 0<~ i<~ L-1;

содержимое 0-й ячейки принимает значение вычисленного бита.

2.Преобразование логического адреса в физический при сегментно-страничной организации памяти требует, как минимум, трех обращений к системным таблицам, расположенным в оперативной памяти (таблице дескрипторов, КТС и ТС). Это может привести к существенному снижению производительности компьютера. Механизм сокращения потерь времени на такое преобразование основывается на том факте, что изменение состояния сегментных регистров производится относительно редко, например, при переключении ЭВМ на новую задачу, а новое страничное преобразование требуется лишь при выходе программы за пределы загруженной в оперативную память страницы.

При сегментном преобразовании адреса после первого считывания дескриптора из таблицы дескрипторов, расположенной в оперативной памяти (например, после изменения состояния сегментного регистра при переключении на новую задачу), он запоминается в программно-недоступных ("теневых") регистрах микропроцессора (рис. 16.4). При последующих обращениях к данному сегменту используется дескриптор из "теневого" регистра без обращения к ОП. Поэтому на его вызов требуется минимальное время. Так как состояние сегментных регистров меняется относительно редко, то такой подход приводит к значительной экономии времени при сегментном преобразовании адреса.

При страничном преобразовании номера виртуальной страницы в номер физической страницы используется кэш-буфер ассоциативной трансляции (TLB), содержащий физические адреса 32-х наиболее активно используемых страниц (рис. 16.5) и расположенный непосредственно в микропроцессоре.

Номер виртуальной страницы представляет собой старшие 20 разрядов линейного адреса, полученного при сегментном преобразовании (А31 - А12). По младшим разрядам (А14 - А12) этого номера выбирается блок в буфере ассоциативной трансляции. Содержимое поля тэгов каждой из четырех строк этого блока ассоциативным образом (одновременно) сравнивается с разрядами (А31 - А15) линейного адреса. Если значения для одной из строк выбранного блока совпали, значит, номер этой виртуальной страницы уже преобразовывался в номер физической страницы и результат этого преобразования находится в найденной строке TLB. Если сравнение не было успешным, то преобразование номера виртуальной страницы в номер физической проходит обычным образом через обращения к каталогу таблиц страниц и к таблице страниц, а полученное значение заносится в TLB. При этом в поле тэгов заносятся старшие 17 разрядов линейного адреса этой страницы (A31-A15). Если нет свободной строки в блоке, определяемом разрядами А14 - А12 линейного адреса, то из блока вытесняется строка, информация в которой дольше всего не использовалась (механизм LRU).

3. -----------

Билет №7.

1.Арифме́тико-логи́ческое устро́йство (АЛУ) (англ. arithmetic and logic unit, ALU) — блок процессора, который под управлением устройства управления (УУ) служит для выполнения арифметических и логических преобразований (начиная от элементарных) над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером машинного слова.

Организация и принципы действия

Одноразрядное двоичное бинарное (двухоперандное) АЛУ с бинарным (двухразрядным) выходом может выполнять до 2^{(2^2)*2}=2^8=256 двоичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом.

Одноразрядное троичное бинарное (двухоперандное) АЛУ с унарным (одноразрядным) выходом (полуАЛУ) может выполнять до 3^{(3^2)}=3^9=19\ 683 троичных бинарных (двухоперандных) функций (операций) с унарным (одноразрядным) выходом.

Одноразрядное троичное бинарное (двухоперандное) АЛУ с бинарным (двухразрядным) выходом может выполнять до 3^{(3^2)*2}=3^{18}=387\ 420\ 489 троичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом.

Арифметико-логическое устройство в зависимости от выполнения функций можно разделить на две части:

микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

операционное устройство, в котором реализуется заданная последовательность микрокоманд (команд).

В состав арифметико-логического устройства, условно, для примера на картинке, включается регистры Рг1 — Рг7, которые служат для обработки информации, поступающей из оперативной или пассивной памяти N1, N2, …NS и логические схемы, которые используются для обработки слов по микрокомандам, поступающим из устройства управления. Различают два вида микрокоманд: внешние — такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нём преобразование информации (на рисунке 2 это микрокоманды А1,А2,…,Аn) и внутренние — те, которые генерируются в АЛУ и оказывают влияние на микропрограммное устройство, изменяя таким образом нормальный порядок следования команд. р1, p2,…, pm на рисунке 2 — это и есть микрокоманды. А результаты вычислений из АЛУ передаются в ОЗУ по кодовым шинам записи у1, у2, …, ys.

Функции регистров, входящих в арифметико-логическое устройство

Рг1 — аккумулятор (или аккумуляторы) — главный регистр АЛУ, в котором образуется результат вычислений;

Рг2,Рг3 — регистры операндов (слагаемого/сомножителя/делителя/делимого и др.) в зависимости от выполняемой операции;

Рг4 — регистр адреса (или адресные регистры), предназначенные для запоминания (бывает что формирования) адреса операндов результата;

Рг6 — k индексных регистров, содержимое которых используется для формирования адресов;

Рг7 — l вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров могут быть адресованы в команде для выполнения операций с их содержимым и их называют программно-доступными. К таким регистрам относятся: сумматор, индексные регистры и некоторые вспомогательные регистры. Остальные регистры нельзя адресовать в программе, то есть они являются программно-недоступными.

Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу её обработки и по логической структуре. Более подробная классификация указана на рис.3.

Такая сложная логическая структура АЛУ может характеризоваться количеством отличающихся друг от друга микроопераций, которые необходимы для выполнения всего комплекса задач, поставленных перед арифметико-логическим устройством. На входе каждого регистра собраны соответствующие логические схемы, обеспечивающие такие связи между регистрами, что позволяет реализовать заданные микрооперации. Выполнение операций над словами сводится к выполнению определённых микроопераций, которые сводятся в свою очередь … управляют передачей слов в АЛУ и действиями по преобразованию слов. Порядок выполнения микрокоманд определяется алгоритмом выполнения операций. То есть, связи между регистрами АЛУ и их функциями зависят в основном от принятой методики выполнения логических операций, в том числе арифметических или специальной арифметики.

Операции в АЛУ

Все выполняемые в АЛУ операции являются логическими операциями (функциями), которые можно разделить на следующие группы:

операции двоичной арифметики для чисел с фиксированной точкой;

операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

операции десятичной арифметики;

операции индексной арифметики (при модификации адресов команд);

операции специальной арифметики;

операции над логическими кодами (логические операции);

операции над алфавитно-цифровыми полями.

Современные ЭВМ общего назначения обычно реализуют операции всех приведённых выше групп, а малые и микроЭВМ, микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами.

К арифметическим операциям относятся сложение, вычитание, вычитание модулей («короткие операции») и умножение и деление («длинные операции»).

2.При мультипрограммном режиме работы ЭВМ в ее памяти одновременно могут находиться несколько независимых программ. Поэтому необходимы специальные меры по предотвращению или ограничению обращений одной программы к областям памяти, используемым другими программами. Программы могут также содержать ошибки, которые, если этому не воспрепятствовать, приводят к искажению информации, принадлежащей другим программам. Последствия таких ошибок особенно опасны, если разрушению подвергнутся программы операционной системы. Другими словами, надо исключить воздействие программы пользователя на работу программ других пользователей и программ операционной системы. Следует защищать и сами программы от находящихся в них возможных ошибок.

Таким образом, средства защиты памяти должны предотвращать 2

неразрешенное взаимодействие пользователей друг с другом,

несанкционированный доступ пользователей к данным,

повреждение программ и данных из-за ошибок в программах,

намеренные попытки разрушить целостность системы,

использование информации в памяти не в соответствии с ее функциональным назначением.

Чтобы воспрепятствовать разрушению одних программ другими, достаточно защитить область памяти данной программы от попыток записи в нее со стороны других программ, а в некоторых случаях и своей программы (защита от записи), при этом допускается обращение других программ к этой области памяти для считывания данных.

В других случаях, например при ограничениях на доступ к информации, хранящейся в системе, необходимо запрещать другим программам любое обращение к некоторой области памяти как на запись, так и на считывание. Такая защита от записи и считывания помогает в отладке программы, при этом осуществляется контроль каждого случая обращения за область памяти своей программы.

Для облегчения отладки программ желательно выявлять и такие характерные ошибки в программах, как попытки использования данных вместо команд или команд вместо данных в собственной программе, хотя эти ошибки могут и не разрушать информацию (несоответствие функционального использования информации).

Если нарушается защита памяти, исполнение программы приостанавливается и вырабатывается запрос прерывания по нарушению защиты памяти.

Защита от вторжения программ в чужие области памяти может быть организована различными методами. Но при любом подходе реализация защиты не должна заметно снижать производительность компьютера и требовать слишком больших аппаратурных затрат.

Методы защиты базируются на некоторых классических подходах, которые получили свое развитие в архитектуре современных ЭВМ. К таким методам можно отнести защиту отдельных ячеек, метод граничных регистров, метод ключей защиты.

Защита отдельных ячеек памяти организуется в ЭВМ, предназначенных для работы в системах управления, где необходимо обеспечить возможность отладки новых программ без нарушения функционирования находящихся в памяти рабочих программ, управляющих технологическим процессом. Это может быть достигнуто выделением в каждой ячейке памяти специального "разряда защиты". Установка этого разряда в "1" запрещает производить запись в данную ячейку, что обеспечивает сохранение рабочих программ. Недостаток такого подхода - большая избыточность в кодировании информации из-за излишне мелкого уровня защищаемого объекта (ячейка).

В системах с мультипрограммной обработкой целесообразно организовывать защиту на уровне блоков памяти, выделяемых программам, а не отдельных ячеек.

Метод граничных регистров (рис. 17.1) заключается во введении двух граничных регистров, указывающих верхнюю и нижнюю границы области памяти, куда программа имеет право доступа.

При каждом обращении к памяти проверяется, находится ли используемый адрес в установленных границах. При выходе за границы обращение к памяти не производится, а формируется запрос прерывания, передающий управление операционной системе. Содержание граничных регистров устанавливается операционной системой при загрузке программы в память.

Модификация этого метода заключается в том, что один регистр используется для указания адреса начала защищаемой области, а другой содержит длину этой области.

Метод граничных регистров, обладая несомненной простотой реализации, имеет и определенные недостатки. Основным из них является то, что этот метод поддерживает работу лишь с непрерывными областями памяти.

Метод ключей защиты, в отличие от предыдущего, позволяет реализовать доступ программы к областям памяти, организованным в виде отдельных модулей, не представляющих собой единый массив.

Память в логическом отношении делится на одинаковые блоки, например, страницы. Каждому блоку памяти ставится в соответствие код, называемый ключом защиты памяти, а каждой программе, принимающей участие в мультипрограммной обработке, присваивается код ключа программы. Доступ программы к данному блоку памяти для чтения и записи разрешен, если ключи совпадают (то есть данный блок памяти относится к данной программе) или один из них имеет код 0 (код 0 присваивается программам операционной системы и блокам памяти, к которым имеют доступ все программы: общие данные, совместно используемые подпрограммы и т. п.). Коды ключей защиты блоков памяти и ключей программ устанавливаются операционной системой.

В ключе защиты памяти предусматривается дополнительный разряд режима защиты. Защита действует только при попытке записи в блок, если в этом разряде стоит 0, и при любом обращении к блоку, если стоит 1. Коды ключей защиты памяти хранятся в специальной памяти ключей защиты, более быстродействующей, чем оперативная память.

При обращении к памяти группа старших разрядов адреса ОЗУ, соответствующая номеру блока, к которому производится обращение, используется как адрес для выборки из памяти ключей защиты кода ключа защиты, присвоенного операционной системой данному блоку. Схема анализа сравнивает ключ защиты блока памяти и ключ программы, находящийся в регистре слова состояния программы (ССП), и вырабатывает сигнал "Обращение разрешено" или сигнал "Прерывание по защите памяти". При этом учитываются значения режима обращения к ОЗУ (запись или считывание), указываемого триггером режима обращения ТгРО, и режима защиты, установленного в разряде режима обращения (РРО) ключа защиты памяти.

3.--------

Билет №8.

1. Схемное устройство управления

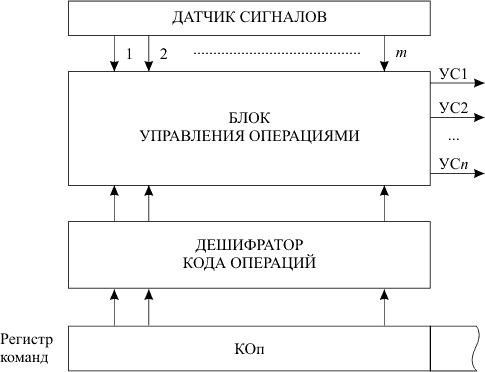

Устройство управления схемного типа состоит из:

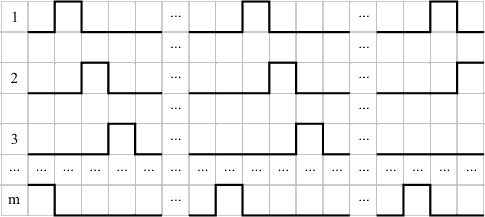

датчика сигналов, вырабатывающего последовательность импульсов, равномерно распределенную во времени по своим шинам (рис. 4.2) (n - общее количество управляющих сигналов, необходимых для выполнения любой операции; m - количество тактов, за которое выполняется самая длинная операция);

блока управления операциями, осуществляющего выработку управляющих сигналов, то есть коммутацию сигналов, поступающих с ДС, в соответствующем такте на нужную управляющую шину;

дешифратора кода операций, который дешифрирует код операции команды, присутствующей в данный момент в регистре команд, и возбуждает одну шину, соответствующую данной операции; этот сигнал используется блоком управления операциями для выработки нужной последовательности управляющих сигналов.

2. Защита памяти

Защита информации хранящейся в памяти, от несанкционированного использования.

Уровни защиты = уровням привилегий – PL (0…3).

Intel: 0 – высший, 3 – низший.

0) ядро ОС программа инициализирующая работу, программа управляющая доступом к памяти, программы защиты памяти и др.,

1) утилиты ОС, основная часть программ операционной системы,

2) уровень служебных программ драйверы внешних устройств, система управления базами данных, подсистема программ разного назначения и др.,

3) программы пользователей или прикладные программы

3.4.1Взаимодействие между уровнями определяется правилами:

Данные из сегмента уровня PL могут быть выбраны программой с уровнем PL и выше.

Сегмент программы с уровнем PL могут быть вызваны программами с уровнем PL и ниже.

Введем обозначения:

DPL – уровень привилегий в дескрипторе,

СPL – уровень привилегий текущей программы (устанавливается в разрядах 0 и 1 сегмента CS, относящегося к IP),

RPL – уровень привилегий сегмента- источника запроса (разряды 0 и 1 источника запроса).

Реализация правил зависит от типа сегмента, к которому обращаются.

Обращение к сегменту данных

DPL ≥ max (CPL, RPL).

Установкой значения RPL можно управлять доступом текущей программы к сегментам, имеющим различные PL. Если правило не выполняется, то вызывается int 13 (прерывание, связанное с защитой памяти).

Обращение к стеку

DPL = CPL = RPL, к стеку можно обращаться только на своём уровне.

R/W = 1, т.е. запись разрешена, иначе int 13.

Обращение к сегменту программ

Проблемы могут возникнуть, если существуют переходы к другим сегментам:

– безусловный переход JMP,

– обращение к подпрограммам и возврат CALL(RET),

– прерывания INT(IRET).

Примечание. Условный переход может выполняться только в пределах одного сегмента.

Все зависит от С-бита подчиненности (он в поле атрибутов дескриптора, связанного с CS). C = 1, подчиненный сегмент; С = 0, неподчиненный.

а) Рассмотрим случай С=1.

Обращение к подчиненному сегменту для команд JMP и CALL идет по правилу №2. (при условии DPL≤ CPL); CPL – уровень привилегий текущей программы; DPL – сегмента, к которому обращаемся.

Особенности: при обращении к более высоким уровням значение CPL сохраняется из прерываемой программы.

б) Рассмотрим случай С = 0.

DPL= CPL (команды JMP и CALL).

Но можно переходить также и вверх с помощью спец. точек входа в другие программы (шлюзов). Это значит, что вызваны могут быть не любые, а только некоторые сегменты с более высоким уровнем привилегий.

Каждой JMP/CALL выбирается шлюз из LTD, следующего формата:

Селектор Относительный адрес Атрибуты

По селектору из GDT выбирается дескриптор сегмента, к которому идет обращение и в нем базовый адрес. Относительный адрес загружается в счетчик команд (EIP или 16-ти разрядный IP)

Параллельно запоминаются параметры для возврата. При этом учитываются атрибуты:

Р – бит присутствие в ВМ,

DPL – уровень привилегий,

T – тип процессора (i286, i486),

WC – 5 бит, в которых указывается количество 16/32 – разрядных слов, которые должны быть переданы в стек нового уровня (от 0 до 31), поскольку при переходе на более высокий уровень создается свой стек!

При возврате происходят обратные действия.

Замечание 1. Если выполняется команда CALL, нужно запомнить определенную информацию в стеке нового уровня.

Замечание 2. Та программа, из которой делается переход, может быть названа текущая, данная, прерываемая (если речь идёт о прерывании) и т.д. Для определённости будем применять термин старая.

Та программа, к которой мы переходим, может быть названа новая, прерывающая и т.д. Мы будем использовать термин новая.

3.4.2 Особенности выполнения команды перехода JMP

При переходе по JMP надо знать:

1) куда идет переход:

а) Переход в пределах сегмента – ближний переход.

б) Переход в другой сегмент – дальний переход.

2) как формируется адрес перехода:

Ближний переход:

– Относительный переход. Указывается смещение относительно текущего значения счетчика команд EIP или IP: d8 – короткий; d16, d32 – длинный. Время – 3 такта.

– Косвенный переход. В счетчик команд загружается либо содержимое регистра, либо содержимое ячейки памяти в зависимости от кода поля конца строки MOD R/M команды. Время – 5 тактов.

Дальний переход.

При переходе надо знать не только смещение, но и информацию о сегменте, которая должна быть загружена в CS.

– Прямой переход – вся информация указывается в коде команды

(19 тактов).

– Косвенный переход – указывается адрес ячейки памяти, в которой содержится информация о счетчике, а в следующей ячейке – информация о селекторе (18 тактов).

Команды условного перехода выполняются только для переходов в том же сегменте.

3.4.3 Особенности выполнения команды перехода CALL

CALL выполняется аналогично JMP, но поскольку необходим возврат, то делается запоминание места перехода. Время на выполнение CALL существенно увеличивается: CALL – дальний переход 70 тактов. Возврат ~ 35 тактов.

Выполнение прерываний INT аналогично выполнению CALL.

Команды межсегментного перехода JMP, CALL, INT к другим сегментам могут выполняться как межзадачные переходы – 180-200 тактов.

3.5 Многозадачность

Многозадачность – возможность процессора выполнять несколько задач одновременно. Программы и данные этих задач должны быть в ВМ. При этом должна быть обеспечена защита информации от несанкционированного использования.

Для реализации многозадачного режима в процессоре предусмотрены аппаратные и программные средства.

Аппаратные средства (регистр задачи, дескриптор, соответствующий этой задаче) должны обеспечивать легкий переход между выполняемыми задачами.

Программные средства предусматривают специальную структуру данных – сегмент состояния задачи – TSS. Он оформляется как обычный программный сегмент => должен иметь селектор и дескриптор (см. «Системные регистры» в подразделе 3.2). Дескрипторы TSS хранятся в GDT и выбираются оттуда по коду селектора, хранящегося в TR (регистр задач)

Aтрибуты:

- G – бит дробности (байты или 4Кбайта),

- P – присутствие (есть в ВМ или нет),

- DPL – уровень привилегий (2 бита),

- M – тип процессора (i286 или i486),

- B – бит занятости (0 – если задача не решалась, 1 – при переключении на эту задачу).

Содержимое TSS.

Общая информация, хранящаяся в TSS, может быть разделена на обязательную и дополнительную информацию.

Обязательная информация:

Содержимое TR предыдущей задачи (из которой был сделан переход) на случай возможного возврата.

Содержимое регистров сегментов (6 регистров по 16 разрядов),

Содержимое РОН 8х32,

СодержимоеEIP, EFlags 2 x 32,

Селектор LDT,

Содержимое регистра CR3,

Содержимое сегментных регистров стеков SS0, SS1, SS2 (стеков более высокого уровня),

Относительные адреса вершин стеков SP0, SP1, SP2.

Начальный базовый адрес битовой карты ввода-вывода,

Бит ловушка Т. При Т = 1 вызывается прерывание типа 1. Используется при отладке программы (пошаговый режим).

Дополнительная информация:

Информация для ОС: имя задачи, комментарии и т.п.

Битовая карта ввода-вывода (БКВВ). Её вид: 10110001… Биты по порядку соответствуют номерам (N) ВУ (0 - доступно; 1 - не доступно), длина может быть до 64 кбайт (216). Если битовая карта вылезает за пределы сегмента (D), то лишняя часть карты отбрасывается.

11111111 – признак конца

Обращение к TSS происходит при загрузке регистра TR селектора той задачи, которая будет выполняться.

3.

54 = 110110

28 = 11100

76 = 1001100

55 = 110111

12 = 1100

43 = 101011

86 = 1010110

124 = 1111100

255 = 11111111

244 = 11110100

Билет намба ван на руси (то есть 9)

(Задание намба ван на билете) Р еализация датчика сигналов на основе счетчика с дешифратором представлена на рисунке. По заднему фронту каждого тактового импульса, поступающего на устройство управления с системного генератора импульсов, счетчик увеличивает свое состояние

(Задание намба ту на билете)

1) с использованием простого пароля;

2) в диалоговом режиме с использованием нескольких паролей и/или персональной информации пользователей;

3) по индивидуальным особенностям и физиологическим характеристикам человека (отпечатки пальцев, геометрия руки, голос, персональная роспись, структура сетчатки глаза, фотография и некоторые другие);

4) с использованием радиокодовых устройств;

5) с использованием электронных карточек.

(Задание намба фри на билете)

110111 - 55

1011011 - 91

1010 - 10

10110010 - 178

111010 - 58

111 - 7

11111111 - 255

101100101 - 357

Билет намба ту на руси (то есть 10)

(Задание намба ван на билете) Проектирование датчика сигналов на сдвиговом регистре требует лишь его "закольцовывания", то есть соединения выхода последнего разряда с входом, через который в регистр заносится информация при сдвиге, и первоначальной установки (рисунок). В начальном состоянии регистр содержит "1" только в разряде 0. Входы параллельной загрузки регистра для его начальной установки и соответствующий этой операции управляющий вход регистра на схеме не показаны.

(Задание намба ту на билете) (Вопрос говно, поэтому я напишу устройства ввода-вывода информации.)

Дисплей, клавиатура, мышь, трекбол (не ебу что это), сканеры, джойстик, руль, принтер, плоттер.

(Задание намба фри на билете) (Писать так же как тут)

478

239 - 1

119 - 1

59 - 1

30 - 0

15 - 1

7 - 1

3 - 1

1 - 1

0 - 0

509

255 - 1

127 - 1

63 - 1

31 - 1

15 - 1

7 - 1

3 - 1

2 - 0

1 - 1

Билет намба фри на руси (то есть 11)

(Задание намба ван на билете)

М икропрограммное устройство управления представлено на рис. 4.7. Преобразователь адреса микрокоманды преобразует код операции команды, присутствующей в данный момент в регистре команд, в начальный адрес микропрограммы, реализующей данную операцию, а также определяет адрес следующей микрокоманды выполняемой микропрограммы по значению адресной части текущей микрокоманды.

(Задание намба ту на билете)

Интерфе́йс (англ. Interface — сопряжение, поверхность раздела, перегородка) — совокупность возможностей, способов и методов взаимодействия двух систем (любых, а не обязательно являющиеся вычислительными или информационными), устройств или программ для обмена информацией между ними, определённая их характеристиками, характеристиками соединения, сигналов обмена и т. п. В случае, если одна из взаимодействующих систем — человек, чаще говорят лишь о второй системе, то есть об интерфейсе той системы, с которой человек взаимодействует.

(Задание намба фри на билете)

Там короче расчет на листке должен быть расчет

Билет намба фор на руси (то есть 12)

(Задание намба ван на билете)

По форме записанной информации:

· аналоговые;

· цифровые.

По устойчивости записи и возможности перезаписи:

· Постоянные (ПЗУ), содержание которых не может быть изменено конечным пользователем (например, BIOS). ПЗУ в рабочем режиме допускает только считывание информации.

· Записываемые (ППЗУ), в которые конечный пользователь может записать информацию только один раз (например, CD-R).

· Многократно перезаписываемые (ПППЗУ) (например, CD-RW).

· Оперативные (ОЗУ) — обеспечивают режим записи, хранения и считывания информации в процессе её обработки. Быстрые, но дорогие ОЗУ (SRAM) строят на триггерах, более медленные, но более дешёвые разновидности ОЗУ — динамические ЗУ (DRAM) строят на элементах состоящих из ёмкости (конденсатора) и полевого транзистора, используемого в качестве ключа разрешения записи-чтения. В обоих видах ЗУ информация исчезает после отключения от источника питания (например, тока).

По энергозависимости:

· энергонезависимые, записи в которых не стираются при снятии электропитания;

· энергозависимые, записи в которых стираются при снятии электропитания;

· статические, которым для хранения информации достаточно сохранения питающего напряжения;

· динамические, в которых информация со временем разрушается (деградирует), и, кроме подачи электропитания, необходимо производить её периодическое восстановление (регенерацию).

По типу доступа:

· С последовательным доступом (например, магнитные ленты).

· С произвольным доступом (RAM; например, оперативная память).

· С прямым доступом (например, жёсткие диски).

· С ассоциативным доступом (специальные устройства, для повышения производительности баз данных).

По геометрическому исполнению:

· дисковые (магнитные диски, оптические, магнитооптические);

· ленточные (магнитные ленты, перфоленты);

· барабанные (магнитные барабаны);

· карточные (магнитные карты, перфокарты, флэш-карты, и др.);

· печатные платы (карты DRAM, картриджи).

По физическому принципу:

· перфорационные (с отверстиями или вырезами)

· перфокарта

· перфолента

· с магнитной записью

· магнитные сердечники (пластины, стержни, кольца, биаксы)

· магнитные диски

· Жёсткий магнитный диск

· Гибкий магнитный диск

· магнитные ленты

· магнитные карты

· оптические

· CD

· DVD

· HD-DVD

· Blu-ray Disc

· магнитооптические:

· CD-MO

· использующие накопление электростатического заряда в диэлектриках (конденсаторные ЗУ, запоминающие электроннолучевые трубки);

· использующие эффекты в полупроводниках (EEPROM, флэш-память)

· звуковые и ультразвуковые (линии задержки);

· использующие сверхпроводимость (криогенные элементы);

· другие.

По количеству устойчивых (распознаваемых) состояний одного элемента памяти:

· двоичные

· троичные

· десятичные

(Задание намба ту на билете)

Программно-управляемая передача данных осуществляется при непосредственном участии и под управлением процессора, который при этом выполняет специальную подпрограмму ввода-вывода. Данные между памятью и периферийным устройством пересылаются через процессор. Операция ввода-вывода инициируется текущей командой программы или запросом прерывания от периферийного устройства.

(Задание намба фри на билете)

Представим числа 1710 и -2510 в обратном коде.

Представим число 17 в двоичном коде.

17 = 100012

Обратный код для положительного числа совпадает с прямым кодом. Для отрицательного числа все цифры числа заменяются на противоположные (1 на 0, 0 на 1), а в знаковый разряд заносится единица.

Двоичное число 10001 имеет обратный код 0,10001

Представим число -25 в двоичном коде.

25 = 110012

Двоичное число 11001 имеет обратный код 1,00110

Сложим числа 010001 и 100110

В итоге получаем:

| 5 | 4 | 3 | 2 | 1 | 0 |

Результат сложения: 110111

В старшем бите 1. Следовательно, в результате сложения получили отрицательное число. Переведем его обратно в прямой код. Для этого найдем обратный код (инвертируем все биты, кроме знакового): 01000

Получили число 01000. В десятичном представлении это число имеет вид:

Для перевода необходимо умножить разряд числа на соответствующую ему степень разряда.

01000 = 24*0 + 23*1 + 22*0 + 21*0 + 20*0 = 0 + 8 + 0 + 0 + 0 = 8

Результат сложения (в десятичном представлении): -8

Билет 13

Вопрос 1

В ЗУ с произвольным доступом (RAM - random access memory) время доступа не зависит от места расположения участка памяти (например, ОЗУ).

В ЗУ с прямым (циклическим) доступом благодаря непрерывному вращению носителя информации (например, магнитный диск - МД) возможность обращения к некоторому участку носителя циклически повторяется. Время доступа здесь зависит от взаимного расположения этого участка и головок чтения/записи и во многом определяется скоростью вращения носителя.

В ЗУ с последовательным доступом производится последовательный просмотр участков носителя информации, пока нужный участок не займет некоторое нужное положение напротив головок чтения/записи (например, магнитные ленты - МЛ).

Вопрос 2

Унарной операцией или одноместной операцией на множестве  называется отображение множества в себя

называется отображение множества в себя  , которое каждому элементу множества

, которое каждому элементу множества  , называемому операндом, ставит в соответствие некоторый элемент того же множества, называемый результатом.

, называемому операндом, ставит в соответствие некоторый элемент того же множества, называемый результатом.

Унарную операцию принято обозначать знаком действия, который ставится перед или над операндом. Например, для унарной операции «–» результат её применения к элементу  записывается в виде

записывается в виде  .

.

Унарная операция, обратная самой себе, называется инволюцией.

Простыми словами: Унарная операция — это операция над одним операндом (побитовое отрицание, унарный минус — меняет знак числа).

Двоичные логические операции с цифровыми сигналами (битовые операции)

Date: 2015-09-05; view: 970; Нарушение авторских прав