Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Интерфейс I2C

|

|

Используются две линии:

SDA - данные

SCL – синхронизация.

Передатчик должен быть сделан с открытым коллектором (стоком).

Устройство может являться и приемником и передачиком. Допускается неограниченное количество вудущих и ведомых.

Интерфейс полностью асинхронный.

1. 1 ведущий 1 ведомый

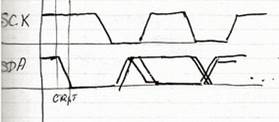

Данные можно менять, только если SCK в нуле. Исходное состояние шин в 1.

Синхронизацию задает ведущее устройство, но ведомое, если оно не имеет достаточного быстродействия, может замедлять обмен данными.

Начало любой передачи — условие Start — инициируется ведущим устройством, убедившимся в том, что шина свободна (высокий уровень сигналов SCL и SDA). Условие Start (на диаграммах обозначается как S)— перевод сигнала SDA из высокого в низкий при высоком уровне SCL Завершается операция переводом сигнала SDA из низкого уровня в высокий при высоком уровне SCL — условие Stop (обозначается как Р), также вводящееся ведущим устройством. При передаче данных состояние линии SDA может изменяться только при низком уровне SCL, биты данных считаются действительными во время высокого уровня SCL Ведущее устройство может начать очередную передачу вслед за текущей, не вводя условие

Каждая посылка данных состоит из 8 бит данных, формируемых передатчиком (старший бит — MSB — передается первым), после чего передатчик на один такт освобождает линию данных для получения подтверждения. Приемник во время девятого такта формирует бит подтверждения Ac k, по которому передатчик убеждается, что его «услышали». После передачи бита подтверждения ведомое устройство может задержать следующую посылку, удерживая линию SCL на низком уровне. 9 бит всегда в 0 – это обратня связь. 9 бит устанавливает пассивное устройство (это его ответ, что пассивное устройство есть, оно приняло данные и данные правильные). Если 9 = 0 и SCL = 1 – конец передачи – шина свободна

Работа начинается со сброса SDA при высоком SCK.

Если SCK =0, а приемник хочет подождать, он выставляет на шине 1 – ПРД передать не может – достигается асинхронность.

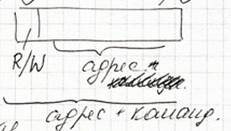

В I2C существует 2 фазы

1. адресация + команда

2. передача

Активное устройство перед данными передает байт адреса.

Этот байт принимается всеми устройствами и только то устройство Z.

Сейчас используется 2 байта на команду и адрес.

Т.к устройства медленные может случится так что несколько усьройств могут заработать одновременно. Устройства выставляют свои данные и сразу проверяют линию, если новое значение не прижилось – оно думает что это асинхронная задержка, кроме случая, когда задержка очень длинная – коллизия.. Устройства управляют линиями SCL и SDA и наблюдают за ними. Если устройство, передающее единицу (высокий уровень), в данном такте на линии SDA видит ноль (низкий уровень), оно должно признать свой проигрыш в конфликте и освободить линии SCL и SDA (при этом ему позволительно управлять линией SCL до конца передачи текущего байта). Если ведущее устройство, проигравшее в конфликте, имеет и функции ведомого устройства, по признанию проигрыша оно должно перейти в режим ведомого, поскольку конфликт мог быть вызван и попыткой обращения к нему победившего ведущего устройства.

Каждое ведомое устройство имеет свой адрес, уникальный на шине. В начале любой передачи ведущее устройство после условия S или S г посылает адрес ведомого устройства или специальный адрес (табл. 11.1). Ведомое устройство, опознавшее свой адрес после условия Start, становится выбранным; оно обязано ответить подтверждением на адрес и последующие сигналы со стороны ведущего устройства, до получения условия Р или 5г. В первоначальном варианте интерфейса разрядность адреса устройства составляла 7 бит, впоследствии был введен и режим 10-битной адресации, совместимый с 7-битной. На одной шине могут присутствовать устройства и с 7-битной, и 10-битной адресацией.

При 7-битной адресации в первом байте после S (Sr) ведущее устройство передает 7 бит адреса (А[6:0] в битах [7:1]) и признак операции RW (в бите О RW=1 — чтение, RW=0 — запись).

Date: 2015-07-27; view: 538; Нарушение авторских прав