Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Двунаправленный байтный режим

|

|

В этом режиме данные принимаются с использованием двунаправленного порта, у которого выходной буфер данных может отключаться установкой бита CR.

1. Хост сигнализирует о готовности приема данных установкой низкого уровня

на линии HostBusy.

2. ПУ в ответ помещает байт данных на линии Data [0:7].

3. ПУ сигнализирует о действительности байта установкой низкого уровня на

линии PtrClk.

4. Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой байта.

5. ПУ отвечает установкой высокого уровня на линии PtrClk,

6. Хост подтверждает прием байта импульсом HostClk.

Побайтный режим позволяет поднять скорость обратного канала до скорости прямого канала в стандартном режиме. Однако он способен работать только на двунаправленных портах, которые раньше применялись в основном на малораспространенных машинах PS/2, но практически все современные порты можно сконфигурировать на двунаправленный режим

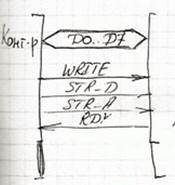

EPP

Параллельный. Протокол ЕРР обеспечивает четыре типа циклов обмена:

♦ запись данных;

♦ чтение данных;

♦ запись адреса;

♦ чтение адреса.

Шина данных двунаправленная.

WRITE – направление передачи. Низкий уровень — цикл записи, высокий — цикл чтения

STR_D – строб данных. Строб данных. Низкий уровень устанавливается в циклах передачи данных

STR_A – Строб адреса. Низкий уровень устанавливается в адресных циклах

RDY –

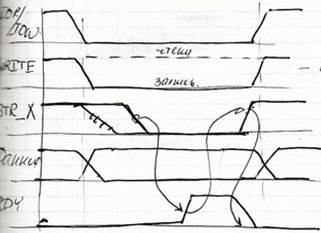

Процедура обмена (во время цикла ввода или вывода)

IOW и IOR - это линии, представляющие чтение и запись портов ввода-вывода

Вся процедура должна укладываться в цикл Ior/iow.

Если устройство тормозит, т.е. RDY долго не идет – существует специальный сигнал ISA (IO/RDY), который задает длительность IOR/IOW, но контроллер ЕРР имеет встроенный таймер для контроля вечного ожидания (более 15 мкс) – после этот контроллер сбрасывает весь процесс + состояние время 0.

Существует три регистра (D,S,..)

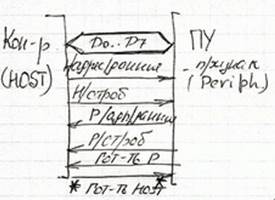

ECP

Основное отличие: оба устройства могут быть активными, т.е. управлять процессом.

Протокол ЕСР в обоих направлениях обеспечивает два типа циклов:

циклы записи и чтения данных;

командные циклы записи и чтения.

Передача двунаправленная. Существует FIFO (первый зашел первый вышел).

В контроллере описана процедура сжатия данных.

Информация делиться на:

- данные

- команды.

Устройство имеет два регистра на запись и на чтение.

1. данные записываются в HOST FIFO

2. цикл обмена (запись в Р)

Отличие цикла ЕСР от ЕРР, что в ЕСР длительность цикла ни к чему не привязана, а в ЕСР все идет быстрее.

Также присутсвует таймер. При таком возникновении вся ситуация сохраняется в устройстве и потом передается в HOST.

В обоих интерфейсах существует возможность адресоваться к большому числу ПУ.

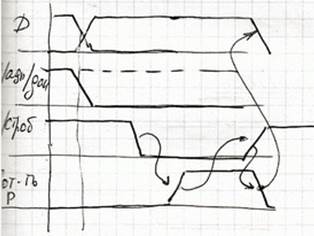

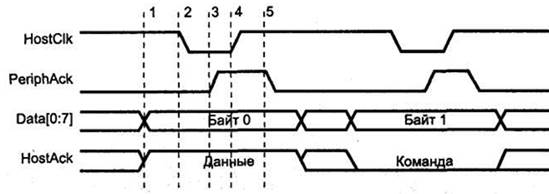

диаграмма двух циклов прямой передачи: за циклом данных следует командный цикл

Тип цикла задается уровнем на линии HostAck: в цикле данных — высокий, в командном цикле — низкий. В командном цикле байт может содержать канальный адрес или счетчик RLE. Отличительным признаком является бит 7 (старший): если он нулевой, то биты 0-6 содержат счетчик RLE (0-127), если единичный — то канальный адрес.

Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

Хост помещает данные на шину канала и устанавливает признак цикла дан

ных (высокий уровень) или команды (низкий уровень) на линии HostAck.

Хост устанавливает низкий уровень на линии HostClk, указывая на действи

тельность данных.

ПУ отвечает установкой высокого уровня на линии PeriphAck.

Хост устанавливает высокий уровень линии HostClk, и этот перепад может использоваться для фиксации данных в ПУ.

ПУ устанавливает низкий уровень на линии PeriphAck для указания на готовность к приему следующего байта.

Данные считаются переданными на шаге 4, когда линия HostClk переходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт.

Date: 2015-07-27; view: 484; Нарушение авторских прав