Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Шина QP

|

|

Выход платформы Nehalem — LGA1156 — ознаменовал полный отказ Intel от использования шины FSB в качестве связующего звена между процессором и чипсетом, а интеграция контроллера памяти DDR3 дала возможность передавать данные из памяти напрямую в CPU. Но и на этом инженеры компании не остановились, перенеся контроллер шины PCI Express на кристалл процессора, что дало возможность полностью отказаться от двухчиповой компоновки набора системной логики. Разводка материнских плат стала проще и дешевле, но из-за отсутствия доступных моделей CPU с разъемом LGA1156 новую платформу пока экономически целесообразной не назовешь.

Процессоры для разъёма LGA 1156 не имеют внешнего интерфейса QuickPath, поскольку чипсеты для данного разъёма поддерживают только однопроцессорную конфигурацию, а функциональность северного моста встроена в сам процессор (и следовательно, для связи процессора с аналогом южного моста используется шина DMI). Однако внутри процессора LGA 1156 связь между ядрами и встроенным контроллером PCIe осуществляется через встроенную шину QuickPath[4][5].

Каждое соединение шины QuickPath состоит из пары односторонних каналов, каждый из которых физически реализован как 20 дифференциальных пар проводов. Данные передаются в виде пакетов (дейтаграмм). Пропускная способность одного канала составляет от 4,8 до 6,4 миллиарда передач в секунду. Одна передача содержит 16 бит полезной нагрузки, следовательно теоретическая суммарная пропускная способность одного соединения (в двух направлениях) — от 19,2 до 25,6 гигабайт в секунду (то есть от 9,6 до 12,8 гигабайт/с в каждую сторону); при этом один процессор может иметь несколько соединений.

Шина QP служит для соединения устройств в системе между собой, а также для «общения» процессоров между собой в многопроцессорных системах. Этому способствует её кэш - когеренстность (передача кэш-данных в обход оперативной памяти на полной скорости шины).

В сокетах LGA 1156 и LGA 1155 шина применяется, только внутри процессора для связи ядер, контроллёров оперативной памяти и PCI-Express.

Шина имеет два 20-ти битных соединения, которые передают данные в двух направлениях. 4 бита используются для передачи служебной информации и исправления ошибок (ECC), а остальные 16 бит для передачи данных (4\1). Шина способна работать со скоростью 6,4 GT/s (3,2 Ггц), что суммарно составляет 25,6 Гбайт/с (12,8 Гбайт/с в одну сторону).

С появлением очередного чипсета, а теперь и процессора, тема разгона памяти на платформе Intel не теряет своей актуальности, так как позволяет иногда повысить быстродействие системы и сэкономить на покупке модулей DIMM. Как оказалось, для работы памяти на частоте свыше 1800 МГц необходимо поднимать напряжение на контроллере памяти до 1,4~1,6 В, а то и выше, что влечет за собой сильный нагрев CPU. Да и не каждый процессор может функционировать в таком режиме, так как с повышением частоты модулей растет частота кэша третьего уровня и контроллера памяти, которая должна превышать значения памяти в два раза. Отчасти эта проблема решилась с переходом процессоров серии Core i7-900 на новый степпинг D0, и обладателям таких CPU стало проще достигать 2000 МГц при разгоне памяти.

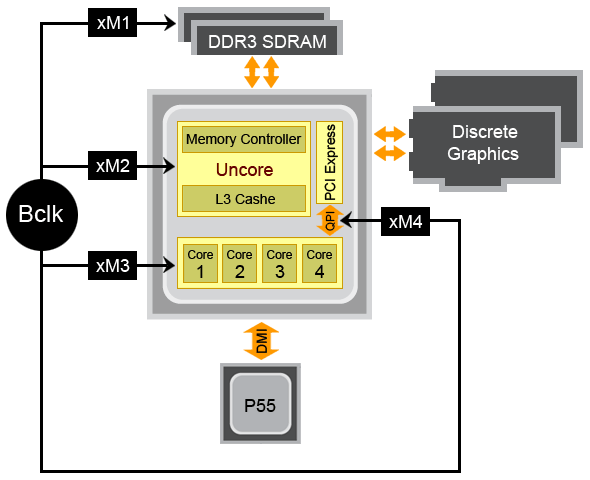

Теперь давайте посмотрим, что изменилось с переходом на более доступную платформу LGA1156 (ядро Lynnfield). Как и ранее, частоты большинства узлов системы (процессор, контроллер памяти и кэш третьего уровня, называемые блоком Uncore, шина QPI и память) получаются за счет перемножения определенных коэффициентов на базовую частоту (на блок-схеме множители xM1, xM2, xM3 и xM4), равную в номинале 133 МГц.

Но данные между процессором и чипсетом теперь передаются по шине DMI (знакомая еще с семейства наборов системной логики Intel 915/925), а интерфейс QPI, используемый для этой цели в процессорах Bloomfield, применяется уже для связи между интегрированным контроллером PCI Express и самим CPU. Контроллер памяти лишился одного канала, став 128-битным, и за счет снижения нагрузки на этот блок его частота зафиксирована на одном значении (множитель х18 для серии процессоров Core i7-800 и х16 для Core i5-700), а не так, как было ранее в решениях LGA1366. Свободы по выбору множителя шины QPI у пользователя стало больше, и теперь он может установить либо х18, либо х16 (напомним, что в процессорах Core i7-9xxx не «экстремальных» версий коэффициент умножения был зафиксирован на х18, а у моделей EE равнялся х18, х20 и х24). С памятью стало немного интереснее — максимально доступный множитель равен х12 для Core i7-8xx и x10 для Core i5-7xx, тогда как у CPU с разъемом LGA1366 он x16. Получается, что для старших процессоров новой платформы в стандартном режиме работы будет доступна лишь память DDR3-1600, а для младших — DDR3-1333. Максимальное напряжение питания модулей осталось на прежнем уровне и составляет 1,65 В.

Date: 2015-05-22; view: 888; Нарушение авторских прав