Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Типы логических микросхем

|

|

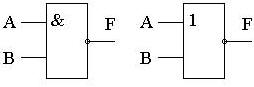

Логические ИМС выпускаются в виде серий (наборов) элементов, обеспечивающих выполнение множества логических операций. В основе каждой серии лежит схемное решение так называемого основного логического элемента, на базе которого создаются более сложные схемы. Чаще всего в качестве базового выбирается элемент " И-НЕ " (штрих Шеффера), реже – " ИЛИ-НЕ" (стрелка Пирса). Их обозначения приведены соответственно на рисунке 5.2.1., а таблицы истинности соответственно в таблицах 5.2.1. 5.2.2.

Рис. 5.2.1.Элементы " И-НЕ " (штрих Шеффера) и " ИЛИ-НЕ" (стрелка Пирса).

Даже на одном виде логических элементов "И-НЕ ", либо " ИЛИ-НЕ" можно построить оказывается любое логическое и цифровое устройство. Элементы "И-НЕ" (или "ИЛИ-НЕ") выполняются в виде различных схем, которые определяют основные типы логики. На сегодня широко известны следующие типы: ДТЛ – диодно-транзисторная логика; ТТЛ – транзисторно-транзисторная логика; ЭСЛ – эмиттерно-связанная логика; ТТЛШ – транзисторно-транзисторная логика с диодами Шоттки. Название типа логики очевидно определяется теми компонентами, на которых строятся логические элементы.

Таблица 5.2.1. Таблица 5.2.2.

| A | B | F=A | B | A | B | F=A $ B | |

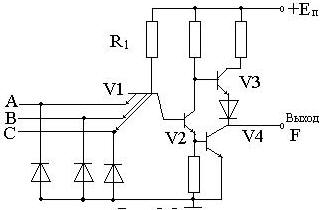

В настоящее время наибольшее распространение получили элементы ТТЛ-логики благодаря их низкой стоимости, относительно высоких быстродействия, нагрузочной способности и помехоустойчивости. На рис. 5.2.2. приведена схема базового логического элемента " И-НЕ" ТТЛ -типа.

Рис. 5.2.2. Логический элемент " И-НЕ" ТТЛ -типа на многоэмиттерном транзисторе

В основе этого класса элементов – многоэмиттерный транзистор V1. Функции многоэмиттерного транзистора сводятся к замене диодной части элемента "И-НЕ". Транзисторы V1 и V2 собственно и образуют схему "И-НЕ", на транзисторах V3 и V4 собран неинвертирующий выходной каскад для усиления по мощности выходного сигнала.

При "1" на всех входах (А=В=С=1), (т.е. подан высокий потенциал) все эмиттерные переходы закрыты, коллекторный же переход открыт, поэтому через R1 течет ток, образующий базовый ток V2 достаточный для его насыщения. На коллекторе V2 потенциал близок к нулю (0), часть эмиттерного тока V2 поступает в базу V4 и насыщает его, а V3 закрыт, поэтому на выходе (коллекторе V4) имеется сигнал "0".

При подаче хотя бы на один вход V1 нулевого потенциала (сигнал "0") соответствующий эмиттерный переход V1 открывается, ток резистора R1 переходит во входную цепь V1, т.к. она обладает меньшим сопротивлением, чем входное сопротивление V2. Поэтому ток базы V2 стремится к нулю, V2 запирается, на его коллекторе высокий потенциал близкий к Еп, V3 отпирается, V4 запирается, поэтому на выходе элемента имеем высокий потенциал (сигнал "1").

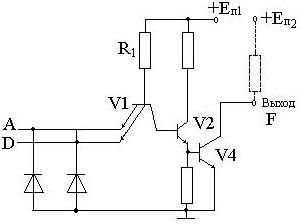

Вариантом логического элемента " И-НЕ" ТТЛ -типа является схема с открытым коллекторным выходом, приведенная на рис. 5.2.3.

Рис. 5.2.3. Логический элемент " И-НЕ" ТТЛ -типа на многоэмиттерном транзисторе с открытым коллекторным выходом

В коллекторную цепь V4 может быть включена любая внешняя нагрузка, второй вывод которой соединяется с положительным полюсом источника питания Еп2. Причем Еп2 может быть иным, чем Еп1, что удобно.

Для определения характеристик и параметров цифровых микросхем рассмотрим логические элементы (ЛЭ) ТТЛ типа. Наибольшее распространение получили элементы с положительной логикой (транзистор типа n-p-n ). В положительной логике значению логической «1» ставят в соответствие большее, а значению логического «0» – меньшее значение напряжения или тока. Потенциальный способ представления логического «0» и логической «1» при положительной логике приведен на рис. 5.2.4.:

Рис. 5.2.4. Потенциальный способ представления логического «0» и логической «1» при положительной логике

На рисунке 5.2.4.:

- уровень логического «0»;

- уровень логического «0»;

- уровень логической «1»;

- уровень логической «1»;

.

.

Динамические характеристики ЛЭ приведены на рис. 5.2.5.

Рис. 5.2.5. Динамические характеристики ЛЭ

Время задержки ЛЭ зависит от времени задержки переднего t З 1 и заднего t З 2 фронтов и определяется из выражения tЗ = (tЗ1+ tЗ2).

Нагрузочная способность ЛЭ характеризует его способность получать сигнал от нескольких источников информации и одновременно быть источником информации для ряда других элементов.

Для численной характеристики нагрузочной способности ЛЭ используются:

· n – коэффициент разветвления – характеризует количество выходов для элементов данной серии, которые могут быть подключены к одному выходу. Для ТТЛ n =10. Нагрузочная способность элемента характеризуется его выходным сопротивлением RВЫХ;

· m – коэффициент объединения – характеризуется количеством входов данного логического элемента (от двух и более).

Различают следующие статические характеристики ЛЭ:

· IВХ = f(UВХ) – входная характеристика элемента, характеризующаяся входным сопротивлением логического элемента. Сопротивление RВХ различно при подаче низкого и высокого уровней сигнала обычно при высоком уровне сигнала RВХ больше.

· UВЫХ = f(IВЫХ) – нагрузочная (выходная) характеристика (рис. 5.2.6.). Её угол наклона определяется выходным сопротивлением ЛЭ.

· UВЫХ = f(UВХ) – переходная характеристика или амплитудная передаточная характеристика ЛЭ. Амплитудная передаточная характеристика инвертирующего ЛЭ ТТЛ -типа с положительной логикой приведена на рис. 5.2.7., а), неинвертирующего ЛЭ – на рис. 5.2.7., б).

Рис. 5.2.6. Нагрузочная характеристика ЛЭ

а) б)

Рис. 5.2.7. Амплитудная передаточная характеристика инвертирующего (а) и неинвертирующего (б) ЛЭ ТТЛ -типа с положительной логикой

Логическая «1» соответствует уровням от E1МИН до  .

.

Логический «0» соответствует уровням от  до E0МАКС.

до E0МАКС.

Участок АВ – соответствует зоне отсечки ключа, CD – насыщению, ВС – переходная область (активный режим,  ). Чем круче участок ВС, тем выше качество ЛЭ.

). Чем круче участок ВС, тем выше качество ЛЭ.

Пороговый уровень нуля на входе UП0 характеризует максимально возможный входной сигнал (UВХ>UП0), а пороговый уровень «1» – UП1 характеризует минимальный входной сигнал (UВХ>UП1).

Термин помехоустойчивость используется для обозначения максимального уровня помехи, которая, будучи добавлена к логическому сигналу при самых неблагоприятных условиях, не будет еще приводить к ошибочной работе схем. Так, например, для элементов ТТЛ помехоустойчивость составляет 0,4 В, так как любой сигнал ниже 0,8 В интерпретируется ими как низкий уровень, а любой сигнал выше +2 В – как высокий, в то время как уровни выходных сигналов составляют в самом неблагоприятном случае +0,4÷+2,4 В соответственно.

Помехоустойчивость ЛЭ при передаче «0» на входе ΔU П 0 определяется выражением с учётом наихудшего случая:

ΔUП0=UП0–E0МАКС, где E0МАКС – максимальный уровень «0» элементов данной серии (рис. 5.2.8.).

Рис. 18.7. Помехоустойчивость ЛЭ

Помехоустойчивость ЛЭ при передаче «1» определяется аналогично:

ΔUП1 = E1МИН – UП1.

Быстродействие ЛЭ серий ИС ТТЛ в основном определяется инерционными свойствами применяемых биполярных транзисторов и нагрузки. Инерционность, обусловленная параметрами нагрузки, зависит от конкретной схемы и конструктивного выполнения логического устройства.

Date: 2015-05-09; view: 1976; Нарушение авторских прав