Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Раздел 2 Алгоритм создания ИМС в среде Cadence Virtuoso

|

|

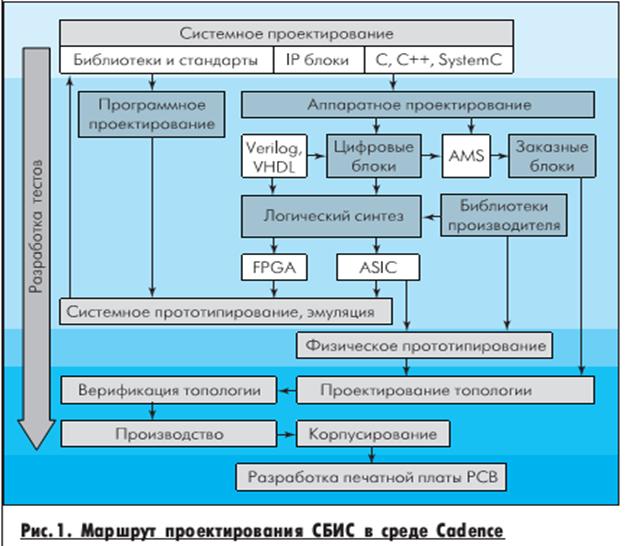

Технология Cadence охватывает практически все уровни разработки сложных систем – от системного уровня, свойственного разработчикам аппаратуры, до уровней логического, схемотехнического и топологического проектирования СБИС, их корпусирования, а также разработки печатных плат, на которых эти СБИС будут монтироваться.

В целом проектирование СБИС в среде Cadence включает следующие этапы:

• системное проектирование – построение модели системы на высоком уровне абстракции с использованием языков программирования C/C++ и SystemC, разбиение на программные и аппаратные модули, исследование параметров системы, получение спецификаций (набора требуемых параметров) на программные и аппаратные блоки;

• аппаратное проектирование и верификация – разработка на основе спецификации поведенческих моделей отдельных блоков системы с использованием языков Verilog/VHDL, реализация проекта в базисе библиотек производителя ИС, проверка программно-аппаратной реализации на соответствие спецификациям, полученным на системном уровне;

• физическое прототипирование – предварительное размещение элементов, оценка потребляемой мощности, планирование шин питания и иерархии тактовых сигналов, качественная оценка возможных искажений сигнала;

• проектирование и верификация топологии кристалла – разработка топологии заказных блоков, трассировка на уровне ячеек, проверка правил проектирования топологии, экстракция паразитных параметров.

Раздел 3 “Иерархический подход в проектировании ИМС ”

Исходным элементом при проектировании были выбран МДП-транзисторы p-n - типа с встроенным каналом

Использование графического редактора Cadence Composer Schematic Editor, является традиционным для описания проектируемого устройства на транзисторном уровне. Редактор предоставляет возможность визуального размещения основных компонентов схемы (транзисторов, диодов, конденсаторов, катушек индуктивности), вспомогательных компонентов (источников постоянного тока и напряжения, источников малых сигналов), а также контактов (пинов), использующихся при иерархическом представлении сложных схем, и соединения элементов между собой.

Результатом работы в Composer Schematic Editor является создание таблицы соединений схемы, записи которой служат в дальнейшем входными данными для других инструментов САПР Cadence. Очевидно, что на следующих этапах разработки устройства может потребоваться изменение начального представления схемы. В этом случае будут откорректированы и записи таблицы соединений.

Рассмотрим реализацию логических элементов с использованием NMOS-транзисторов и PMOS-транзисторов.

На рисунке 2а представлены их принципиальные электрические схемы. Когда сигнал Vx=0V, NMOS транзистор закрыт. Поэтому ток через резистор R отсутствует, и на выходе Vf=5V. С другой стороны, когда Vx=5V, транзистор открыт и на выходе Vfустанавливается низкий уровень напряжения. Точное значение напряжения на выходе Vfв этом случае зависит от величины тока, протекающего через резистор и транзистор. Использование резистора в схеме инвертора обусловлено необходимостью ограничить ток, протекающий в цепи при Vx=5V. В интегральной схемотехнике в качестве такого ограничителя обычно используется транзистор.Используя последовательное соединение NMOS-транзисторов, как показано на рисунке 2б, можно реализовать логический элемент И-НЕ. Если Vx1=Vx2=5V, оба транзистора будут открыты и Vfбудет равен 0V. Но если либо Vx1, либо Vx2=0, то ток в цепи будет отсутствовать и Vfбудет равен 5V.

Рис.2 а) Схемная реализация инвертора б) схемная реализация логическогг элемента И-НЕ

Раздел 4 “ Моделирование работы и параметров созданного прибора”

1.2 Virtuoso Analog Design Environment — интерфейс и возможности

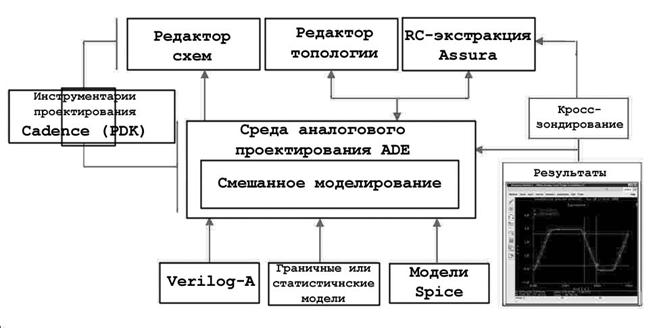

Моделирование или анализ работы устройства, представленного принципиальной электрической схемой, проводится в среде Analog Design Environment. Как было отмечено ранее, входными данными для нее являются записи таблицы соединений схемы, на основании которых строятся системы дифференциальных уравнений.В ходе решения данных систем могут быть получены величины параметров, характеризующих работу моделируемого устройства.

Analog Design Environment поддерживает моделирование с использованием различных уровней абстракции моделей - от чисто поведенческого на верхнем системном уровне до точных, откалиброванных по экспериментальным данным на нижнем, наиболее детальном уровне. Уровни абстракции физического дизайна меняются от оценочных на ранних стадиях, до финальных трассировки и экстракции. Кремниевый анализ, основанный на расширенных моделях полупроводниковых приборов, прецизионной экстракции и средствах анализа, дают адекватную информацию в течение всего процесса проектирования.

В зависимости от сложности и объема решаемых задач, Vittuoso ADE (Analog Design Environment) может интегрировать различные системы аналогового моделирования (Spice, Spectre, UltraSim, Multi-mode Simulation), обепечивать обратную аннотацию паразитных параметров, экстрагируемых с помощью Assura RC, поддерживать кросс-пробинг между схемным вводом (Virtuoso Schematic Editor), топологическим редактором (Virtuoso Layout Editor) и системой анализа результатов моделирования..

Рис.4 а) Основные компоненты среды проектирования Virtuoso ADE

б) Диалоговое окно для выбора параметров и методик моделирования

Раздел 5 «Достижение предела классических подходов с использованием ОДУ. Пути решения кризиса»

Классические программы моделирования аналоговых электронных схем, обеспечивают хорошую сходимость решения в большинстве случаев и гарантируют достаточную точность. Однако, постоянный рост сложности и объемов проектов БИС привел к увеличению размеров схем до десятков и сотен миллионов узлов. Как следствие, производительность классических программ моделирования, построенных на традиционном подходе составления и решения системы ОДУ с применением методов разреженных матриц, стала явно недостаточной для решения системы уравнений, описывающей всю схему.

Подходы, применявшиеся несколько лет назад, состоят в расчете фрагментов схем, базовых ячеек или в комбинированном применении логических и временных расчетов совместно с моделированием аналоговых фрагментов схем на уровне транзисторов. Широкое распространение нашло также макромоделирование.

В последние годы, интенсивно начали развиваться программы моделирования нового поколения, так называемые «быстрые симуляторы». Их применение дает качественный скачок в производительности. Появилась возможность моделировать БИС объемом в десятки и сотни миллионов узлов с точностью и требованиями к вычислительным ресурсам, близкими к традиционным программам моделирования.

Решение, предлагаемое Cadence на данном сегменте рынка, - платформа Virtuoso и система FastSPICE Ultrasim. Наряду с известными системами моделирования, Ultrasim интегрирован в общую среду разработки Virtuoso и дает возможность быстро получить решение с приемлемой точностью при возрастании сложности проекта на несколько порядков.

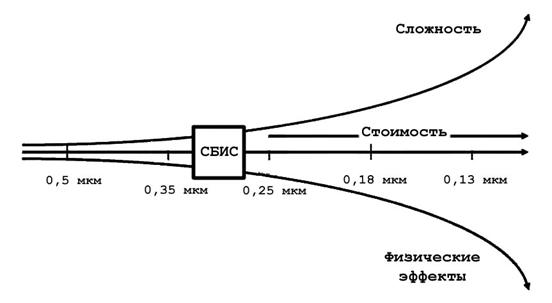

Технические требования к аналоговым, заказным цифровым, радиотехническим и смешанным проектам росли экспоненциально в последнее десятилетие (рис. 2). Экономические факторы и конкуренция на рынке электроники вынуждают разработчиков применять новые технологии и объединять прежде независимые блоки на одном кристалле (System-On-Chip, SOC). Многие производители переходят на современные технологии проектирования по нормам 0.13 мкм – 65 нм, и совмещают аналоговое проектирование, с нанометровыми цифровыми дизайнами. Более того, основой цифрового проектирования является использование библиотек стандартных и специализированных заказных блоков, разрабатываемых с применением средств аналогового моделирования.

Рис. 5 Взаимосвязь технологии, сложности и стоимости проекта

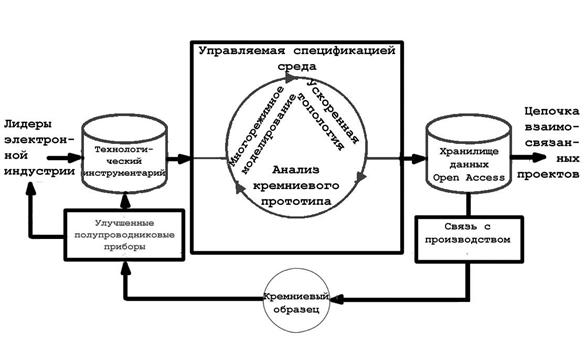

Сложность, объем современных проектов и новые физические эффекты требуют соответствующих технологий заказного проектирования, объединяющих возможности быстрого нисходящего (top-down) проектирования с точностью восходящего (bottom-up) проектирования, идущего от кремниевой реализации. Meet-in-the-middle – современная методология, сочетающая в себе скорость и точность (рис. 3)

Платформа для заказного проектирования Virtuoso [2] является понятной системой для быстрого и точного проектирования, оптимизированной для технологии meet-in-the-middle, например Analog Custom Design (ACD).

Рис.6 Процесс проектирования с помощью платформы Vituoso

В Virtuoso входит среда, определяемая спецификацией, многорежимное моделирование, имеющее общий синтаксис, модели и системы уравнений, значительно ускоренные слои и объединенная на уровне всего кристалла, а также среда смешанного моделирования.

Virtuoso поддерживает моделирование с использованием различных уровней абстракции моделей - от чисто поведенческого на верхнем системном уровне до точных, откалиброванных по экспериментальным данным на нижнем, наиболее детальном уровне. Уровни абстракции физического дизайна меняются от оценочных на ранних стадиях, до финальных трассировки и экстракции. Кремниевый анализ, основанный на расширенных моделях полупроводниковых приборов, прецизионной экстракции и средствах анализа, дают адекватную информацию в течение всего процесса проектирования.

В зависимости от сложности и объема решаемых задач, Vittuoso ADE (Analog Design Environment) может интегрировать различные системы аналогового моделирования (Spice, Spectre, UltraSim, Multi-mode Simulation), обепечивать обратную аннотацию паразитных параметров, экстрагируемых с помощью Assura RC, поддерживать кросспробинг между схемным вводом (Virtuoso Schematic Editor), топологическим редактором (Virtuoso Layout Editor) и системой анализа результатов моделирования.

Платформа Virtuoso может работать с базой данных Cadence CDBA или с базой OpenAccess. С этой платформой, возможно быстрое проектирование с высоким выходом годных для геометрий от 1 мкм до 90 нм и менее.

ВЫВОДЫ

С использованием современной FastSPICE технологии Virtuoso UltraSim, система моделирования позволяет выполнять высокопроизводительное, аналоговое или смешанное моделирование всей системы. Поддержка многих языков описания объектов обеспечивает независимость языка и уровня абстракции в методологии проектирования. Обобщенная реализация полупроводниковых приборов в системах моделирования, входящих в платформу Virtuoso, гарантирует высокую точность результатов. С учетом RC-редукции, с помощью UltraSim и Virtuoso стало возможным решение ранее недоступных задач полной и точной верификации проекта после фазы разработки топологии на нанометровых технологиях.

Платформа заказного проектирования Vittuoso легко интегрируется в единый маршрут проектирования с платформой функциональной верификации Incisive. Фирма Cadence обеспечила интеграцию новой системы на уровне plug-and-play и предоставила разработчикам возможность использования современных средств аналогового моделирования и заказного проектирования в рамках единой методологии разработки СБИС.

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

1. Жан М.Рабаи Цифрофые интегральные схемы 2-е изд 2007 год

2. Жмурко С.А..Разработка подсистемы поиска информации в гетерогенных САПР на основе многоагентных систем - дис. 2010г.

3. Ф.Томас А Иванов САПР микроэлекроники — ж.Электроника №3 2006г.

4. А Иванов Среда проектирования компании Cadence — ж.Электроника №5 2003г.

5. Шелохвостов В.П.Проектирование интегральних микросхем 2008г.

Date: 2015-07-17; view: 2722; Нарушение авторских прав