Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Храбров Е. А. 4 page

|

|

|

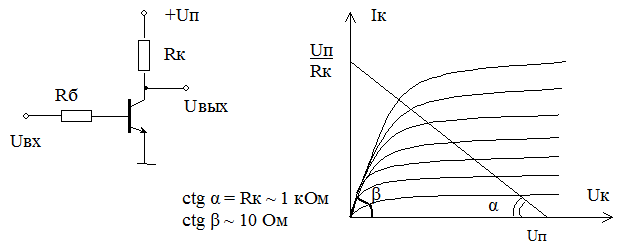

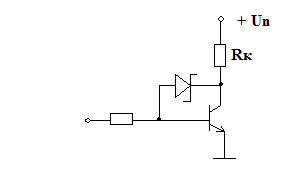

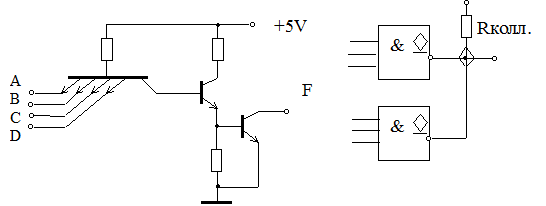

Рис. 6.3. Транзисторная схема НЕ и ее выходная характеристика.

Инвертирующий усилитель на транзисторе включен по схеме с общим эмиттером и кроме усиления сигнала реализует логическую функцию НЕ. Ток базы Iб.гр. для данного Uпит и данного Rк определяет границу между областью активного (усилительного) режима и областью насыщения транзистора. Чем больше базовый ток по отношению к Iб.гр., то есть больше степень насыщения транзистора, тем больше потребуется времени для рассасывания заряда в базе транзистора после его закрывания.

Обеспечить выходное напряжение логического нуля достаточно низким, чтобы иметь какой–то запас от помех можно, если режим транзистора при логическом нуле на выходе устанавливать в области насыщения или вблизи ее. Транзисторы при изготовлении имеют большой разброс по усилению: в 3…5 раз. Выбирая номинал базового резистора Rб таким, чтобы при подаче на вход инвертора заданного U1вх.min даже транзисторы с минимальным усилением находились в области насыщения или вблизи ее, все остальные транзисторы с неминимальным усилением вводить в режим глубокого насыщения.

|

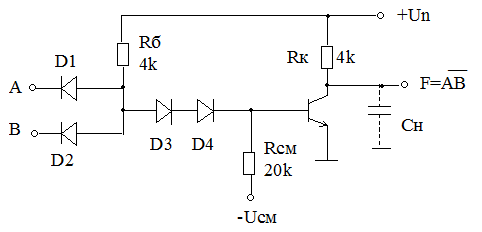

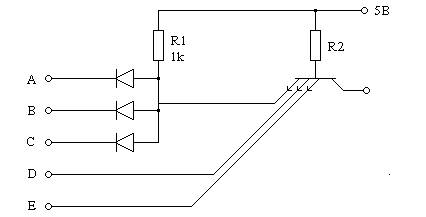

Рис. 6.4. Схема простейшего логического элемента диодно–транзисторной логики

При соединении входной диодной схемы И с выходным транзисторным инвертором получается одна из простейших логических микросхем. Диоды Д3, Д4 и цепь смещения Rсм., –Uсм. введены для обеспечения работоспособности и увеличения помехоустойчивости схемы при уровне логического нуля на входе.

Считаем что вход данного логического элемента подключен к входу такого же логического элемента. Паспортные данные на такие ДТЛ микросхемы: U0вых.max = 0,5 В, прямое падение на входном диоде Uпр.д.max = 0,9 B. Следовательно при лог.0 на выходе предыдущего логического элемента и, соответственно, на входе данного логического элемента напряжение после входного диода в точке Х соединения анодов входных диодов может быть следующим:

U0X = U0вых.max + Uпр.д.max = 0,5 + 0,9 = 1,4 B.

Если бы не было диодов Д3 и Д4, то напряжение логического нуля U0X в точке Х, напрямую попадая на базу выходного транзистора, может быть слишком большим, чтобы этот транзистор закрылся, т.е. может быть так, что выходной транзистор не будет закрываться ни при логической единице ни при логическом нуле на его входе.

При наличии диодов Д3, Д4 и цепи смещения Rсм., –Uсм., ток, протекающий от точки Х через диоды Д3 и Д4 и резистор Rсм. к источнику смещения –Uсм., создает на этих диодах падение напряжения, равное двойному Uпр.д.max, т.е. Uпр. = 1,8 В. Напряжение на базе транзистора Uб при логическом нуле входе при этом будет ниже напряжения в точке Х на величину падения напряжения на открытых диодах Д3 и Д4 (исходя из направления тока в диодах), т.е.:

Uб = UX – 2× Uпр.д.max = 1,4 – 1,8 = – 0,4 В.

Поскольку для начала открывания транзистора n–p–n необходимо положительное напряжение хотя бы 0.1 В, можно считать, что у данной микросхемы статическая помехоустойчивость составит:

U0ПОМ = 0,1 – (– 0,4) = 0,5 В.

Главные недостатки таких схем:

a) низкая нагрузочная способность Кразв.=5;

б) низкое быстродействие: t0,1зд.р. = 110 нс, t1,0зд.р. = 20 нс. Большая разница между задержками по фронтам 0,1 и 1,0 объясняется тем, что заряд емкости нагрузки логического элемента при закрывании выходного транзистора (фронт 0,1) происходит через коллекторный резистор Rк = 4 Ком, а разряд, – через открытый транзистор, имеющий существенно меньшее внутреннее сопротивление RОТКР, чем Rк (RК = 50... 130 Ом, а RОТКР» 1 Ом).

Усовершенствование микросхем ДТЛ путем усложнения выходного инвертора, как показано на рис.6.5, позволило увеличить нагрузочную способность (Kразв. = 16) и быстродействие (t0,1 зд.р. = t1,0 зд.р. = 40 нс).

|

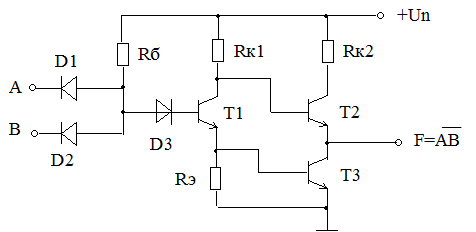

Рис. 6.5. Схема усовершенствованного логического элемента диодно–транзисторной логики

В этой схеме выходные транзисторы Т2 и Т3 собраны по двухтактной схеме (push–pull, – "тяни–толкай"). Они открываются поочередно. Транзистор T1 называют фазоразделительным. Низкоомный резистор Rк2 ограничивает импульс тока, протекающий через транзисторы Т2 и Т3 при переключении, когда один из этих транзисторов открывается, а второй, – закрывается.

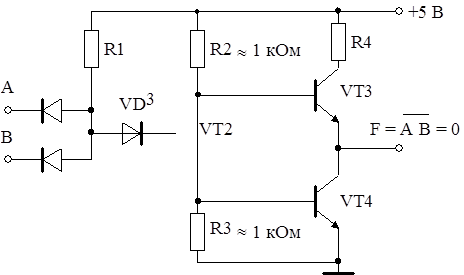

Для анализа работы такого выходного каскада можно использовать следующий прием, – допустить, что в одном случае (при логической единице на обоих входах А и В) фазоинвертирующий транзистор представляет собой короткое замыкание между коллектором и эмиттером, как показано на рис. 6.6, а в другом состоянии этот транзистор представляет собой разрыв, т. е. его как бы нет, что показано на рис 6.7.

Рис. 6.6. Схема ДТЛ логического элемента при логических единицах на всех входах

В первом случае, показанном на рис.6.6, очевидно, что если не учитывать влияние верхнего выходного транзистора, то нижний выходной транзистор VT4 будет открыт. При этом напряжение на его коллекторе будет выше уровня нуля (хотя бы на долю вольта), следовательно, и потенциал эмиттера верхнего выходного транзистора будет выше уровня нуля, выше уровня эмиттера нижнего выходного транзистора. Поэтому можно считать, что для верхнего выходного транзистора напряжения на его базе будет недостаточно для его открывания, хотя этого напряжения и хватает для открывания нижнего выходного транзистора. Следовательно, верхний выходной транзистор будет закрыт, и не будет влиять на работу нижнего выходного транзистора, что подтверждает правильность сделанного выше предположения. Следовательно, при логических единицах на всех входах ДТЛ логический элемент имеет на своем выходе напряжение логического нуля.

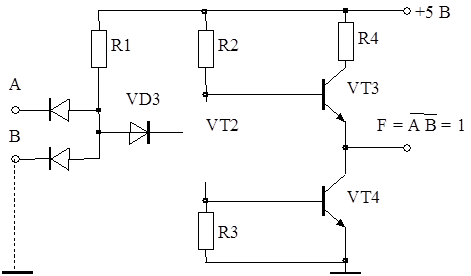

Рис. 6.7. Схема ДТЛ логического элемента при хотя бы одном логическом нуле на входах

Анализ работы схемы, приведенной на рис.6.7, еще более прост. Здесь сразу очевидно, что верхний выходной транзистор будет открыт, а нижний выходной транзистор, – закрыт.

Следовательно, при хотя бы одном логическом нуле на входах ДТЛ логический элемент имеет на своем выходе напряжение логической единицы.

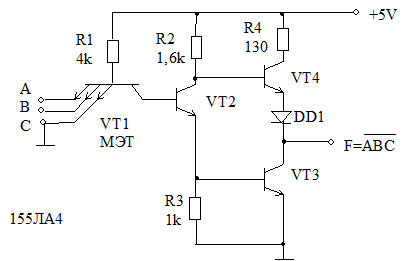

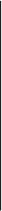

7. ТРАНЗИСТОРНО-ТРАНЗИСТОРНАЯ логика

Основное отличие логических элементов ТТЛ от ДТЛ логических элементов состоит в том, что в ТТЛ логических элементах входные диоды заменены одним многоэмиттерным транзистором (МЭТ). В первом приближении p–n переходы база–эмиттер многоэмиттерного транзистора VT1 можно считать входными диодами как у схем ДТЛ, а переход база–коллектор многоэмиттерного транзистора, – помехозащитным диодом в базе фазоразделительного каскада. Так эта схема ТТЛ и работает при уровне логической единицы на входах A, B и C. Когда же на один из входов поступает логический ноль, многоэмиттерный транзистор VT1 становится транзистором, включенным по схеме ОБ.

При таком переходе входа многоэмиттерного транзистора из логической единицы в логический ноль транзистор фазоразделительного каскада VT2 из открытого (насыщенного) состояния переходит в закрытое, при этом накопленный в базе VT2 заряд быстро рассасывается через открытый многоэмиттерный транзистор VT1, что существенно уменьшает время переключения всего ТТЛ элемента по сравнению с ДТЛ.

Особенностью многоэмиттерного транзистора в открытом состоянии является отсутствие прямого взаимодействия эмиттеров между собой, т.к. их разделяют участки базы. Можно считать, что многоэмиттерный транзистор во включенном состоянии, – это несколько транзисторов, имеющих общий коллектор.

|

Рис. 7.1. Схема простейшего логического элемента транзисторно–транзисторной логики

Трехтранзисторный выходной инвертор ТТЛ, отличается от рассмотренного ранее при анализе ДТЛ логического элемента, введением диода VD1 в эмиттерную цепь верхнего транзистора VT4 двухтактного выходного каскада. Этот диод обеспечивает более надежное запирание транзистора VT4 при логическом нуле на входе логического элемента.

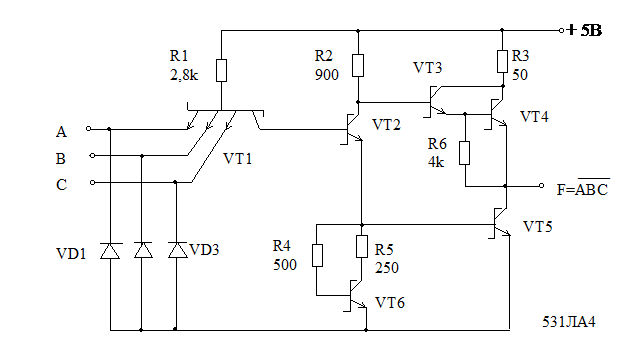

Развитие схемотехники ТТЛ вентиля (логического элемента) привело в основном к следующему:

1) введению антизвонных диодов (VD1…VD3 на рис. 7.2) на входах схемы (ведены во все сериях ТТЛ);

Рис. 7.2. Схема усовершенствованного логического элемента транзисторно–транзисторной логики

2) замене эмиттерного сопротивления R3 фазоразделительного каскада на генератор тока, схема которого собрана на VT6, R4, R5 (называется иногда динамической нагрузкой), который обеспечивает быстрое рассасывание накопленных зарядов в области базы нижнего транзистора VT5 выходного двухтактного каскада при закрывании этого транзистораVT5;

3) замене выходного эмиттерного повторителя верхнего транзистора VT4 выходного двухтактного каскада на составной эмиттерный повторитель на двух транзисторах VT3 и VT4, для уменьшения выходного сопротивления в состоянии логической единицы на выходе, для выравнивания этого сопротивления с сопротивлением при логическом нуле на выходе;

4) замене всех или части транзисторов логических элементов транзисторами Шоттки (Schottky) для уменьшения времени их переключения.

Комбинации 2, 3 и 4 изменений, а также значения внутренних резисторов определяют различия между сериями ТТЛ, при этом изменяются быстродействие и потребляемая микросхемами мощность.

7.1. Транзисторы Шоттки

Транзисторы Шоттки отличаются от обычных тем, что они не входят в глубокое насыщение, следовательно, в их базах в открытом состоянии накапливается мало носителей заряда, и в результате время их рассасывания меньше обычного.

Эффект Шоттки снижает напряжение открывания кремниевого p–n перехода от обычных 0,5... 0,7 В до 0,2... 0,3 В и значительно уменьшает время жизни неосновных носителей в полупроводнике. Эффект Шоттки основан на том, что в p–n переходе или рядом с ним присутствует очень тонкий слой металла, богатый элементами, свободный носителями.

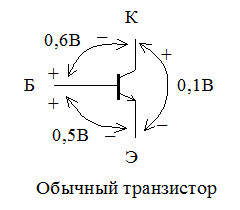

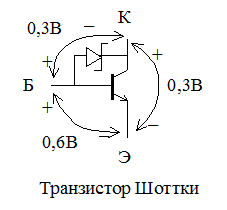

Транзистор Шоттки можно представить как обычный транзистор с диодом Шоттки, включенном между его базой и коллектором, как показано на рис. 7.1.1.

|

Рис. 7.1.1. Транзистор Шоттки, представленный как обычный транзистор с диодом Шоттки, включенном между его базой и коллектором

При открывании транзистора базовый ток нарастает только до значения, лежащего на границе активного режима и области насыщения, а весь избыточный базовый ток отводится через открытый диод Шоттки через коллектор и эмиттер открытого транзистора на землю.

Чем сильнее откроется транзистор, т.е. тем меньше падение напряжения коллектор–эмиттер, тем больший ток отводится через диод Шоттки, минуя базу, на землю. Это приведет к закрыванию транзистора, т.к. уменьшение тока базы закрывает транзистор. Так образуется обратная связь, саморегулирующая режим работы транзистора, удерживая его от глубокого насыщения.

Сами диоды Шоттки имеют очень малые задержки включения и выключения. Накопление заряда в диодах Шоттки не происходит, т.к. протекающий в них ток вызван переносом основных носителей.

Когда транзистор заперт потенциал коллектора выше потенциала базы, а значит, диод Шоттки смещен в обратном направлении и не влияет на работу транзистора.

Если в процессе отпирания транзистора потенциал коллектора становится ниже потенциала базы, диод Шоттки открывается и на нем устанавливается прямое напряжение Uпр. Поскольку это напряжение меньше 0,5 В, то коллекторный переход практически заперт, а следовательно, не возникает режима насыщения и связанных с ним двойной инжекции и накопления избыточных зарядов. Благодаря этому при запирании транзистора исключается задержка, вызываемая рассеиванием избыточного заряда.

На рис 7.1.2. показана разность потенциалов между выводами обычного транзистора и транзистора Шоттки, подтверждающая большее напряжение между коллектором и эмиттером транзистора Шоттки в открытом состоянии.

| |||

| |||

Рис. 7.1.2. Разность потенциалов между выводами обычного транзистора и транзистора Шоттки

7.2. состав ТТЛ логических микросхем малой интеграции

Логический элемент, служащий основой для построения других сложных микросхем называется базовым. В ТТЛ базовым логическим элементом считается элемент 4–НЕ. Микросхема, содержащая в своем корпусе два таких логических элемента, – 2 (4И–НЕ), имеет в своем обозначении символы ЛА1 (К155ЛА1).

В ТТЛ сериях логические элементы И–НЕ распространены более других. Они производятся в виде самостоятельных микросхем, а также служат основой для построения сложных комбинационных и последовательностных микросхем средней и большой интеграции. Кроме базового элемента ЛА1, – 2 (4И–НЕ), в ТТЛ выпускаются логические элементы ЛА2, – 8И–НЕ, логические элементы ЛА3, – 4 (2И–НЕ), логические элементы ЛА4, – 3 (3И–НЕ).

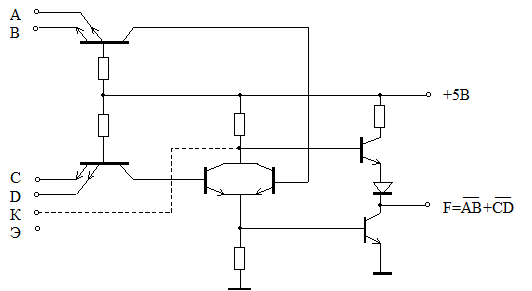

Чтобы реализовать функцию ИЛИ в логические элементы ТТЛ вводят несколько каскадов с фазоразделительными транзисторами, выходы этих транзисторов соединяют параллельно (коллекторы с коллекторами, эмиттеры с эмиттерами) как показано на рис. 7.2.1.

|

Рис.7.2.1. Микросхема 2И–2ИЛИ–НЕ с выводами коллектора и эмиттера фазоразделительного каскада, предназначенными для подключения расширителей по ИЛИ.

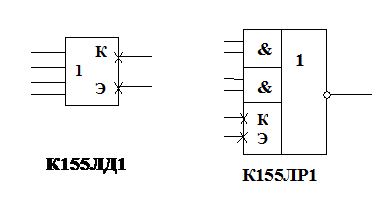

Если входные многоэмиттерные транзисторы таких микросхем имеют по несколько входов И, то получается схема логического элемента ЛР, – И–ИЛИ–НЕ, очень распространенная в ТТЛ (в ТТЛ сериях выпускается тринадцать типов логических элементов И–ИЛИ–НЕ).

В некоторых видах этих микросхем И–ИЛИ–НЕ точки соединений коллекторов и эмиттеров подведены к выводам микросхемы, как показано на рис. 7.2.1 пунктирными линиями, что позволяет подключать дополнительные входные каскады с целью расширения по ИЛИ. При изображении логического элемента И–ИЛИ–НЕ или расширителей с выходами коллектор и эмиттер эти выводы отмечают наклонными крестами (см. рис. 7.2.2), в отличие от логических выводов. На обозначенных крестами выводах микросхем потенциалы могут отличаться от уровней, заданных требованиями для логических уровней.

|

Рис. 7.2.2. Условные графические обозначения расширителя по ИЛИ и логического элемента 2И–2ИЛИ–НЕ, “нелогические” выводы которых, отмечены наклонными крестами

Для расширения по входу ИЛИ в ТТЛ выпускают специальные расширители по ИЛИ на четыре И входа (ЛД1), показанный на рис. 7.2.2 и рис.7.2.3, и на восемь И входов (ЛД3).

|

Рис. 7.2.3. Схема расширителя по ИЛИ, с выходами коллектора и эмиттера, предназначенными для подключения параллельно к выводам коллектора и эмиттера фазоразделительного каскада логического элемента И–ИЛИ–НЕ

Подключив выводы коллектора и эмиттера фазоразделительного каскада расширителя 4И к выводам коллектора и эмиттера фазоразделительного каскада микросхемы 2И–2ИЛИ–НЕ, можно получить логический элемент (2–2–4)И–3ИЛИ–НЕ, как это показано на рис.7.2.4.

Рис.7.2.4. Схема соединения четырехвходового расширителя по ИЛИ с выходами коллектора и эмиттера, подключенными параллельно к выводам коллектора и эмиттера фазоразделительного каскада логического элемента 2И–2ИЛИ–НЕ, создающего логический элемент (2–2–4)И–3ИЛИ–НЕ

Увеличение числа входов И (расширение по И) можно получить, пользуясь элементами из нескольких схем И–НЕ, пользуясь постулатами де Моргана. Тот же результат может быть получен путем подключения дополнительных внешних диодов и резистора к любому из И входов, как показано на рис.7.2.5.

Рис. 7.2.5. Схема расширения по И с помощью дополнительных внешних диодов и резистора

Такое подключение снижает быстродействие и помехоустойчивость микросхемы по И входу, к которому подключены внешние диоды. Статическая помехоустойчивость ТТЛ микросхем составляет 0,4 В. При подаче на один из дополнительных внешних диодов уровня логического нуля падение напряжения на этом открытом диоде практически полностью скомпенсирует напряжение статической помехоустойчивости, поэтому любая помеха при нуле на входе может привести к ложному срабатыванию.

Что касается быстродействия такого подключения, то здесь существенно (почти на порядок) увеличивается длительность фронта переключения из нуля в единицу на том входе логического элемента, к которому подключены дополнительные внешние диоды. Это происходит из–за того, что заряд паразитной емкости этого входа происходит не через верхний выходной транзистор предыдущей микросхемы, имеющий внутреннее сопротивление в открытом состоянии 50...150 Ом, а через внешний резистор величиной 1 кОм. Если дополнительный резистор взять меньшей величины, то при этом может недопустимо возрасти нагрузка на предыдущую микросхему в состоянии логического нуля на ее выходе.

7.3. Выходные каскады ТТЛ микросхем

В микросхемах ТТЛ серий распространены следующие четыре типа выходных каскадов:

1. Обычный двухтактный выходной каскад, показанный на рис.7.1.

2. Умощненный двухтактный выходной каскад, показанный на рис.7.2, иногда его называют буферным выходным каскадом, иногда драйвером.

3. Выходной каскад с так называемым "открытым коллектором" (ОК), в котором из двух выходных транзисторов имеется только один, нижний. В условном графическом обозначении элементов, имеющих выход с открытым коллектором, обычно изображен ромб, подчеркнутый снизу горизонтальной чертой. Изредка используются и каскады с так называемым "открытым эмиттером" (ОЭ), в котором из двух выходных транзисторов имеется только один, верхний. В условном графическом обозначении элементов, имеющих выход с открытым эмиттером, изображен ромб, подчеркнутый сверху горизонтальной чертой.

4. Выходной каскад с так называемым третьим, Z–состоянием, которое не является ни нулевым, ни единичным состоянием выхода микросхемы. Это состояние характеризуется очень высоким выходным сопротивлением данной микросхемы, которая при этом как бы полностью отключена от своей нагрузки. В условном графическом обозначении элементов, имеющих выход с Z–состоянием, обычно изображен ромб, перечеркнутый посередине горизонтальной чертой.

Не разрешается соединять друг с другом выходы микросхем с двухтактными выходными каскады как обычными, так и умощненными. Этот запрет основан на двух причинах.

Если соединить между собой двухтактные выходы двух логических элементов, то, при поступлении на входы этих логических элементов разных сигналов, на их выходах должны быть разные состояния, – на выходе одного логический ноль, на выходе другого, – логическая единица, и неизвестно точно какое же состояние будет в точке их соединения (обычно "побеждает" ноль).

Ток перегрузки, короткого замыкания между ними будет в основном определяться резистором коллекторной нагрузки Rк выходного транзистора, подающего в точку соединения логическую единицу. Главным назначением этого резистора является ограничение очень коротких импульсов сквозного тока, протекающего через два выходных транзистора в выходном каскаде логического элемента при их переключении, когда они оба приоткрыты, поэтому при продолжительной его перегрузке потребляемая или этим резистором, или одним из открытых транзисторов мощность превысить допустимое значение и при достаточно продолжительном состоянии какой–то из логических элементов может выйти из строя.

Еще более опасно подключение выходов логических элементов к корпусу или шине питания, однако, на практике при ремонте плат, при поиске неисправных логических элементов многие электронщики кратковременно (на несколько секунд) закорачивают пинцетом выходы логических элементов на корпус, чтобы подать логический ноль на входы подозрительных логических элементов и при этом предыдущие логические элементы не сгорают.

Никогда нельзя закорачивать выходы логических элементов ТТЛ на шину питания, при этом выход предыдущей микросхемы, находящейся в нулевом состоянии, почти всегда "выгорает". Это касается всех типов выходных каскадов.

Из четырнадцати типов логических элементов И–НЕ в ТТЛ шесть имеют выходы с открытым коллектором (ОК). Они применяются для включения реле, сегментов индикаторов, светодиодов и др. Они, в отличие от микросхем с обычным или умощненным двухтактным выходным каскадом, могут быть соединены друг с другом своими выходами без опасности выхода из строя.

Такое соединение выходов часто называют "монтажное ИЛИ", хотя с точки зрения положительной логики это схема И. Монтажным ИЛИ это соединение называют, возможно, потому, что включить ток в нагрузку (зажечь светодиод, включить реле) может микросхема D1 или микросхема D2. Чтобы такое соединение нормально функционировало, обязательно должна быть нагрузка, подключенная к источнику питания.

Такое соединение иногда используют для подключения выходов нескольких микросхем к какой–либо информационной шине в ЭВМ. Тогда основное значение приобретает быстродействие такого подключения, которое при таком подключении ухудшается.

Ясно, что время задержки распространения t01зд.р. для схем с открытым коллектором и внешним Rн значительно больше чем у схем с обычным двухтактным выходным каскадом (для уменьшения t0,1зд.р. еще в ДТЛ, – прообразе ТТЛ, ввели верхний транзистор в выходной каскад). Ясно также, что чем меньше сопротивление нагрузки Rн, тем меньше задержка, равная t0,1зд.р. = RНАГР × СНАГР, но Rн можно уменьшить лишь до того предела, когда ток выходного транзистора логического элемента, определяемый из условия Iвых = Uпит / Rнагр, не достигает своего максимально допустимого значения I0вых.max. В условном графическом обозначении элементов, имеющих выход с открытым коллектором, обычно изображен ромб, подчеркнутый снизу, как это показано на рис. 7.3.1.

|

|

Рис.7.3.1. Схема логического элемента с выходом с открытым коллектором (ОК) и способ параллельного подключения двух таких выходов к одной линии.

У микросхем, на выходах которых из двух транзисторов двухтактного выходного каскада имеется верхний и отсутствует нижний транзистор, – у микросхем с так называемым открытым эмиттером, в условном графическом обозначении обычно изображен ромб, подчеркнутый сверху.

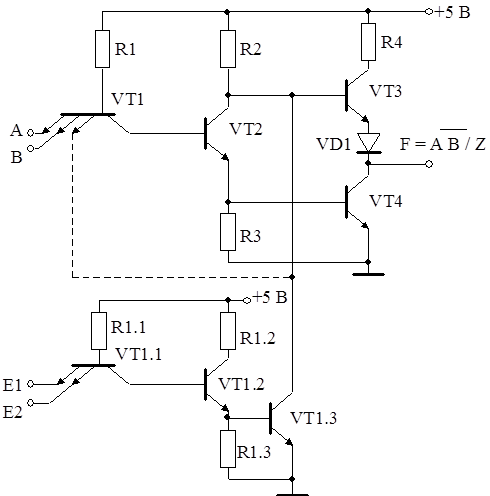

Имеются микросхемы, на выходе которых кроме двух обычных состояний логического нуля и логической единицы может быть и третье состояние Z с высоким выходным сопротивлением. На рис. 7.3.2. приведен пример такой схемы. Таблица истинности такой схемы имеет следующий вид:

Е1 Е2 А В F

Е1 Е2 А В F

0 0 0 0 1

0 0 0 1 1

0 0 1 0 1

0 0 1 1 0

0 1 x x Z

1 0 x x Z

1 1 x x Z

Здесь входы Е1 и Е2 (иногда такие входы обозначают двумя буквами EO – сокращенное ENABLE OUTPUT – разрешение выхода) управляют в соответствии с таблицей истинности состоянием выходного каскада.

В этой микросхеме два логических элемента: верхний, управляемый, и нижний, управляющий, транзисторы которого имеют обозначение, содержащее две цифры, разделенные точкой.

Если на один из входов Е1 или Е2 (или на оба входа) подана логическая единица, то в нижнем управляющем логическом элементе транзистор VT1.1 закрыт, VT1.2 открыт и VT1.3 открыт, следовательно, в верхнем логическом элементе напряжение на коллекторе VT2 близко к нулю, а тогда и напряжение на его эмиттере близко к нулю, значит, будут закрыты оба выходных транзистора VT3 и VT4.

Входы управления Z–состоянием EO следует отличать от входов EI (сокращенное ENABLE INPUT – разрешение входа, когда схема, аналогичная собранной на транзисторах T1.1, T1.2 и T1.3 управляет по пунктирной линии одним из эмиттеров входного многоэмиттерного транзистора основного логического элемента, обеспечивая непрохождение сигналов A и B, отключая входы). При управлении по входам типа EI на выходе F будет состояние логического нуля, а не Z–состояние, как при управлении по входам типа EO.

Рис. 7.3.2. Схема логического элемента с выходом, имеющем три возможных состояния: 0, 1 и "отключено" (Z – состояние), а также имеющего возможность "запрета по входу", показанную с помощью пунктирной связи.

Связь, показанная на рисунке пунктирной линией, не обеспечивает Z–состояние, а обеспечивает только закрытие входных транзисторов (создавая так называемый запрет по входу).

Z–состояние необходимо, когда выходы нескольких логических элементов подключены к одной точке (информационной шине) и эти логические элементы работают поочередно. Итак, чтобы получить состояние Z достаточно закрыть оба выходных транзистора логического элемента.

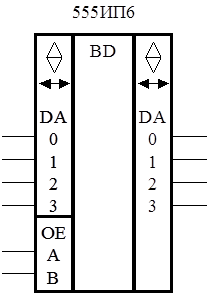

Некоторые логические элементы имеют повышенную (в 2... 5 раз) нагрузочную способность, так, например микросхемы ЛА6, – 2(4И–НЕ) и ЛА12, – 4(2И–НЕ) имеют повышенную нагрузочную способность (Кразв. = 30). Их иногда называют усилителями тока или драйверами (от английского driver – формирователь, водитель). Драйверы с Z–состоянием выхода широко применяются в микропроцессорных системах для подключения самого микропроцессора, памяти и внешних устройств к системным шинам адреса и данных. Такие драйверы называют шинными формирователями (bus driver).

Все микропроцессоры имеют двунаправленную шину данных, а значит, для соединения с этой шиной, как со стороны микропроцессора, так и со стороны внешних устройств требуются двунаправленные драйверы, которые также называют приемопередатчиками. В английском языке приемопередатчик, – transceiver происходит от слияния, комбинации частей слов передатчик, – transmitter, и приемник, – receiver.

Внутри микросхем к каждому двунаправленному выводу микросхемы подключены вход одного и выход другого инвертора (или повторителя). Переключение этих выводов микросхемы с приема на передачу производится по сигналу, поступающему на управляющий вход микросхемы. В условном графическом обозначении микросхем около двунаправленных выводов обычно изображают двунаправленную стрелку, как это показано на рис.7.3.3.

Рис.7.3.3. Условное графическое обозначение двунаправленного шинного формирователя, драйвера (bus driver).

Date: 2015-05-09; view: 1235; Нарушение авторских прав