Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Храбров Е. А. 3 page

|

|

+ A B`C`D`E G 22 + A B C`D E G 23 + A B C`D`E G 24 +

+ А`В С`D E`G 25 + A`B C D E`G 26 + A`B C`D E`G 27 +

+ A`B`C D E`G 28 + A`B`C D`E G 29.

`А`В`C `А`В C `А В C `А В`C А В`C А В C А`В C А`В`C

|

`D`E`G 17 115

|  | ||||||

|  |

`D E`G 11 13 18 116 125 127

|  |

D E`G 12 14 19 117 126 128

D`E`G 110 118

|  | ||||

|  | ||||

D`E G 111 119 129

|  |

D E G 112 120

|  | ||||

|

`D E G 15 113 121 123

|  |

`D`E G 16 114 122 124

|  |

F4 = `B E`G 1,2,3,4,25,26,27,28 + B`D G 5,6,13,14,21,22,23,24 +

+ B`C 7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22 + A`C D E`G 19,29.

Рис.4.10.5. Пример минимизации булевой функции F4 с помощью карты Карно для 6–ти переменных.

4.7. ПОСТРОЕНИЕ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ СХЕМ ПО ЗАДАННЫМ БУЛЕВЫМ ВЫРАЖЕНИЯМ.

Как правило, построение и расчет любой схемы осуществляется, начиная с ее выхода.

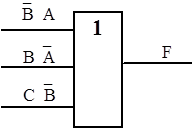

Допустим задано булево выражение:

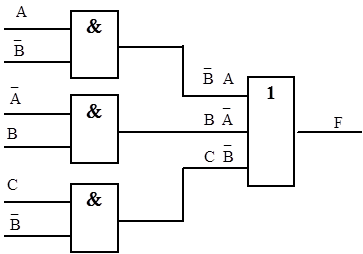

F =`B A + B`A + C`B.

| Первый этап: выполняется логическое сложение, логическую операция ИЛИ, считая входными переменными функции `B A, B`A и C`B: |

|

| Второй этап: к входам элемента ИЛИ подключаются логические элементы И, входными переменными которых являются уже A, B, C и их инверсии: |

|

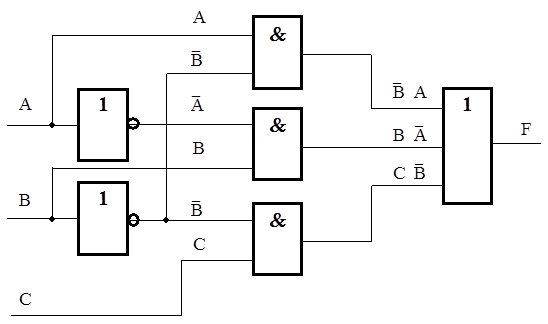

Третий этап: для получения инверсий `A и`B на соответствующих входах ставят инверторы:

Данное построение основано на следующей особенности, – поскольку значениями логических функций могут быть только нули и единицы, то любые логические функции могут быть представлены как аргументы других более сложных функций.

Таким образом, построение комбинационной логической схемы осуществляется с выхода к входу.

4.8. ОСОБЕННОСТИ ПОСТРОЕНИЯ ЛОГИЧЕСКИХ СХЕМ

В ИНВЕРТИРУЮЩИХ БАЗИСАХ.

Первой особенностью построения логических схем в инвертирующих базисах считается непрямая зависимость между простотой булева выражения и минимальностью соответствующей ему логической схемы. Другими словами, самое минимизированное булево выражение не всегда дает схему, минимальную по количеству инвертирующих логических элементов.

Для доказательства этого построим в инвертирующим базисе И–НЕ схему для реализации двухвходовой функции "исключающее ИЛИ", булево выражение которого в двухвходовом случае совпадает с булевым выражением для сумматора по модулю два, и имеет следующий вид:

F = `A B + A`B.

Следует заметить, что данные элементы очень широко применяются в цифровой схемотехнике, и вопрос минимизации их построения довольно актуален.

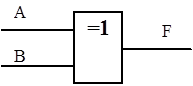

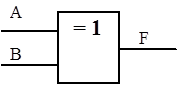

| Условное графическое обозначение логического элемента, реализующего функцию "исключающее ИЛИ" в отечественных схемах: |

|

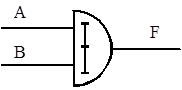

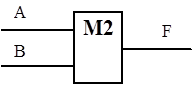

В зарубежных схемах логический элемент "исключающее ИЛИ" обозначают следующим образом:

| - старое обозначение: |

|

| – новое американское обозначение: |

|

| – новое европейское обозначение: |

|

| Условное графическое обозначение логического элемента, реализующего двухвходовый сумматор по модулю два, который в логических схемах выполняет ту же функцию, что и исключающее ИЛИ, в отечественных схемах имеет вид: |

|

Поскольку исходное булево выражение для двухвходовой функции "исключающее ИЛИ", кроме функций И и НЕ содержит и функцию ИЛИ, то, чтобы исключить ИЛИ, преобразуем его следующим образом:

| ||||||||

| ||||||||

|  | |||||||

| ||||||||

F = `A B + A`B = `A B + A`B = `A B × A`B.

Полученное выражение не является минимальным, а чтобы получить действительно минимальное выражение произведем над исходным выражением следующий ряд преобразований:

F = `A B + A`B = `A B + A`B + `A А + В`B =

|

= `A (B + A) +`B (А + В) = (`А + `В) (А + В) =

= А В ×`А `В.

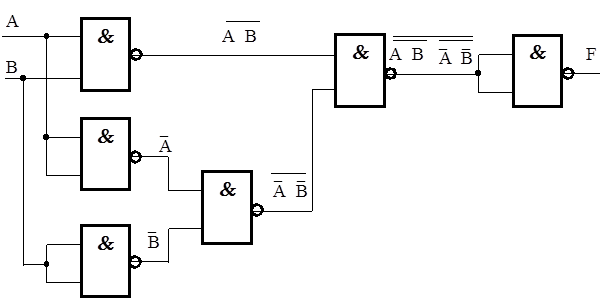

В соответствии с последним минимальным выражением построим в инвертирующем базисе схему из логических элементов И–НЕ:

Теперь попробуем получить такое булево выражение, которое могло бы привести к более простой логической схеме. Для этого над минимальным выражением произведем следующий ряд преобразований:

|  |

F = А В ×`А `В = А В +`А `В =

|

= А В +`А`В + А`В В + А`А В =

|

= А В × А В + А В ×`В +`А`В + `А × А В =

|  |

= А В (А В +`В) +`А (А В +`В) = (А В +`В) (А В +`А) =

| ||||

|  | |||

|

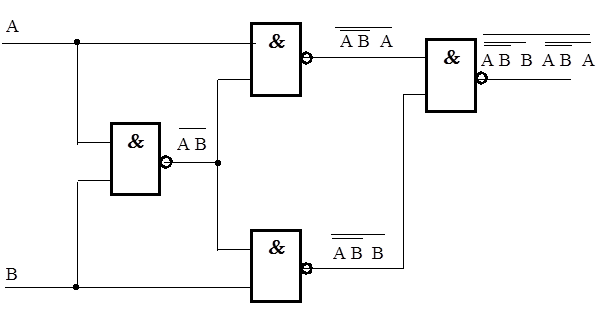

= А В В А В А.

= А В В А В А.

В соответствии с последним булевым выражением построим в инвертирующем базисе схему из логических элементов И–НЕ:

Как видно данная схема оказывается в полтора раза проще, чем предыдущая, несмотря на то, что булево выражение, в соответствии с которым она построена, явно сложнее, чем полученное ранее минимальное выражение. Таким образом, можно считать доказанным утверждение о том, что самое минимизированное булево выражение не всегда дает минимальную по количеству инвертирующих логических элементов схему.

Вторая особенность построения логических схем в инвертирующих базисах приводится без доказательства:

Если в произвольной цифровой схеме (комбинационной):

– проинвертировать все входные и выходные сигналы;

– все элементы И заменить на ИЛИ, а ИЛИ, – на И,

то реализуемая схемой функция не изменится.

5. Цифровые Микросхемы

5.1. Классификация и обозначения цифровых микросхем.

Интегральная микросхема это микроэлектронное изделие, состоящее из активных (транзисторов) и пассивных (диодов, резисторов, конденсаторов) элементов, а также из соединяющих их проводников, которое изготавливается в едином технологическом процессе в объеме полупроводника или на поверхности диэлектрического основания, заключено в корпус и представляет собой неразделимое целое. Иногда ее называют интегральной схема, иногда микросхемой, соответственно, возможны сокращенные обозначения ИМС, ИС, МС.

По технологии изготовления микросхемы делятся на три разновидности: полупроводниковые (самые распространенные), пленочные (почти не выпускаются) и гибридные (выпускают немного и выпуск сокращают).

В полупроводниковых микросхемах все элементы и их соединения изготавливаются в объеме (внутри) и частично на поверхности полупроводника. Иногда полупроводниковую микросхему называют твердотельной схемой, что является буквальным переводом с английского языка (solid state).

В пленочной микросхеме все элементы и их соединения выполнены в виде пленок из проводящих и диэлектрических материалов на диэлектрическом основании. В этих микросхемах нет транзисторов и диодов.

В гибридных микросхемах пассивные элементы и соединительные проводники изготавливают по пленочной технологии, а бескорпусные транзисторы и диоды, изготовленные отдельно по полупроводниковой технологии, соединяют тонкими проводами диаметром 0,04 мм с контактными площадками.

По функциональному назначению микросхемы делятся на две категории:

– аналоговые, обрабатывающие сигналы, изменяющиеся по закону непрерывной функции;

– цифровые, обрабатывающие цифровые сигналы.

Транзисторы, применяющиеся в цифровых микросхемах, бывают двух типов:

– обычные (n–p–n или p–n–p) биполярные транзисторы;

– полевые (униполярные) транзисторы.

В цифровых микросхемах применяются полевые транзисторы только с изолированным затвором, имеющие структуру: металл (затвор), диэлектрик (изоляция затвора), полупроводник (канал, сток–исток), сокращенно МДП, а так как в качестве диэлектрика обычно используется окись кремния, то обычно эти транзисторы, а также микросхемы на них сокращенно называют МОП. Чаще всего в цифровых микросхемах используют пары МОП транзисторов, дополняющие друг друга по проводимости канала, такие микросхемы называют КМОП от слова комплиментарный, что означает дополняющий.

В зависимости от элементов, на которых собраны входные и выходные каскады микросхем, от схемных особенностей этих каскадов цифровые микросхемы делятся на несколько групп или, так называемых "логик" (здесь под словом "логика" подразумевается логический элемент или электронный ключ):

1. РТЛ, – резистивно–транзисторная логика, в которой на входах стоит резистивный сумматор токов, реализующий для положительной логики функцию ИЛИ; выходной каскад собран на транзисторном инверторе;

2. ДТЛ, – диодно–транзисторная логика, в которой на входах стоит несколько диодов, реализующих функцию И или ИЛИ; выходной каскад на транзисторах;

3. ТТЛ, – транзисторно–транзисторная логика, в логических элементах которой к входам подключены эмиттеры многоэмиттерного транзистора; с помощью этого многоэмиттерного транзистора реализуется функция И; выходной каскад собран на транзисторах;

4. ЭСЛ, – эмиттерно–связанная логика, в которой на входах стоят транзисторы, эмиттеры которых связаны друг с другом;

5. nМОП, pМОП, – МОП логика, все элементы которой выполнены на МОП транзисторах с проводимостью канала n –типа (n– МОП) или p –типа (p– МОП);

6. КМОП, – логика, все элементы которой выполнены на двух типах МОП транзисторов nМОП и pМОП, дополняющих друг друга, т.е. комплиментарных;

7. И2 Л, – интегральная инжекционная логика, в которой отсутствуют резисторы; инжекция носителей в область базы транзистора осуществляется с помощью активных генераторов тока, выполненных на p–n–p транзисторах, тогда как сам базовый инвертор, – на n–p–n транзисторах.

По принятой у нас системе обозначение микросхемы должно состоять из четырех основных элементов:

1) цифра, соответствующая конструктивно–технологической группе (1, 5, 6, 7, – полупроводниковые микросхемы, из них 7, – бескорпусные; 2, 4, 8, – гибридные микросхемы; 3, – прочие, в том числе пленочные, вакуумные, керамические и т.д.);

2) две, а в последнее время три цифры, обозначающие порядковый номер разработки серии микросхем;

3) две буквы, обозначающие функциональное назначение микросхемы; первая буква соответствует подгруппе (порядка двадцати подгрупп), вторая, – виду (от трех до семнадцати видов в подгруппе);

4) порядковый номер разработки данной микросхемы внутри своего вида в данной серии.

Номером серии микросхемы считают первые три или четыре цифры. Для микросхем, используемых в устройствах широкого применения, перед номером серии ставится буква К. Для характеристики материала и типа корпуса микросхемы после буквы К могут быть добавлены следующие буквы: Р, – для пластмассового корпуса второго вида, М, – для керамического, металлического и стеклокерамического корпуса второго типа. В конце обозначения микросхемы может быть добавлена буква, конкретизирующая один из основных ее параметров.

Например: КМ155ЛА3, К561ИЕ33, 564ЛА7, КР565РУ8Г.

Корпуса цифровых микросхем бывают в основном двух видов:

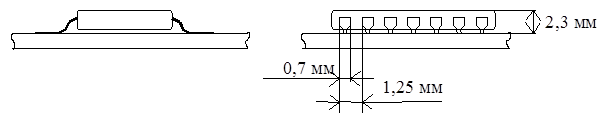

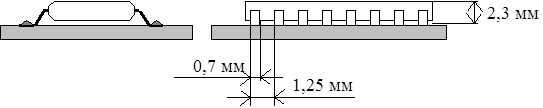

1. Планарные (плоские), у этих микросхем условное обозначение корпуса начинается с цифры 4; выводы числом от четырнадцати до сорока двух расположены с двух сторон микросхемы с шагом 1.25 мм, прямые, припаиваются, как правило, к дорожкам печатной платы на стороне установки микросхем; такие корпуса часто называют SOIC (small outline integrated cirquit, – микросхема в малом корпусе с выводами, не лежащими в одну линию). Иногда такой тип корпуса называют сокращенно, – SO.

Рис. 5.1.1. Планарный корпус микросхемы

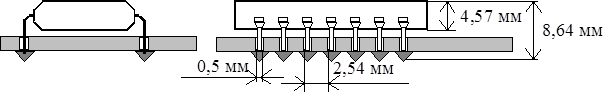

Корпус dip – dual in line package, – в две линии расположенные выводы (иногда этот тип корпуса называют DIL, иногда, чтобы указать, что корпус изготовлен из пластмассы – PDIP, plastic DIP), – корпус микросхемы, у которой обозначение корпуса начинается с цифры 2; выводы числом от четырнадцати до сорока двух с двух сторон микросхемы с шагом обычно 2,5 мм, изогнутые под углом 900, припаиваются только в отверстиях печатных плат.

Рис. 5.1.2. DIP корпус микросхемы

Отечественные ТТЛ микросхемы в планарных корпусах часто имеют в обозначении серии вторую цифру 3 (133, 136), они обычно выпускаются для специального применения при температуре от – 60 0C до 125 0C, а в dip–корпусах имеют вторую цифру 5 (155,1531), выпускаются для широкого применения при температуре от – 10 0C до 70 0C.

Среди миниатюризированных современных корпусов микросхем, предназначенных для припаивания только на стороне установки микросхем, можно в качестве примера привести следующие:

– SOIC – small outline integrated circuit, при обозначении SN… DW

За рубежом в обозначении ТТЛ микросхем имеются числа 54 для микросхем специального (военного) применения, и 74, – для широкого (гражданского) применения. Буквы в конце зарубежных обозначений означают: L, – низкое потребление мощности, но низкое быстродействие; H, – высокое быстродействие, но и большое потребление мощности; S, – с диодами Шоттки (Sсhottky); A, – улучшенные, перспективные от слова Advance (вольный перевод "аванс"); F, – быстрые от слова Fast – быстрый. В обозначение зарубежных КМОП (CMOS) микросхем обычно входит число 40 (CD4011B).

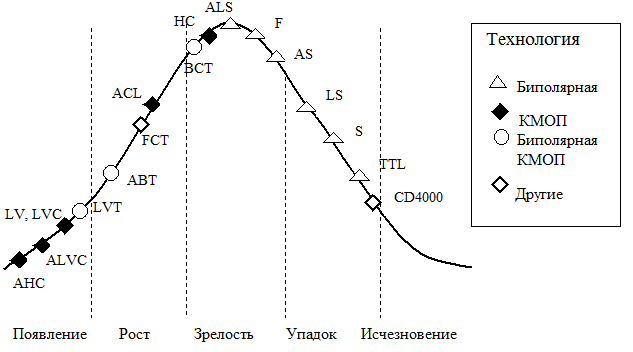

Американская фирма "TEXAS INSTRUMENTS", крупнейший в мире разработчик и производитель цифровых микросхем средней интеграции, в одном из своих проспектов опубликовала график, приведенный на рис. 1, которым, по мнению специалистов этой фирмы, можно охарактеризовать историю развития и перспективы использования различных серий цифровых микросхем.

|

Рис. 5.1.3. Жизненный цикл микросхем различной технологии по данным американской фирмы "TEXAS INSTRUMENTS":

V/ LVC Низковольтная CMOS логика;

LVT Низковольтная технология;

ALVC Усовершенствованная низковольтная CMOS логика;

ABT Усовершенствованная BiCMOS технология;

BCT BiCMOS технология;

F Биполярная технология серии 74F;

AC/ACT Усовершенствованная CMOS логика;

HC/HCT Высокоскоростная CMOS логика.

5.2. Параметры цифровых микросхем

Параметры цифровых микросхем делятся на три группы: статические, динамические и интегральные.

Статические параметры цифровых микросхем характеризуют микросхему в статическом (установившемся) режиме. К ним относятся:

1. Напряжение источника питания Uпит. [В] и допуск на его изменение DUпит. (для ТТЛ DUпит. = ± 5; 10 %; для большинства же серий КМОП допустимо питание в пределах от 3 до 15 В).

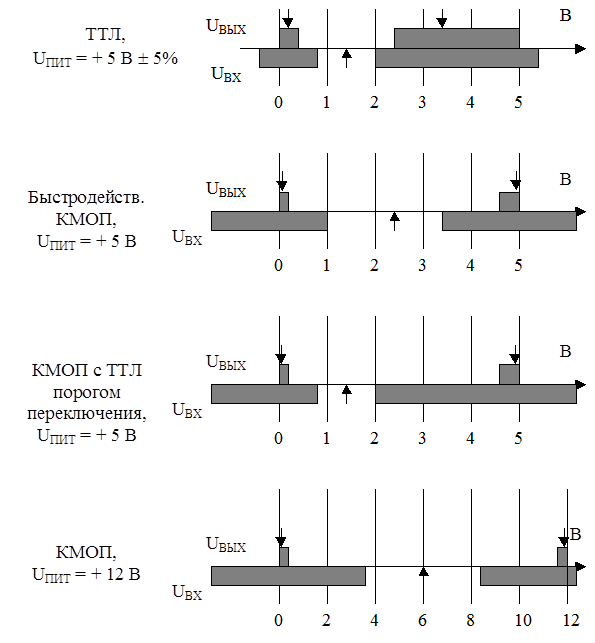

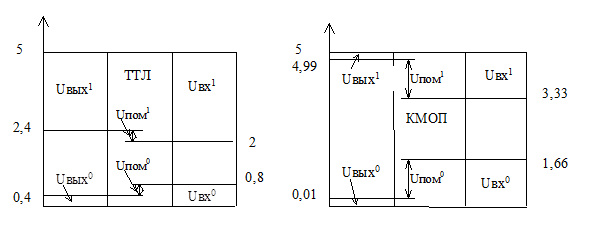

2. Входные и выходные допустимые напряжения U0вх.max, U0вых.max, U1вх.min, U1вых.min [В], для некоторых типов микросхем показаны на рис. 5.2.1.

|

Рис. 5.2.1. Области допустимых значений входных и выходных напряжений ТТЛ и КМОП микросхем при напряжении их питания +5 В и +12 В.

На рис.5.2.1 стрелками, направленными вниз, показаны типовые, наиболее часто встречающиеся значения уровней логического нуля и единицы, а стрелками, направленными вверх, показаны типовые значения порогов переключения микросхем.

3. Входные и выходные токи при лог.0 и лог.1 и их допуски: I0вх.max, I0вых.max, I1вх.min, I1вых.min.

4. Коэффициент разветвления по выходу (это число входов микросхемы данной серии, которые допустимо подключать к данному выходу микросхемы), обычно для ТТЛ Кразв.=10, для КМОП Кразв.=50 … 100.

5. Коэффициент объединения по входу Коб. (обычно это число входов данной микросхемы). Как правило Коб. = 2; 3; 4 и 8. Если нужно другое число, то применяют специальные микросхемы, – расширители, или собирают схему по законам булевой алгебры.

6. Потребляемая мощность (статическая) обычно рассматривается как полу сумма мощностей, потребляемых при нуле и при единице:

РПОТ = (Р0ПОТ + Р1ПОТ) / 2.

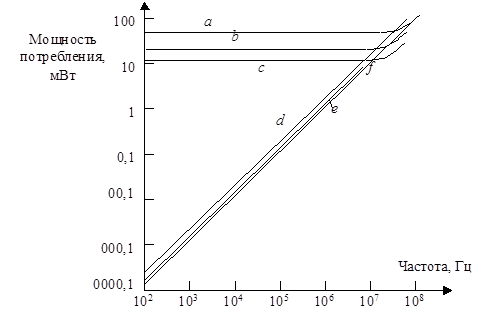

Мощность, потребляемая микросхемами в реальных режимах работы, существенно зависит от частоты их переключения, как это показано на рис.5.2.2.

Рис.5.2.2. Зависимость мощности, потребляемой микросхемами различных серий, от частоты переключения:

a – ТТЛ микросхемы серии КР1531 (F);

b – ТТЛ микросхемы серии К555 (LS);

c – ТТЛ микросхемы серии КР1533 (ALS);

d – КМОП микросхемы серии 1564 (HCT);

e – КМОП микросхемы серии К561 и КР1561 (74C);

f – КМОП микросхемы серии КР1554 (ACT).

7. Помехоустойчивость (статическая) Uпом. – допустимое напряжение помех на входе микросхемы, определяется из двух значений:

| U1ВЫХ.MIN – U1ВХ.MAX | = U1ПОМ, или | U0ВЫХ.MAX – U0ВХ.MIN| = U0ПОМ.

Из этих двух значений выбирается меньшее. Эти значения помехоустойчивости даны для предельных значений питающих напряжений, температуры окружающей среды и др. условий. Реальная помехоустойчивость микросхем примерно в два раза лучше, чем определяемая по приведенной формуле.

Рис. 5.2.3. Области допустимых значений входных и выходных напряжений ТТЛ и КМОП микросхем при напряжении их питания +5 В и напряжения статической помехи при нулевом и единичном уровнях.

В зависимости от продолжительности помехи различают статическую и динамическую помехоустойчивость. Статическую помехоустойчивость связывают с помехами, длительность которых больше времени переходных процессов, а динамическую, – с кратковременными помехами. Динамическая помехоустойчивость лучше статической за счет того, что от короткого импульса помех микросхемы просто не успевает переключиться.

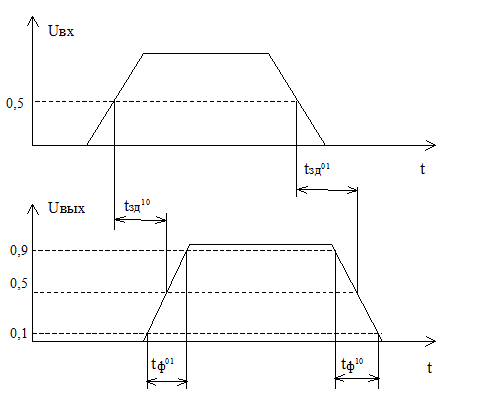

Динамические параметры цифровых микросхем определяют максимальную частоту смены входных состояний, при которой не нарушается нормальное функционирование микросхем. Временные диаграммы, иллюстрирующие способы определения временных динамических параметров, показаны на рис. 5.2.4.

|

Рис.5.2.4. Временные диаграммы, иллюстрирующие способы определения временных динамических интегральных микросхем.

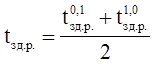

К динамическим параметрам цифровых интегральных микросхем обычно относят следующие:

1. Среднее время tзд.р. задержки распространения переднего и заднего фронтов:

.

.

2. Длительность t0,1Ф фронта выходного сигнала при перепаде от нуля к единице (от 0.1 до 0.9 амплитуды сигнала) и t1,0Ф длительность фронта выходного сигнала при перепаде от 1 к 0 (от 0.9 до 0.1 амплитуды сигнала), как это показано на рис.5.2.4.

3. Максимальная частота переключения:

fMAX £ (t0,1Ф + t1,0Ф) / 2.

Интегральные параметры цифровых микросхем отражают уровень развития технологии и схемотехники, а также качество цифровых микросхем:

1. Энергия переключения ЭПЕР = РПОТР.СР × tЗД.Р [пДж].

2. Степень интеграции N = lg n, где n, – число простых логических элементов (2И–НЕ) на кристалле (при N = 2 микросхемы обычно называют схемами средней интеграции, – СИС; при N = 3 микросхемы обычно называют схемами большой интеграции, – БИС; при N = 4 микросхемы обычно называют схемами сверх большой интеграции, – СБИС).

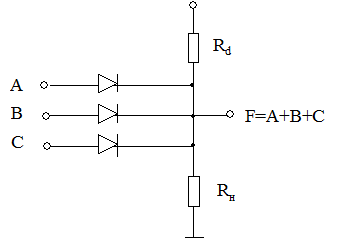

6. Диодные схемы И, ИЛИ, транзисторная схема НЕ, диодно–транзисторная логика

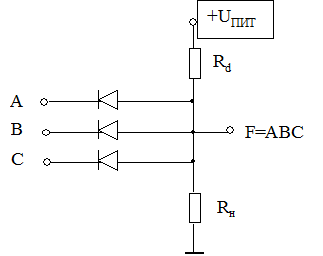

|

Рис. 6.1. Диодная схема И

Если на входах А и В и С схемы И будут высокие уровни, то на выходе F будет высокий уровень. Если хотя бы на одном из входов будет ноль напряжения, то на выходе будет низкий уровень, близкий к нулю, отличающийся от него на величину падения напряжения на диоде Uпр.=0.5 B. Высокий уровень на выходе схемы И при высоких уровнях на всех входах будет в том случае, если R < Rн.

|

Рис. 6.2. Диодная схема ИЛИ

Если на входе А или В или С диодной схемы ИЛИ будет высокий уровень, то на выходе F также будет высокий уровень. Если же на всех входах будут низкие уровни, то и на выходе будет низкий уровень, но только при условии, обратном тому, которое предъявляется в схеме И, а именно R > Rн.

Date: 2015-05-09; view: 759; Нарушение авторских прав