Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Последовательный накапливающий сумматор

|

|

Синтезируем последовательный n-разрядный накапливающий сумматор на базе ОКСм (рассмотрен выше), сдвигающего регистра С(1:n) и триггера Р (для запоминания переноса).

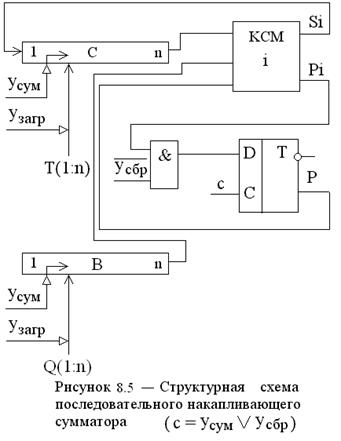

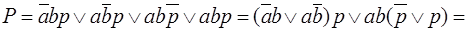

Структурная схема последовательного сумматора приведена на рисунке 8.5. Первое слагаемое загружается в регистр С(1:n), с внешнего регистра T(1:n). Второе слагаемое загружается в регистр В(1:n), с внешнего регистра Q(1:n).

Сложение осуществляется за n тактов. В очередном такте на ОКС складываются очередные цифры слагаемых  и

и  и перенос

и перенос  , полученный в предыдущем такте при сложении предыдущих младших цифр. Перенос

, полученный в предыдущем такте при сложении предыдущих младших цифр. Перенос  , полученный в текущем такте, запоминается на триггере для использования в следующем такте. По истечении n тактов сумма должна оказаться в регистре С. Для записывания в регистр С очередного разряда суммы

, полученный в текущем такте, запоминается на триггере для использования в следующем такте. По истечении n тактов сумма должна оказаться в регистре С. Для записывания в регистр С очередного разряда суммы  и подачи следующей цифры первого и второго слагаемых на ОКС используется микрооперация сдвига (при сдвиге в n-ном разряде регистра С оказывается следующая по старшинству цифра первого слагаемого, а освобождающийся старший разряд регистра С доопределяется значением очередной вычисленной цифры суммы). При сложении младших разрядов перенос должен быть равен нулю, поэтому необходимо предусмотреть микрооперацию сброса триггера Р. Если в триггере есть установочные входы, то сигнал

и подачи следующей цифры первого и второго слагаемых на ОКС используется микрооперация сдвига (при сдвиге в n-ном разряде регистра С оказывается следующая по старшинству цифра первого слагаемого, а освобождающийся старший разряд регистра С доопределяется значением очередной вычисленной цифры суммы). При сложении младших разрядов перенос должен быть равен нулю, поэтому необходимо предусмотреть микрооперацию сброса триггера Р. Если в триггере есть установочные входы, то сигнал  можно подавать на установочный R-вход триггера.

можно подавать на установочный R-вход триггера.

Процесс сложения при помощи последовательного сумматора является не микрооперацией, а микропрограммой (почему?).

8.3. Содержание работы

В процессе выполнения работы необходимо синтезировать одноразрядный двоичный комбинационный сумматор, собрать и исследовать его на макете L-T, построить на его основе и с использованием сдвигающего регистра последовательный сумматор. После этого необходимо построить схему двухразрядного параллельного накапливающего сумматора на основе ОКСм,

полусумматора и запоминающих элементов и исследовать его работу в динамическом режиме. Индивидуальное задание может быть сформулировано преподавателем в виде особых требований к схемной реализации одноразрядного сумматора (по быстродействию, количеству элементов и т. д.).

8.4. Внеаудиторная подготовка к работе

8.4.1. Изучить классификацию сумматоров, методы проектирования и схемные реализации комбинационных и накапливающих сумматоров: ([1], стр. 181-184; [2], стр. 173-185; [3], стр.120-132, [4], стр. 133-141).

8.4.2. Разработать принципиальную электрическую схему одноразрядного сумматора. Оценить ее быстродействие.

8.4.3. Изучить микросхемы К155ИМ3 ([6], стр. 157-158) и К155ИР1 ([6], стр. 104-107) - аналоги 74HC83 и 74HC95).

9.4.4. Синтезировать параллельный четырехразрядный накапливающий сумматор, используя схемы 74HC83 и 74HC95.

8.5. Выполнение работы в лаборатории

8.5.1. Собрать и наладить схему одноразрядного комбинационного сумматора (ОКСм) на макете L-T. Убедиться в ее работоспособности, подавая с кнопок на входные полюса все возможные комбинации и фиксируя значения сигналов суммы и переноса.

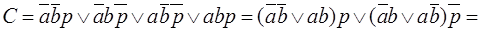

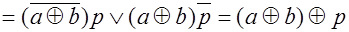

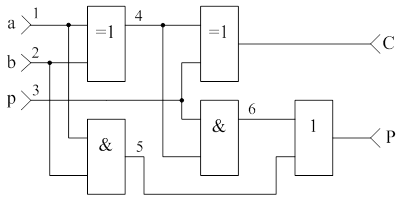

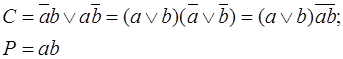

Для обеспечения возможности размещения схемы одноразрядного сумматора на макете Logic, рекомендуется преобразовать функции ОКСм следующим образом:

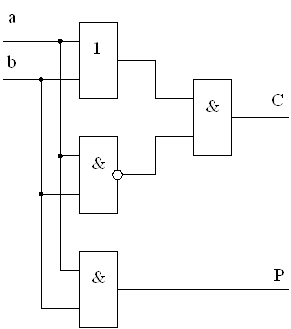

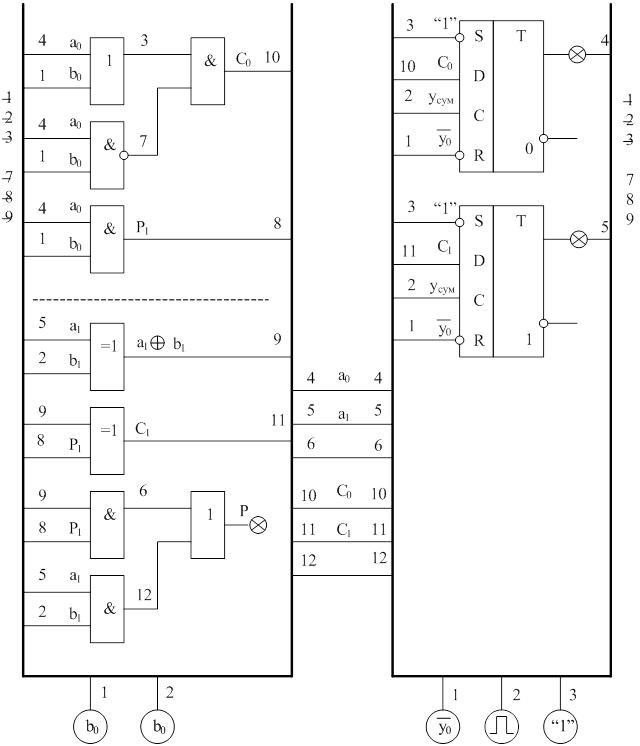

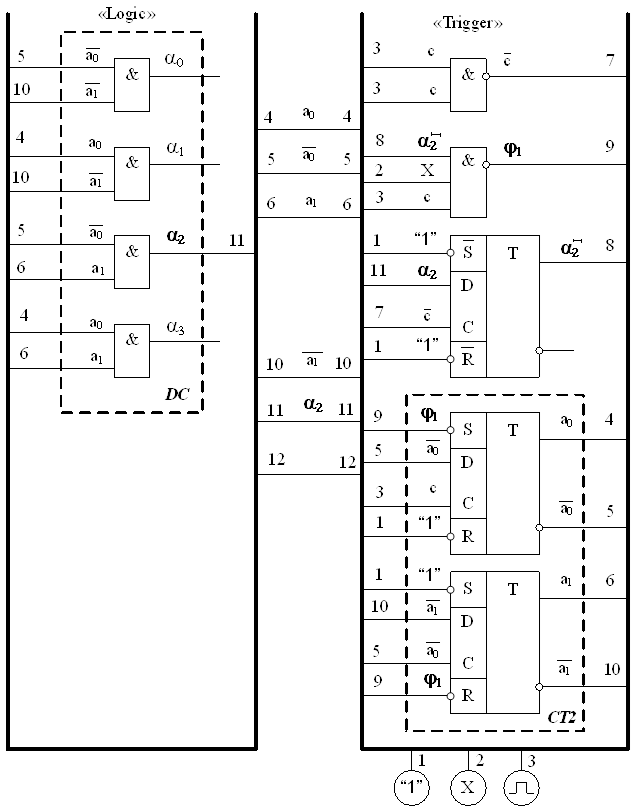

Схема размещения ОКСм на макете Logic изображена на рисунке 8.6.

Рисунок 8.6 – Схема одноразрядного комбинационного сумматора

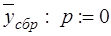

8.5.2. На базе ОКС собрать и наладить схему последовательного суммирования трехразрядных двоичных чисел. Предусмотреть ввод слагаемых в последовательном коде с кнопочного регистра и фиксацию суммы на трехразрядном сдвиговом регистре (рисунок 8.7). Управляющий сигнал  подать с генератора одиночних импульсов. Убедиться в работоспособности схемы на тестовых примерах, реализуя подготовительный такт

подать с генератора одиночних импульсов. Убедиться в работоспособности схемы на тестовых примерах, реализуя подготовительный такт  и три такта суммирования (сдвига)

и три такта суммирования (сдвига)  .

.

Рисунок 8.7 – схема последовательного суммирования

трехразрядных двоичных чисел

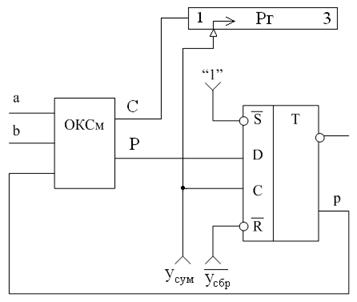

8.5.3. Собрать и наладить схему полусумматора (ПСм).

Полусумматор (рисунок 8.8) – это одноразрядный комбинационный сумматор без входа переноса  . Используется в схемах параллельного суммирования для сложения младших разрядов двоичных чисел. Зависимость выходов от входов ПСм описывается таблицей 8.2.

. Используется в схемах параллельного суммирования для сложения младших разрядов двоичных чисел. Зависимость выходов от входов ПСм описывается таблицей 8.2.

Таблица 8.2 – Таблица истинности

Таблица 8.2 – Таблица истинности

полусумматора

| a | b | C | P |

Рисунок 8.8 - Полусумматор

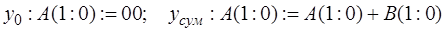

По таблице 8.2 получены следующие функции для выходов полусумматора. Они преобразованы с целью обеспечения возможности размещения схемы на макете Logic.

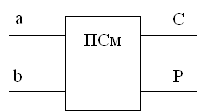

Схема полусумматора изображена на рисунке 8.9.

Рисунок 8.9 – Схема полусумматора

8.5.4. На основе схем ОКСм и ПСм собрать и наладить схему накапливающего двухразрядного параллельного сумматора. Проверить схему в статическом и динамическом режиме. В последнем случае поставить схему в режим работы счетчика и снять осциллограммы на выходах разрядов сумматора. Определить минимальное время такта суммирования (через время задержки срабатывания логических и запоминающих элементов).

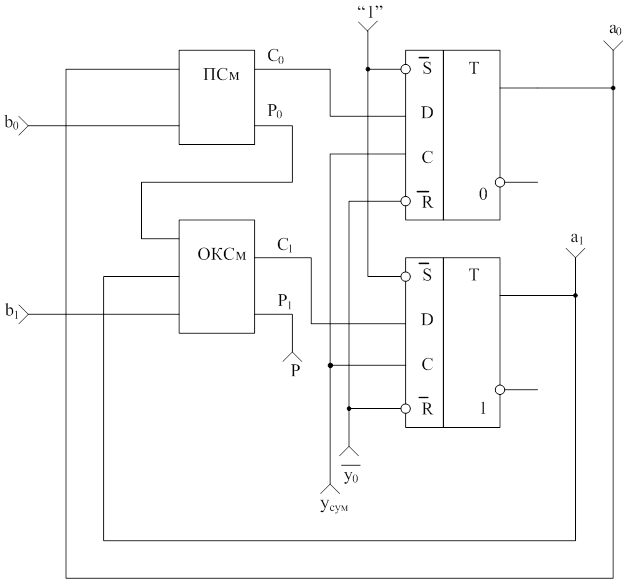

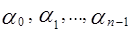

Схема параллельного двухразрядного накапливающего сумматора изображена на рисунке 8.10. Данный операционный элемент выполняет две микрооперации:

Управляющий сигнал  можно подать с кнопки, управляющий сигнал

можно подать с кнопки, управляющий сигнал  целесообразно подать с генератора одиночных импульсов.

целесообразно подать с генератора одиночных импульсов.

Рисунок 8.10 – Двухразрядный параллельный накапливающий сумматор

Схема параллельного двухразрядного накапливающего сумматора в элементном базисе макета «Logic-Trigger» изображена на рисунке 8.11.

Рисунок 8.11 – Схема двухразрядного параллельного накапливающего сумматора

на макете «Logic-Trigger»

8.6. Контрольные вопросы

8.6.1. Чем отличается комбинационный сумматор от накапливающего, последовательный от параллельного?

8.6.2. Какова минимальная задержка сигнала переноса в одноразрядном двоичном сумматоре?

8.6.3. Что такое полусумматор? Как строится полный одноразрядный сумматор из полусумматоров?

8.6.4. Чем определяется время суммирования в параллельном одноразрядном сумматоре? Какие вы знаете способы уменьшения этого времени?

8.6.5. Как с помощью сумматора выполнить операцию вычитания?

9. ЛАБОРАТОРНАЯ РАБОТА № 8. РАСПРЕДЕЛИТЕЛИ СИГНАЛОВ

9.1. Цель работы

Изучить способы построения распределителей сигналов, приобрести навыки проектирования и наладки схем этого класса.

9.2. Краткие теоретические сведения

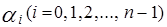

Распределитель сигналов (РС) – это операционный элемент, вырабатывающий выходные сигналы  , принимающие единичные значения в моменты времени

, принимающие единичные значения в моменты времени  соответственно. Специфика применения распределителей сигналов состоит в том, что они обычно используются для построения управляющих, а не операционных автоматов. На РС удобно строить запоминающую часть автомата, работающего по линейной или легко линеаризуемой микропрограмме. При этом с выходов

соответственно. Специфика применения распределителей сигналов состоит в том, что они обычно используются для построения управляющих, а не операционных автоматов. На РС удобно строить запоминающую часть автомата, работающего по линейной или легко линеаризуемой микропрограмме. При этом с выходов  РС снимаются сигналы состояний автомата. Выход

РС снимаются сигналы состояний автомата. Выход  может использоваться для перевода (сброса) РС в состояние

может использоваться для перевода (сброса) РС в состояние  . РС может быть переведен в состояние

. РС может быть переведен в состояние  и специальным управляющим сигналом

и специальным управляющим сигналом  . Состояния РС сменяются последовательно (единица переходит на очередной выход) по синхросигналу

. Состояния РС сменяются последовательно (единица переходит на очередной выход) по синхросигналу  (рисунок 9.1).

(рисунок 9.1).

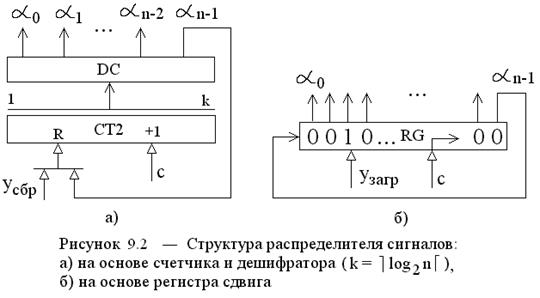

Распределитель сигналов может быть реализован как композиция счетчика и дешифратора (рисунок 9.2,а), а также при помощи регистра сдвига (рисунок 9.2,б).

Распределитель сигналов может быть реализован как композиция счетчика и дешифратора (рисунок 9.2,а), а также при помощи регистра сдвига (рисунок 9.2,б).

Синхросигнал  инициирует микрооперацию счета (увеличение значения счетчика на единицу) – рисунок 9.2,а. Позиционный код состояния счетчика преобразуется дешифратором в унитарный код, расположение единицы в котором соответствует коду в счетчике. Счетчик может быть сброшен в ноль сигналом

инициирует микрооперацию счета (увеличение значения счетчика на единицу) – рисунок 9.2,а. Позиционный код состояния счетчика преобразуется дешифратором в унитарный код, расположение единицы в котором соответствует коду в счетчике. Счетчик может быть сброшен в ноль сигналом  или сигналом на

или сигналом на  -ом выходе дешифратора. Сигнал, равный дизъюнкции указанных сигналов, должен быть подан на вход сброса

-ом выходе дешифратора. Сигнал, равный дизъюнкции указанных сигналов, должен быть подан на вход сброса  счетчика.

счетчика.

Примечание. Если  , то после значения

, то после значения  нулевое значение на счетчике устанавливается автоматически.

нулевое значение на счетчике устанавливается автоматически.

При реализации РС на основе регистра, хранящего унитарный код (рисунок 9.2,б), синхросигнал  инициирует микрооперацию сдвига в регистре. При этом единица сдвигается на очередной выход регистра, а значение освобождающегося нулевого разряда регистра доопределяется значением

инициирует микрооперацию сдвига в регистре. При этом единица сдвигается на очередной выход регистра, а значение освобождающегося нулевого разряда регистра доопределяется значением  -го разряда (организован циклический сдвиг). Таким образом, обеспечивается автоматический переход регистра из состояния

-го разряда (организован циклический сдвиг). Таким образом, обеспечивается автоматический переход регистра из состояния  в состояние

в состояние  . Управляющий сигнал

. Управляющий сигнал  позволяет установить РС в состояние

позволяет установить РС в состояние  путем загрузки в регистр кода 100…0. Состояния РС иногда называют тактами, а сам РС – распределителем тактов, хотя это название не очень удачно.

путем загрузки в регистр кода 100…0. Состояния РС иногда называют тактами, а сам РС – распределителем тактов, хотя это название не очень удачно.

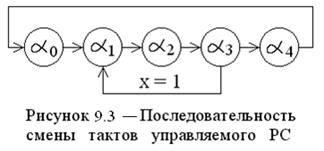

Иногда требуется в зависимости от значения некоторого осведомительного сигнала

Иногда требуется в зависимости от значения некоторого осведомительного сигнала  изменять естественную последовательность смены состояний (тактов). Тогда строят управляемый РС. Например, граф, изображенный на рисунке 9.3 задает распределитель сигналов, вырабатывающий при х=0 циклическую последовательность сигналов α0, α1, α2, α3, α4, α0, α1, α2, α3, α4,..., а при х=1 - α0, α1, α2, α3, α1, α2, α3, α1,.... В общем случае число разветвлений может быть больше одного, но в данной лабораторной работе мы будем использовать графы с одним разветвлением.

изменять естественную последовательность смены состояний (тактов). Тогда строят управляемый РС. Например, граф, изображенный на рисунке 9.3 задает распределитель сигналов, вырабатывающий при х=0 циклическую последовательность сигналов α0, α1, α2, α3, α4, α0, α1, α2, α3, α4,..., а при х=1 - α0, α1, α2, α3, α1, α2, α3, α1,.... В общем случае число разветвлений может быть больше одного, но в данной лабораторной работе мы будем использовать графы с одним разветвлением.

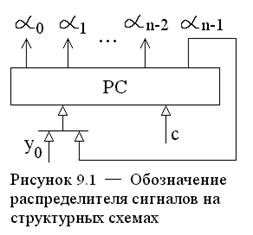

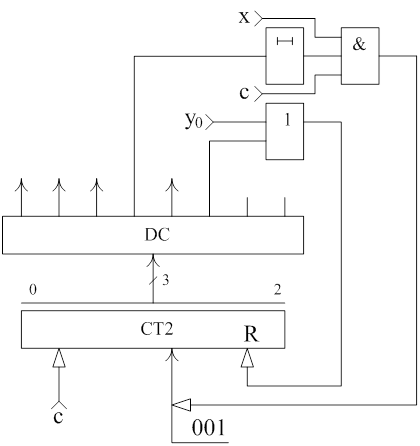

Структурная схема такого РС приведена на рисунке 9.4.

Рисунок 9.4 – Схема управляемого распределителя сигналов

По очередному синхросигналу с код на счетчике увеличивается на 1, а на соответствующем выходе дешифратора появляется активный уровень сигнала, т.е. распределитель переходит в следующее состояние  . Если осведомительный сигнал

. Если осведомительный сигнал  , анализируемый в такте

, анализируемый в такте  , равен нулю, то за состоянием

, равен нулю, то за состоянием  следует состояние

следует состояние  (РС следует по большому циклу – рисунок 9.3). Если осведомительный сигнал

(РС следует по большому циклу – рисунок 9.3). Если осведомительный сигнал  равен 1, то после состояния

равен 1, то после состояния  РС должен вернуться в состояние

РС должен вернуться в состояние  (РС следует по малому циклу). Для осуществления такого перехода используется режим параллельной загрузки счетчика. На входах параллельной загрузки фиксируется код состояния

(РС следует по малому циклу). Для осуществления такого перехода используется режим параллельной загрузки счетчика. На входах параллельной загрузки фиксируется код состояния  (001). Сигнал

(001). Сигнал  переводит счетчик в режим параллельной загрузки. Элемент задержки на рисунке 9.4 должен обеспечивать задержку сигнала

переводит счетчик в режим параллельной загрузки. Элемент задержки на рисунке 9.4 должен обеспечивать задержку сигнала  относительно сигнала

относительно сигнала  на длину синхроимпульса, чтобы распределитель находился в состояние

на длину синхроимпульса, чтобы распределитель находился в состояние  в течение целого такта, а переход в состояние

в течение целого такта, а переход в состояние  произошел в следующем такте. В начальное состояние распределитель переводится либо управляющим сигналом y0, либо активным уровнем сигнала на выходе

произошел в следующем такте. В начальное состояние распределитель переводится либо управляющим сигналом y0, либо активным уровнем сигнала на выходе  .

.

9.3. Содержание работы

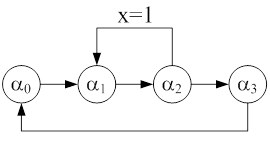

В процессе выполнения лабораторной работы необходимо разработать, собрать и отладить схему управляемого распределителя, формирующего заданную графом последовательность тактовых сигналов. Распределитель сигналов строится на основе счетчика и дешифратора. В качестве примера на рисунке 9.6 изображена принципиальная схема распределителя сигналов, работающего в соответствии с графом смены состояний, приведенном на рисунке 9.5.

Рисунок 9.5 – Граф смены состояний распределителя

сигналов

9.4. Варианты заданий

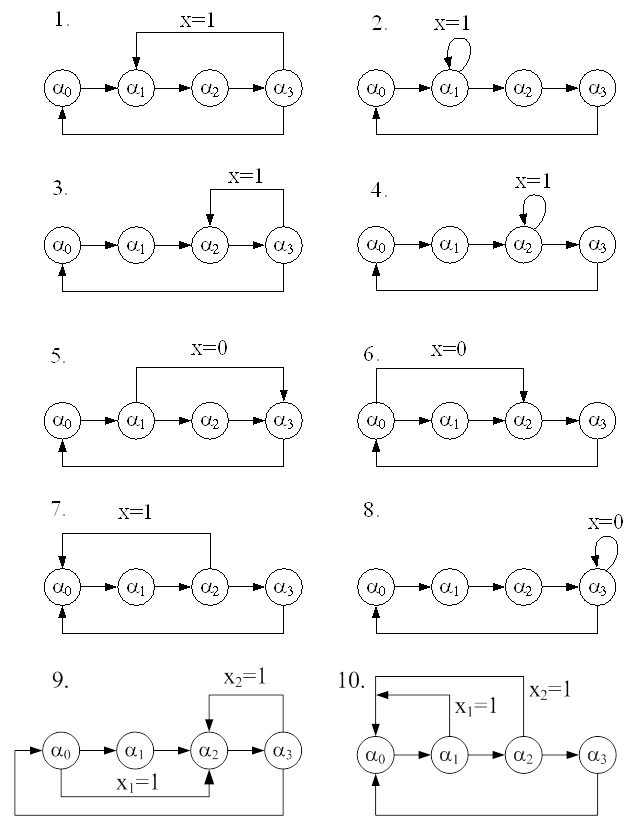

Варианты заданий приведены на рисунке 9.7.

9.5. Внеаудиторная подготовка

9.5.1. Изучить функциональное описание и способы реализации распределителей сигналов: [2], стр. 261-267; [3], стр. 300-315.

9.5.2. Синтезировать схему распределителя сигналов в соответствии с вариантом задания. Распределитель сигналов построить на основе счетчика и дешифратора. Суммирующий счетчик с последовательным переносом реализовать на D-триггерах, имеющихся в составе макета «Trigger». Для построения дешифратора использовать логические элементы макета «Logic». Для обеспечения задержки сигнала  (переводит счетчик в режим параллельной загрузки) относительно сигнала

(переводит счетчик в режим параллельной загрузки) относительно сигнала  (состояние, после которого надо организовать разветвление) на длину синхроимпульса, удобно использовать D-триггер, срабатывающий по инверсному значению синхросигнала, если счетчик срабатывает по прямому значению синхросигнала.

(состояние, после которого надо организовать разветвление) на длину синхроимпульса, удобно использовать D-триггер, срабатывающий по инверсному значению синхросигнала, если счетчик срабатывает по прямому значению синхросигнала.

Рисунок 9.6 – Принципиальная схема управляемого распределителя сигналов, заданного графом, изображенным на рисунке 9.5.

Рисунок 9.7 – Варианты заданий

9.6. Выполнение работы в лаборатории

9.6.1. Собрать схему распределителя сигналов. Значение осведомительного сигнала задать при помощи кнопки.

9.6.2. Отладить схему в статическом режиме, подавая синхросигналы с выхода генератора одиночных импульсов и анализируя состояние схемы с помощью индикаторных лампочек.

9.6.3. Снять с помощью двухлучевого осциллографа временную диаграмму распределителя сигналов, подав на его вход синхросигналы с генератора синхроимпульсов. Определить, по какому фронту синхросигнала осуществляется переключение состояния каждого элемента схемы.

9.7. Контрольные вопросы

9.7.1. Дайте функциональное описание распределителя сигналов. Как он реализуется?

9.7.2. Синтезируйте распределитель сигналов в соответствии с индивидуальным заданием на основе циклического сдвигающего регистра.

9.7.3. Для чего используется триггер в цепях управления сменой состояний счетчика?

9.7.4. Где в компьютере используются распределители сигналов?

10. ЛАБОРАТОРНАЯ УСТАНОВКА «LOGIC-TRIGGER» (L-T)

10.1. Назначение установки

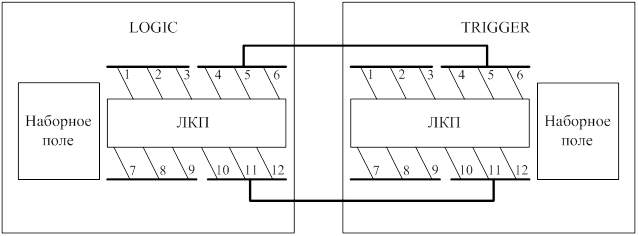

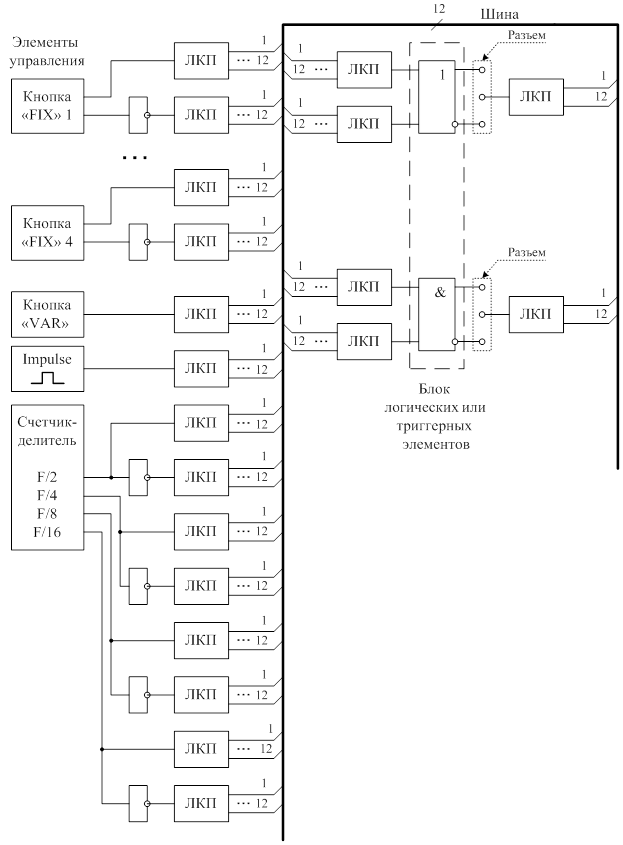

Установка L-T предназначена для изучения методов построения логических схем на потенциальных элементах интегрального комплекса 74HG+. Установка состоит из двух блоков (Logic и Trigger, соединенных шиной, состоящей из шести проводов (рисунок 10.1). Основная часть установки - наборное поле, которое состоит из ряда функциональных и логических элементов. Каждому из этих элементов соответствует условное графическое изображение на лицевой панели установки (рисунок 10.2). Входы и выходы элементов наборного поля выведены локальные коммутационные поля (ЛКП). Схемы устройств собираются с помощью шины путем подключения к ней с помощью ЛКП. Состав наборного поля отдельных блоков:

1. Набор логических (блок Logic) и триггерных (блок Trigger) элементов [6].

2. Кнопочный регистр для задания логических уровней FIX1 –FIX4

3. Генератор синхроимпульсов (Impuls/Generator режимы работы).

4. Генератор одиночных импульсов (режим Impuls).

5. Локальные коммутационные поля (ЛКП), обеспечивающие подключение к шине элементов схемы.

Рисунок 10.1 – Схема установки «LOGIC-TRIGGER» (L-T)

10.2. Логические и триггерные элементы установки

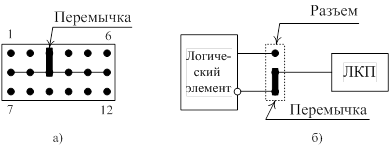

В составе установки имеются логические элементы типа 2И-НЕ, 2И, 3И-НЕ, 3И, 4И-НЕ, 4И, 2ИЛИ-НЕ, 2ИЛИ, 2XOR-НЕ, 2XOR и триггерные элементы типа асинхронных RS и синхронных JK и D-триггеров с установочными инверсными RS-входами. Каждый элемент подключается к шине через ЛКП с помощью перемычки (джампера), которая соединяет вход (выход) с нужным каналом (1,2,…, 12). На рисунке 10.3 приведен пример коммутации одного из выводов логического (триггерного) элемента с линией шины номер 3.

Логические элементы, имеющие как прямой, так и инверсный выход подключаются к ЛКП с помощью разъема. На рисунке 10.3 с помощью разъема и перемычки к ЛКП подключен инверсный выход логического элемента. Каждый вывод элементов наборного поля можно подключить к расположенному рядом светодиодному индикатору.

На незадействованные входы используемых элементов наборного поля должен быть подан потенциал логической «1». Уровень логической «1» может быть выставлен с помощью любой из кнопок «FIX» или кнопки «VAR».

Триггеры типа JK и D, входящие в состав лабораторной установки, используются как элементы памяти.

Триггер типа D может работать в двух режимах: синхронном, при котором управление производится по входу D (при наличии импульсов положительной полярности на входе C), и асинхронном – по RS-входам. Таблица 10.1 - таблица переходов триггера.

Таблица 10.1 – Таблица переходов D-триггера

с установочными RS-входами

|

|

|

|

|

| X | X | Не определено | ||

| X | X | |||

| X | X | |||

| X |

| |||

В таблице 10.1  ,

,  ,

,  ,

,  - сигналы на входах

- сигналы на входах  ,

,  ,

,  ,

,  в момент t; Q(t) - состояние триггера в момент t; Q(t+1) - состояние триггера в момент t+1; X - состояния входов, значения которых не влияют на Q(t+1).

в момент t; Q(t) - состояние триггера в момент t; Q(t+1) - состояние триггера в момент t+1; X - состояния входов, значения которых не влияют на Q(t+1).

Для синхронного входа t и t+1 означают время до и после прихода синхронизирующего импульса. Для организации счетного режима работы триггера необходимо инверсный выход триггера подсоединить к входу D.

Триггер JK-типа также может работать в синхронном и асинхронном режимах. Таблица 10.2 - таблица переходов триггера.

Таблица 10.2 – Таблица переходов JK-триггера

с установочными RS-входами

|

|

|

|

|

|

| X | X | X | Не определено | ||

| X | X | X | |||

| X | X | X | |||

| X | X |

| |||

| |||||

|

В таблице 10.2 J(t),K(t) - сигналы на входах J и K в момент t.

10.3. Кнопочный регистр

В состав наборного поля установки входит 4-разрядный кнопочный регистр (FIX1 – FIX4, рис. 1), который предназначен для задания парафазным кодом логических уровней "1" и "0". Кнопки FIX изменяют состояние (логический уровень) при каждом нажатии.

Рисунок 10.2 – Структурная схема блока логических (LOGIC) или

триггерных (TRIGGER) элементов с элементами управления

10.4. Генератор синхроимпульсов и одиночных импульсов

Кнопка «Impuls-Generator» управляет одновибратором, формирует одиночный импульс длительностью 20 мс. При длительном нажатии кнопки можно переключиться на режим мультивибратора (генератор). Генератор формирует прямоугольные импульсы, которые подаются на счетчик «Counter Output» который работает как делитель частоты. На коммутационных полях F/2, F/4, F/8, F/16 с помощью перемычек устанавливается связь с необходимой линией шины.

10.5. Порядок работы на установке

10.5.1. Произвести коммутацию элементов установки в соответствии с заданной схемой и описанием лабораторной работы.

10.5.2. Получить разрешение преподавателя на проведение эксперимента. Включить питание.

10.5.3. При работе с осциллографом необходимо соединить корпус осциллографа с корпусом установки (гнезда "_|_"), установить на осциллографе режим внешней синхронизации. Сигнальный вход осциллографа соединить с нужной точкой схемы. Коммутация производится специальными шнурами.

10.5.4. После выполнения работы выключить питание, затем разобрать схему. Коммутационные перемычки собрать в специальный контейнер.

Рисунок 10.3 – Элементы коммутации:

а) локальное коммутационное поле (ЛКП);

б) разъем на выходе логического элемента

\

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Апраксин Ю.К. Основы теории и проектирования цифровых автоматов: Учеб. пособие для вузов/Ю.К.Апраксин. – Севастополь: Изд-во СевГТУ, 2001.-345 с.

2. Бабич Н.П. Компьютерная схемотехника. Методы построения и проектирования: учеб. пособие/ Н.П. Бабич, И.А. Жуков. – К.: МК-Пресс, 2004. – 576 с.

3. Потемкин И.С. Функциональные узлы цифровой автоматики/ И.С. Потемкин. – М.: Энергоатомиздат, 1988. – 320 с.

4. Схемотехника электронных систем. Цифровые устройства/ В.И. Бойко, А.Н. Гуржий, В.Я Жуйков и др. – СПб.: БХВ-Петербург, 2004. – 512 с.

5. Цифрова електроніка: методичні вказівки до лабораторних робіт. – Хмельницький: Open System, 2004. – 98 с.

6. Шило В.Л. Популярные цифровые микросхемы: справочник/ В.Л. Шило. – М: Радио и связь, 1988. – 352 с.

Date: 2015-09-05; view: 2309; Нарушение авторских прав