Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Раздельные шины

|

|

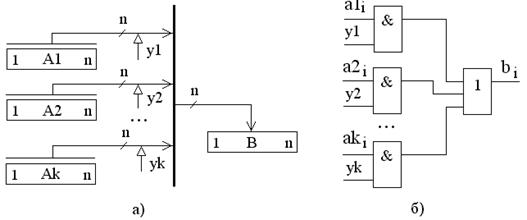

Если необходимо на один регистр-приемник передать информацию с нескольких регистров-источников, то соответствующие цепи объединяются при помощи логических элементов. Пусть на регистр В может передаваться информация с регистров A1, A2, …, Ak:

y1: B(1: n):= A1(1: n);

y2: B(1: n):= A2(1: n);

… …

yk: B(1:n):= Ak(1:n).

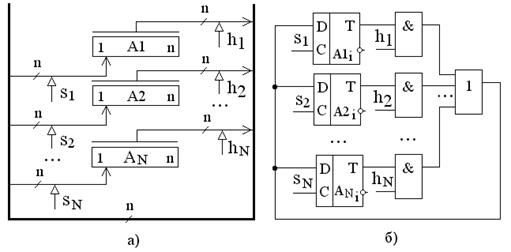

Рисунок 7.5,а иллюстрирует идеологию раздельной шины для осуществления указанных микроопераций. На рисунке 7.5,б приведена схема связей между i-ми разрядами регистров без привязки к конкретной серии микросхем.

Оценим сложность схемы, приведенной на рисунке 7.5,б, по числу входов логических элементов. Для n-разрядных регистров она составит  , где k – количество источников. В общем случае, если в системе не один, а m приемников, сложность схемы составит

, где k – количество источников. В общем случае, если в системе не один, а m приемников, сложность схемы составит  . Если количество передач между регистрами

. Если количество передач между регистрами  в системе достаточно велико, то реализация этих передач раздельными шинами может быть сравнительно дорогой. В связи с этим появилась идея реализации всех передач одной – общей – шиной.

в системе достаточно велико, то реализация этих передач раздельными шинами может быть сравнительно дорогой. В связи с этим появилась идея реализации всех передач одной – общей – шиной.

Рисунок 7.5 – Реализация передач в системе регистров

раздельными шинами: а) структурная схема;

б) функциональная организация для i-го разряда регистров

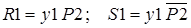

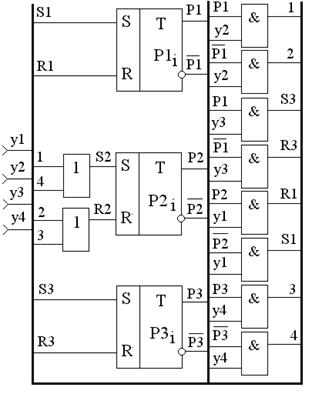

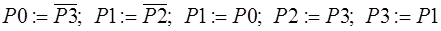

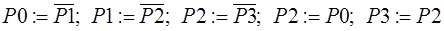

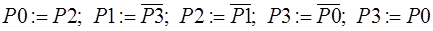

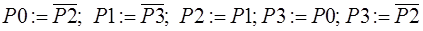

Пример. Синтезировать раздельные парафазные шины (функциональная схема i-го разряда) для осуществления следующих передач в системе из трех регистров:

Парафазные шины применяются, когда приемником является регистр, построенный на RS (JK)-триггерах для того, чтобы межрегистровые передачи могли быть осуществлены за один такт. Поэтому в схеме в качестве i-го разряда каждого регистра будет использован RS-триггер. Для осуществления прямой передачи на S-вход приемника должно быть передано прямое значение источника, домноженное на соответствующий управляющий сигнал, а на R-вход приемника – инверсное значение источника, домноженное на тот же сигнал.

Для осуществления инверсной передачи на S-вход приемника должно быть передано инверсное значение источника, домноженное на соответствующий управляющий сигнал, а на R-вход приемника – прямое значение источника, домноженное на тот же сигнал.

Функции возбуждения входов триггеров:

;

;

;

;

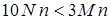

Функциональная схема i-го разряда раздельных шин, осуществляющих заданные передачи, приведена на рисунке 7.6. Схема выполнена без привязки к конкретной серии микросхем.

Рисунок 7.6 – Реализация передач в системе

регистров раздельными шинами

Общая шина (магистраль)

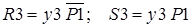

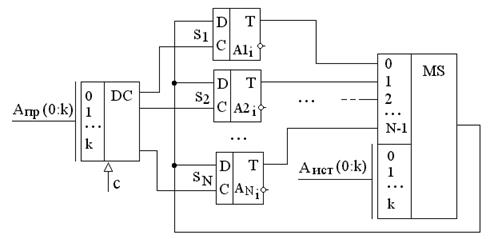

Структурная схема общей шины приведена на рисунке 7.7,а. Функциональная схема i-го разряда общей шины приведена на рисунке 7.7,б.

Рисунок 7.7 – Реализация межрегистровых передач общей шиной:

а) структурная схема общей шины;

б) функциональная схема i-го разряда общей шины

При осуществлении передачи Ak:=Aj через общую шину выход источника подключается ко входу общей по сигналу hj, выход общей шины подключается ко входу приемника по сигналу sk. Для осуществления указанной передачи управляющие сигналы hj и sk должны быть поданы в схему одновременно. Это значит что для осуществления любой передачи управляющий автомат должен выработать два соответствующих этой передаче унитарных кода:

и

и  . То есть управление в данном случае осуществляется унитарными управляющими кодами. Часто на практике УА для осуществления передачи по общей шине вырабатывает позиционные коды номера источника и номера приемника (управление позиционными управляющими кодами). В этом случае выбор источника и подключение его ко входу общей шины осуществляется посредством мультиплексора, подключением нужного приемника ко входу общей шины управляет дешифратор (рисунок 7.8).

. То есть управление в данном случае осуществляется унитарными управляющими кодами. Часто на практике УА для осуществления передачи по общей шине вырабатывает позиционные коды номера источника и номера приемника (управление позиционными управляющими кодами). В этом случае выбор источника и подключение его ко входу общей шины осуществляется посредством мультиплексора, подключением нужного приемника ко входу общей шины управляет дешифратор (рисунок 7.8).

Следует отметить, что в рассмотренных схемах общих шин (рисунки 7.7, 7.8) передаются только прямые значения с регистров-источников. Если в системе возможны передачи инверсных значений, то число источников увеличивается в общем случае в два раза (так как будут использоваться не только прямые, но и инверсные выходы триггеров). В дальнейшем под источником будем понимать номер регистра и тип передачи (прямая или инверсная).

Сравнение общей и раздельной шины.

1) По быстродействию. Более производительными считаются раздельные шины, так как они позволяют совместить некоторые передачи в одном такте. Передачи у1: A:=B и y2: C:=D могут производиться одновременно (но не у1: А:=B и у2: С:=А).

Рисунок 7.8 – Схема i-го разряда общей шины, управляемой

позиционными кодами номера (адреса) источника (Аист) и

номера (адреса) приемника (Апр);

2) По стоимости. Стоимость общей шины, изображенной на рисунке 23,  . Если реализовать дополнительно все возможные инверсные передачи, то стоимость общей шины станет равна

. Если реализовать дополнительно все возможные инверсные передачи, то стоимость общей шины станет равна  . Такой ценой можно организовать любую передачу в системе из N n-разрядных регистров. Цена раздельной шины возрастает с увеличением количества передач:

. Такой ценой можно организовать любую передачу в системе из N n-разрядных регистров. Цена раздельной шины возрастает с увеличением количества передач:  , где

, где  - количество передач,

- количество передач,  - количество источников,

- количество источников,  - количество приемников. Общая шина будет дешевле раздельной, когда

- количество приемников. Общая шина будет дешевле раздельной, когда  . Раздельные шины в операционных автоматах применяют, если регистры слабо связаны (передач между регистрами мало) и важно быстродействие.

. Раздельные шины в операционных автоматах применяют, если регистры слабо связаны (передач между регистрами мало) и важно быстродействие.

3) По степени универсальности (настраиваемости на конкретную микропрограмму).

Общая шина – универсальное решение, пригодное для любой микропрограммы. Раздельную шину необходимо проектировать для каждой конкретной микропрограммы.

7.3. Содержание работы

В процессе выполнения работы необходимо построить таблицы истинности для мультиплексора, подключающего к общей шине 8 источников и демультиплексора, обеспечивающего передачу информации от шины к одному из 4 приемников, экспериментально проверить работу указанных операционных элементов на макете. Разработать схему i-го разряда общей шины для осуществления всех возможных передач данных в системе, состоящей из четырех регистров, и схему i-го разряда раздельной шины для осуществления передач, предусмотренных вариантом задания. Сравнить схемы по сложности и быстродействию.

7.4. Варианты индивидуальных заданий

Варианты индивидуальных заданий приведены в таблице 7.5.

Таблица 7.5

| № варианта | Реализуемые передачи данных | Тип триггера |

| JK | |

| D | |

| RS | |

| D | |

| JK |

7.5. Внеаудиторная подготовка к работе

7.5.1. Изучить классификацию дешифраторов. Мультиплексоров и демультиплексоров, методы их проектирования и схемы реализации [1], стр. 173-178, [2], стр. 141-157, [4], стр. 110-132.

7.5.2. Изучить описание микросхем серий ТТЛ-логики (К155, 74НС). По описаниям микросхем построить таблицы их функционирования.

7.5.3. Построить схемы реализации дешифратора и мультиплексора, необходимые для выполнения индивидуального задания на макете.

7.5.4. Разработать схему передачи данных (i-ый разряд) в системе регистров в соответствии с индивидуальным заданием. Для этого требуется синтезировать общую шину. Номера источников и приемников информации задаются в виде двоичных кодов. Передача информации синхронизируется синхроимпульсами. На входе шины используется мультиплексор, на адресные входы которого подается номер источника информации. Информация по адресам приемников распределяется с помощью демультиплексора. В случае, если выход шины подключается ко всем входам D-триггеров регистров, которые могут принимать информацию, то достаточно однофазного сигнала. Если прием информации осуществляется на триггеры с RS или JK-входами, необходимо организовать парафазный сигнал с выхода шины.

7.5.5. Разработать схему і-го разряда раздельной шины для осуществления заданных передач. Сравнить с предыдущей схемой по сложности и быстродействию.

7.6. Выполнение работы в лаборатории

7.6.1. Собрать схему дешифратора (2 входа на 4 выхода). Соединив его входы с кнопочным регистром, провести эксперимент и сравнить экспериментальные данные с теоретическими. Аналогичный эксперимент провести с шифратором.

7.6.2. По аналогии с предыдущим пунктом собрать и исследовать схемы мультиплексора и демультиплексора с двумя адресными входами.

7.7. Контрольные вопросы

7.7.1. Сравнить по быстродействию и сложности различные структуры дешифраторов.

7.7.2. Как построить сеть из дешифраторов с заданным количеством входов с целью увеличения разрядности дешифрируемого кода?

7.7.3. Что такое мультиплексор? Как с помощью мультиплексора реализовать произвольную булеву функцию?

7.7.4. Как подключить к общей шине n двоичных сигналов, если n>k, где k – число информационных входов мультиплексора?

7.7.5. Где в компьютере используются мультиплексоры и дешифраторы. Привести примеры.

7.7.6. Приведите формулы для оценки сложности общей и раздельной шины.

8. ЛАБОРАТОРНАЯ РАБОТА № 7. ДВОИЧНЫЕ СУММАТОРЫ

8.1. Цель работы

Изучить методы проектирования и схемные реализации одноразрядных сумматоров, получить навыки сборки, наладки и использования схем двоичных сумматоров, приобрести опыт работы с сумматорами в интегральном исполнении.

8.2. Краткие теоретические сведения

Сумматор – это операционный элемент, предназначенный для выполнения микрооперации сложения чисел. Если операнды и результат сложения представляются в двоичной системе счисления, то сумматор называется двоичным. Сумматоры подразделяются на два типа: комбинационные и накапливающие. Комбинационные сумматоры не содержат запоминающих элементов и реализует микрооперацию сложения в виде C:=A+B. Накапливающие сумматоры содержат регистр, на котором перед началом микрооперации хранится слагаемое и на момент окончания сложения – сумма. Накапливающие сумматоры реализуют микрооперацию сложения в виде С:=С+А.

Структура сумматоров зависит от типа используемых логических и запоминающих элементов и ограничений, налагаемых на длительность микрооперации сложения или количество оборудования.

Операционное устройство может производить арифметические и логические операции в соответствии с заложенной в его основу микропрограммой параллельно, последовательно и параллельно-последовательно. Параллельный способ выполнения операции суммирования двух чисел с фиксированной точкой предполагает, что микрооперация сложения, используемая в микропрограмме суммирования, выполняется над всеми разрядами операндов одновременно (параллельно). Последовательный способ выполнения операции суммирования означает, что соответствующая микрооперация сложения выполняется последовательно над каждым i-ым разрядом суммируемых чисел, начиная с младшего. Поэтому для осуществления сложения двух  -разрядных чисел на последовательном двоичном сумматоре потребуется

-разрядных чисел на последовательном двоичном сумматоре потребуется  тактов суммирования (потери времени при этом компенсируются существенной экономией аппаратуры). Компромиссным способом является параллельно-последовательный способ выполнения сложения на двоичном сумматоре. Он предполагает, что микрооперация сложения выполняется над

тактов суммирования (потери времени при этом компенсируются существенной экономией аппаратуры). Компромиссным способом является параллельно-последовательный способ выполнения сложения на двоичном сумматоре. Он предполагает, что микрооперация сложения выполняется над  разрядами суммируемых чисел (т.е.

разрядами суммируемых чисел (т.е.  разрядов суммируются параллельно),

разрядов суммируются параллельно),  ,

,  кратно

кратно  . При этом в микропрограмме сложения должна быть предусмотрена микрооперация сдвига регистра, на который записывается сумма, на

. При этом в микропрограмме сложения должна быть предусмотрена микрооперация сдвига регистра, на который записывается сумма, на  разрядов вправо для того, чтобы освободить место для записи суммы следующих по старшинству

разрядов вправо для того, чтобы освободить место для записи суммы следующих по старшинству  разрядов суммируемых слов.

разрядов суммируемых слов.

На микрооперации сложения основаны алгоритмы (микропрограммы) выполнения основных арифметических операций в арифметико-логическом устройстве (сложение, вычитание, умножение, деление). Три перечисленных способа выполнения суммирования слов на соответствующих операционных элементах применимы и к выполнению поразрядных логических операций над словами. В соответствии с вышесказанным, арифметико-логические устройства компьютера по способу выполнения операций делятся на параллельные, последовательные и параллельно-последовательные.

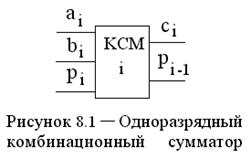

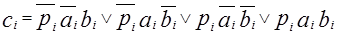

Параллельный комбинационный сумматор с последовательным переносом. При построении применяется стандартный метод – синтез типового разряда. N-разрядный параллельный сумматор с последовательным переносом строится из n одноразрядных комбинационных сумматоров (ОКСм). Функция одноразрядного комбинационного сумматора (рисунок 8.1) представлена в таблице 8.1.

Параллельный комбинационный сумматор с последовательным переносом. При построении применяется стандартный метод – синтез типового разряда. N-разрядный параллельный сумматор с последовательным переносом строится из n одноразрядных комбинационных сумматоров (ОКСм). Функция одноразрядного комбинационного сумматора (рисунок 8.1) представлена в таблице 8.1.

Таблица 8.1

| Номер входного набора | Входы | Выходы | |||

|

|

|

|

| |

Схема, изображенная на рисунке 1, суммирует ai и bi - значения i-ых разрядов слов А(1:n) и B(1:n) – а также pi - перенос в i-ый разряд суммы из младшего (i+1)-го разряда.

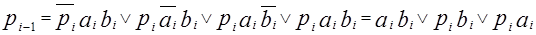

Из таблицы 8.1 получены следующие функции для определения выходных сигналов ОКС.

Значение i-го разряда суммы:

;

;

Значение переноса в старший (i-1)-ый разряд суммы:

По этим функциям строится двухуровневый двоичный одноразрядный комбинационный сумматор с ценой 25 (входов логических элементов) и временем задержки  , где

, где  - задержка на логическом элементе.

- задержка на логическом элементе.

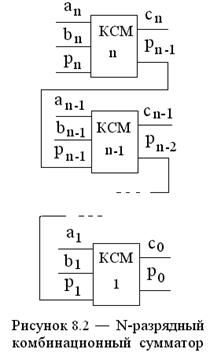

Схема n-разрядного комбинационного сумматора, построенного на базе ОКС представлена на рисунке 8.2.

Схема n-разрядного комбинационного сумматора, построенного на базе ОКС представлена на рисунке 8.2.

В данном сумматоре сигналы переносов распространяются последовательно от младших разрядов к старшим. По этой причине указанный сумматор называется сумматором с последовательным переносом. Длительность микрооперации сложения определяется суммой времени распространения переносов и времени формирования суммы в одном разряде:

,

,

где L – максимальная длина переноса, равная числу соседних разрядов, через которые распространяется сигнал переноса при выполнении сложения,  - небольшой запас времени для надежности. При наличии переноса между всеми разрядами сумматора (например, при сложении чисел A=11…11 и B= 00…01 перенос формируется в младшем разряде сумматора и проходит через все остальные разряды)

- небольшой запас времени для надежности. При наличии переноса между всеми разрядами сумматора (например, при сложении чисел A=11…11 и B= 00…01 перенос формируется в младшем разряде сумматора и проходит через все остальные разряды)  , и длительность микрооперации сложения составляет

, и длительность микрооперации сложения составляет

Поскольку фактическое время распространения переноса в схеме рисунка 8.2 не определяется, то для выполнения микрооперации сложения отводится такт, длительность которого определяется максимальным временем распространения переносов.

Методы ускорения микрооперации сложения

Случай сложения с наличием переносов между всеми разрядами сумматора достаточно маловероятен. Доказано, что в n-разрядном сумматоре, на вход которого поступают слагаемые, равномерно распределенные в интервале  , средняя длина самого длинного переноса, затрагивающего группу соседних разрядов, не превышает

, средняя длина самого длинного переноса, затрагивающего группу соседних разрядов, не превышает  . Так, в 32-х разрядном сумматоре переносы пробегают в среднем не более чем через 5 соседних разрядов. Если в сумматор встроить схему, определяющую момент окончания сложения, то время сложения уменьшается в

. Так, в 32-х разрядном сумматоре переносы пробегают в среднем не более чем через 5 соседних разрядов. Если в сумматор встроить схему, определяющую момент окончания сложения, то время сложения уменьшается в  раз. Сумматор, в котором вырабатывается осведомительный сигнал, отмечающий окончание сложения, называется асинхронным сумматором.

раз. Сумматор, в котором вырабатывается осведомительный сигнал, отмечающий окончание сложения, называется асинхронным сумматором.

Еще одним методом уменьшения длительности микрооперации сложения является использование сумматора с групповым переносом. Сумматор делится на  групп, каждая из которых содержит

групп, каждая из которых содержит  соседних разрядов. В сумматор вводятся цепи, ускоряющие процесс распространения переносов между группами и в пределах каждой группы.

соседних разрядов. В сумматор вводятся цепи, ускоряющие процесс распространения переносов между группами и в пределах каждой группы.

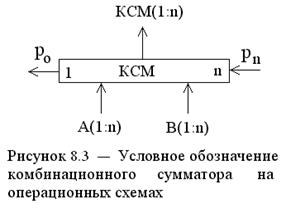

Комбинационные сумматоры независимо от их внутренней структуры обозначаются на операционных (структурных) схемах как представлено на рисунке 8.3. Если перенос в младший разряд сумматора всегда равен нулю, то вход

Комбинационные сумматоры независимо от их внутренней структуры обозначаются на операционных (структурных) схемах как представлено на рисунке 8.3. Если перенос в младший разряд сумматора всегда равен нулю, то вход  на операционных схемах не обозначается. Если перенос из старшего разряда сумматора никак не используется (теряется), то выход

на операционных схемах не обозначается. Если перенос из старшего разряда сумматора никак не используется (теряется), то выход  также не обозначается. Выход

также не обозначается. Выход  может быть использован для увеличения разрядности сумматора (тогда он подается на вход

может быть использован для увеличения разрядности сумматора (тогда он подается на вход  следующего (старшего) сумматора). При сложении чисел в обратных кодах в сумматоре организуется цепь циклического переноса путем подсоединения выхода

следующего (старшего) сумматора). При сложении чисел в обратных кодах в сумматоре организуется цепь циклического переноса путем подсоединения выхода  (старшего сумматора, если необходимую разрядность обеспечивают несколько сумматоров) ко входу

(старшего сумматора, если необходимую разрядность обеспечивают несколько сумматоров) ко входу  (младшего сумматора).

(младшего сумматора).

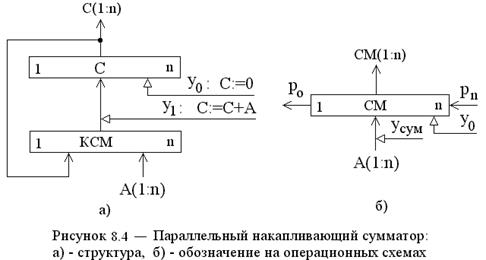

Накапливающие сумматоры

В накапливающем сумматоре значение суммы вычисляется путем сложения предыдущего ее значения со слагаемым, т.е. микрооперация сложения выполняется в виде  . Для присваивания сумме начального значения в накапливающем сумматоре обычно реализуется операция установки

. Для присваивания сумме начального значения в накапливающем сумматоре обычно реализуется операция установки  . Накапливающий сумматор можно рассматривать как композицию регистра, используемого для хранения значения

. Накапливающий сумматор можно рассматривать как композицию регистра, используемого для хранения значения  и комбинационного сумматора

и комбинационного сумматора  , вычисляющего сумму

, вычисляющего сумму  . Структурная схема параллельного накапливающего сумматора изображена на рисунке 8.4,а, условное обозначение на операционных схемах – на рисунке 8.4,б.

. Структурная схема параллельного накапливающего сумматора изображена на рисунке 8.4,а, условное обозначение на операционных схемах – на рисунке 8.4,б.

Время такта суммирования в данном случае определяется задержкой комбинационного сумматора и временем приема значения суммы на регистр.

Date: 2015-09-05; view: 1045; Нарушение авторских прав