Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Дешифраторы

|

|

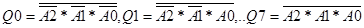

Дешифратором (ДШ) чаще всего называют устройство, преобразующее двоичный код в унарный. Из всех m выходов дешифратора активный уровень имеется только на одном, а именно на том, номер которого равен поданному на вход двоичному числу. На всех остальных выходах ДШ уровни напряжения неактивные. Обычно ДШ имеют инверсные выходы. При этом на выбранном выходе 0, а на всех остальных "1". Унарный код называют еще кодом " 1 из m ". Условное изображение ДШ с инверсными выходами показано на рис. 3.1,а. О входе Е будет сказано ниже.

Если ДШ имеет n входов, m выходов и использует все возможные наборы входных переменных, то m=2n. Такой ДШ называют полным.

ДШ используют, когда нужно обращаться к различным ЦУ, и при этом номер устройства – его адрес – представлен двоичным кодом.

Адресные входы ДШ обозначают обычно А0, А1, А2,..А(n-1), где индекс буквы А означает показатель степени 2. Иногда эти входы просто нумеруют в соответствии с весами двоичных разрядов: 1, 2, 4, 8, 16,..2n-1.

Формально описать работу ДШ можно, задав список функций, обрабатываемых каждым из его выходов. Так для ДШ (рис. 3.2,а)

Реализация этих восьми выражений с помощью восьми трехвходовых ЛЭ 3И-НЕ дает наиболее простой по структуре ДШ, называемый линейным.

Рис. 3.1. Дешифратор "1 из 8" с инверсными выходами.

Основной объем оборудования линейного ДШ составляют в общем случае m n- входовых элементов И-НЕ для ДШ с инверсными выходами или m n -входовых элементов И для ДШ с прямыми выходами. Кроме того, требуется n инверторов входных переменных и n буферных инверторов, назначение которых – свести к единице кратность нагрузки, которую представляет ДШ для источника сигнала. Иначе каждый источник будет нагружен на m/2 входов элементов И-НЕ или И.

ДШ с прямыми и инверсными выходами можно построить, соответственно, на ЛЭ ИЛИ-НЕ и ИЛИ. Общее число ЛЭ при этом не изменится.

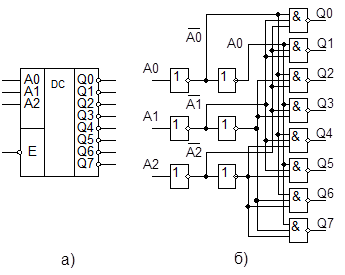

Дешифраторы обычно имеют разрешающий вход Е (от enable – давать возможность).

Вход Е часто выполняют инверсным, тогда при Е=0 ДШ работает как обычно, а при Е=1 на всех выходах устанавливаются неактивные уровни независимо от поступившего кода адреса.

|

На рис. 3.2, а показан вариант построения разрешающего входа, когда сигнал Е воздействует непосредственно на все дешифрирующие ЛЭ. Этот вариант требует увеличения на единицу числа входов у дешифрирующих ЛЭ, но не вносит дополнительной задержки. На рис. 3.2, б показан другой вариант, основанный на том, что, как видно из рис. 3.1, б, в ДШ не найдется ни одного дешифрирующего ЛЭ, к которому любая переменная не была бы подключена или в своей прямой, или в инверсной форме. Поэтому если и в прямой, и в инверсной тракты любой входной переменной поставить элементы 2И и завести на них сигнал Е, то при Е=0 будут заперты абсолютно все коньюнкторы, подключенные к выходам. Такой способ экономичен по оборудованию, но увеличивает задержку дешифратора.

Рис. 3.2. Разрешающий вход дешифратора.

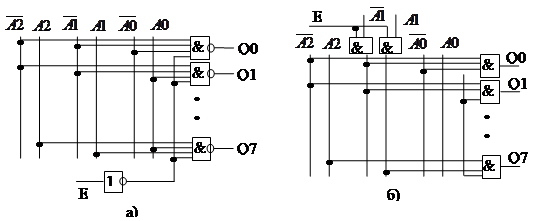

На рис. 3.3 показана группа из пяти ДШ, соединенных в два каскада. Вся группа работает как дешифратор "1 из 32". Два старших разряда адреса А4 и А3 расшифровываются дешифратором "1 из 4" DC4, который по входам Е управляет четырьмя дешифраторами "1 из 8" второго каскада. Младшие разряды адреса А2, А1, А1 поступают на все ДШ второго каскада, но выбранным по входу Е оказывается лишь один из них. Ему и будут принадлежать единственный из всех 32 активный выход. Так при поступлении кода А4А3А2А1А0=01111 у DC4 активный сигнал ("0") появится на выходе Q1, и по входу Е будет выбран DC1. Остальным дешифраторам второго каскада работа запрещена. Разряды адреса А2А1А0=101 вызовут появление активного сигнала на выходе Q7 DC1, т.е. на выходе Q15 всего составного ДШ, что соответствует заданному адресу. Принцип используется при построении ДШ на много выходов из микросхем ДШ с меньшим числом выходов.

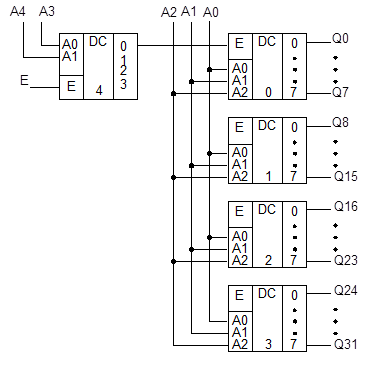

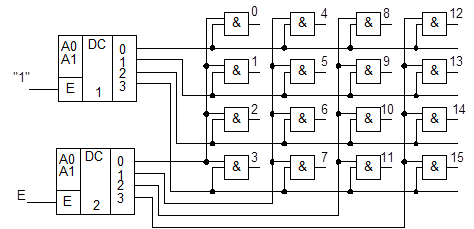

На рис. 3.4 показан двухкаскадный ДШ "1 из 16", второй каскад которого собран по схеме координатного или матричного ДШ. Разряды адреса разбиты на две группы.

Рис. 3.3 Каскадное соединение дешифраторов

каждая из которых независимо от другой расшифровывается своим дешифратором первого каскада DC1 и DC2. При любой комбинации значений входных переменных оказываются выбранными одна строка и один столбец сетки, в узлах которой расположены элементы 2И второй ступени. В результате каждый адресный набор возбуждает выход единственного соответствующего ему элемента 2И.

При использовании во второй ступени элементов 2И-НЕ выходы ДШ будут инверсными. Их можно сделать прямыми, построив координатную сетку на элементах 2ИЛИ-НЕ; тогда инверсными должны быть выходы дешифраторов первого каскада.

Делить разряды адреса между DC1 и DC2 нужно по возможности поровну: чем ближе прямоугольник второго каскада к квадрату, тем при том же числе выходных элементов 2И меньше сумма его строк и столбцов, т.е. меньше число выходов дешифраторов первого каскада. В качестве входа E всего двухкаскадного ДШ удобно использовать разрешающий вход одного из дешифраторов первого каскада. При этом запираются или все строки, или все столбцы.

|

Целесообразно сравнить три рассмотренных типа дешифраторов по величине задержки и аппаратным затратам. Задержка минимальна для линейного ДШ и в пределе может быть равна (2¸3)t в зависимости от числа ступеней инверторов-усилителей. При включении линейных ДШ в несколько каскадов задержки всех каскадов складываются. Чем больше выходов ДШ, тем большая доля оборудования сосредоточена в элементах И самого последнего каскада. Число ЛЭ предпоследнего каскада уже в несколько раз меньше, а предыдущих – тем более. Число элементов И последнего каскада ДШ любого типа всегда равно числу его выходов, поэтому в первом приближении аппаратные затраты ДШ различных типов соотносятся как аппаратные затраты их элементов И последнего каскада. Они и определяют основную разницу: у линейного ДШ число входов каждого элемента И последнего (и единственного) каскада равно числу адресных входов n, у каскадного оно зависит от способа разбиения на группы, однако оно всегда меньше n, но больше двух, у прямоугольного оно равно двум – минимально мозможному числу. Поэтому при большом числе выходов (сотни и более) прямоугольный ДШ – самый экономичный по оборудованию, чем и объясняется его широкое применение в БИС памяти. При уменьшении числа выходов до каскадных десятков экономичнее каскадные ДШ, а при малом числе выходов самым экономичным (а к тому же и самым быстрым) оказывается линейный ДШ.

Приведенные оценки справедливы лишь для ДШ, построенных непосредственно из ЛЭ. При проектировании же блоков из готовых микросхем, когда затраты оборудования оцениваются не числом элементов, а числом корпусов, даже большие ДШ экономичнее строить по каскадному принципу, набирая их из микросхем небольших ДШ на 8 или 16 выходов.

Дешифраторы, выпускаемые в виде отдельных микросхем, имеют буквенное обозначние ИД. В сериях ТТЛ, в которых элементы И-НЕ наиболее технологичны, ДШ обычно имеют инверсные выходы. В КМОП-сериях, где элементы ИЛИ-НЕ не менее технологичны, чем И-НЕ, ДШ чаще имеют прямые выходы. Стремление полнее использовать выводы типовых DIP-корпусов определяет размеры ДШ, выпускаемых в виде средних интегральных схем (СИС). Обычно это дешифраторы “1 из 8”, ”1 из 10”, сдвоенный ”1 из 4”, а также ”1 из 16”, но уже в корпусе DIP24.

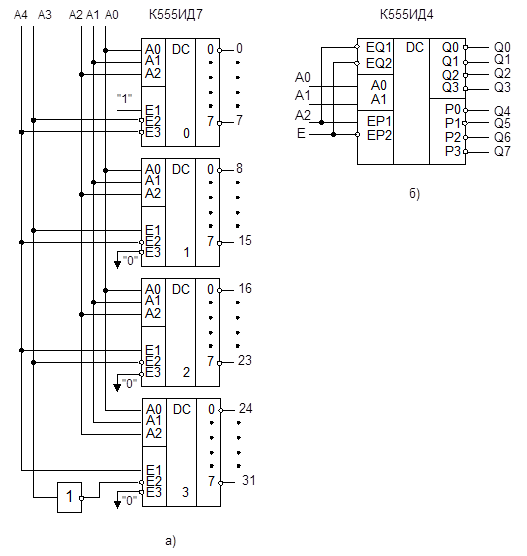

Часто в микросхемах ДШ делают несколько разрешающих входов, а разрешающей комбинацией является их конъюнкция. При этом удобно наращивать ДШ, используя каскадный принцип и строя первый каскад дешифрации не на отдельном специальном ДШ, а собирая его из конъюнкторов разрешающих входов. На рис. 3.5, а таким способом построен ДШ ”1 из 32” из четырех микросхем К555ИД7 ”1 из 8”. Каждая микросхема имеет по три разрешающих входа (два инверсных и один прямой). Разрешение существует лишь тогда, когда одновременно на инверсных входах ”нули”, а на прямом ”единица”.

В микросхему К555ИД4 входят два ДШ ”1 из 4” с общими адресными входами А1 и А0. Каждый ДШ имеет пару разрешающих входов. У верхнего по схеме (рис. 3.5,б) ДШ два инверсных входа EQ1 и EQ2, у нижнего – один прямой – EP1, и один инверсный – EP2. Это позволяет, объединив EQ1 и EP1 и подав на эту пару третий разряд адреса А2, использовать эту микросхему как ДШ ”1 из 8”.

В микроэлектронике очень распространена тенденция выпускать микросхемы, способные выполнять несколько различных функций: это увеличивает спрос на микросхемы, а рост выпуска способствует снижению стоимости.

Рис. 3.5 Использование разрешающих входов микросхем дешифраторов

а) – на разрешающих входах построена первая ступень каскадного ДШ;

б) – универсальная микросхема дешифраторов 2x”1 из 4” и “1 из 8”.

Разрешающие входы ДШ используются и при размещении ДШ в адресном пространстве системы. На практике число адресатов, адреса которых дешифрируются ДШ, значительно меньше, чем адресное пространство, т.е. общее количество адресатов, которое может быть размещено в системе. Это число определяется разрядностью n шины адреса (ША) и равно Q = 2n.

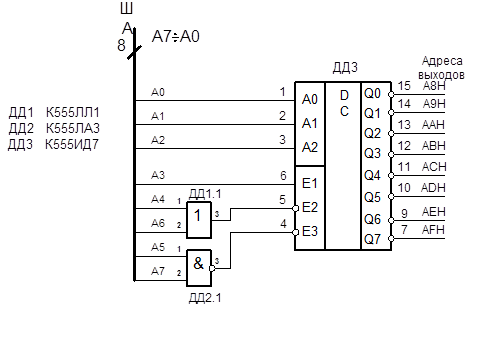

Пример. На микросхеме К155ИД7 построить ДШ адресов B8H – BFH в системе с n = 8.

Запишем начальный и конечный адреса диапазона в двоичном коде:

A7A6A5A4A3 A2A1A0

А нач = B8H = 1 0 1 0 1 0 0 0 B

……………………………………

A кон = BFH = 1 0 1 0 1 1 1 1 B

Выбор ДШ Выбор выхода ДШ

Нетрудно видеть, что старшие 5 разрядов адреса (одинаковые для всех 8 адресатов) определяют их положение в адресном пространстве. Следовательно, только при такой комбинации на входы ДШ E1, E2, E3 должны быть поданы “1”, ”0”, ”0”, соответственно (Рис.3.8.).

|

Рис.3.8. Дешифратор адресов A8H – AFH

Date: 2015-05-09; view: 896; Нарушение авторских прав