Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Что такое схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ?

|

|

С х е м а И

Схема И реализует конъюнкцию двух или более логических значений.

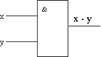

Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис. 1. Таблица истинности — в таблице 1.

Рис. 1 Таблица 1

Рис. 1 Таблица 1

| x | y | X Y |

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x*y (читается как " x и y").

Операция конъюнкции на функциональных схемах обозначается знаком “&” (читается как "амперсэнд"), являющимся сокращенной записью английского слова and.

С х е м а ИЛИ

Схема ИЛИ реализует дизъюнкцию двух или более логических значений.

Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

Знак “1” на схеме — от устаревшего обозначения дизъюнкции как ">=1" (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y (читается как " x или y "). Таблица истинности — в табл. 2.

Таблица 2

| x | y | x v y |

С х е м а НЕ

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом x этой схемы и выходом z можно записать соотношением z =  , где

, где  читается как " не x " или " инверсия х ".

читается как " не x " или " инверсия х ".

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение инвертора — на рисунке 3, а таблица истинности — в табл. 3.

Рис. 3 Таблица.3

Рис. 3 Таблица.3

| x |

|

С х е м а И - НЕ

Схема И-НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И.

Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  читается как " инверсия x и y ".

читается как " инверсия x и y ".

Таблица истинности схемы И-НЕ — в табл. 4.

Таблица 4

| x | y |

|

С х е м а ИЛИ - НЕ

Схема ИЛИ-НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ.

Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  , читается как " инверсия x или y ". 0Таблица истинности схемы ИЛИ-НЕ — в табл. 5.

, читается как " инверсия x или y ". 0Таблица истинности схемы ИЛИ-НЕ — в табл. 5.

Таблица 5

| x | y |

|

Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис.6.

Рис.6

Рис.6

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал Q является логическим отрицанием сигнала

, причем выходной сигнал Q является логическим отрицанием сигнала  .

.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов ( ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис.7 показана реализация триггера с помощью вентилей ИЛИ-НЕ и соответствующая таблица истинности.

Рис.7

Рис.7

| S | R | Q |

|

| запрещено | |||

| хранение бита |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ-НЕ (табл. 6).

- Если на входы триггера подать S=“1”, R=“0”, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=“0”, Q=“0” и выход

станет равным “1”.

станет равным “1”. - Точно так же при подаче “0” на вход S и “1” на вход R на выходе

появится “0”, а на Q — “1”.

появится “0”, а на Q — “1”. - Если на входы R и S подана логическая “1”, то состояние Q и

не меняется.

не меняется. - Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 • 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

Задание:

Вариант 1

Вариант 1

2. not (a and not B) or C

3. JK-триггер на элементах И-НЕ.

Вариант 2

Вариант 2

2. not (not A or B and not C)

3. RS-триггера на элементах И-НЕ.

Вариант 3

2. not (А and not B) or C

3. D-триггер на элементах И-НЕ.

Вариант 4

2. A or not (not B and C)

3. T-триггер на элементах И-НЕ.

Вариант 5

|

- not(not A or B or C)

- Двухтактный RS-триггера на элементах И-НЕ.

Порядок выполнения работы:

- По заданной логической схеме составить логическое выражение и заполнить для него таблицу истинности, нарисовать временную диаграмму входных и выходных сигналов.

- По заданному логическому выражению составить логическую схему и построить таблицу истинности, нарисовать временную диаграмму входных и выходных сигналов

- Нарисовать схему триггера, его условно-графическое обозначение. Построить таблицу истинности

Контрольные вопросы:

- Перечислите элементарные логические функции

- Назовите базовые логические элементы

- Что такое таблица истинности?

- Что такое регистр?

- Дайте определение понятию триггер?

- Какие виды триггеров вы знаете?

Отчет должен содержать:

- Логические схемы для каждого задания

- Логические выражения

- Ответы на контрольные вопросы.

| <== предыдущая | | | следующая ==> |

| орытынды | | | Саратов-2011 |

Date: 2015-10-19; view: 616; Нарушение авторских прав