Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Параллельный обмен

|

|

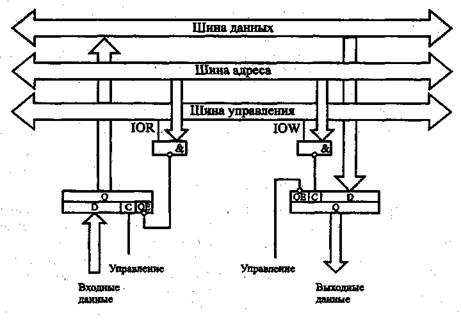

Простейшая подсистема параллельного обмена должна обеспечить лишь дешифрацию адреса ВУ и электрическое подключение данных ВУ к системной шине данных DB по соответствующим управляющим сигналам. На рис. 6.7 показаны устройства параллельного ввода и вывода информации в составе МПС на базе буферных регистров К580ИР82.

Очевидно, при обращении процессора (он в подобных циклах играет роль активного устройства) к устройству ввода, адрес соответствующего регистра помещается процессором на шину адреса и формируется управляющий сигнал RDIO. Дешифратор адреса, включающий и линию RDIO, при совпадении адреса и управляющего сигнала активизирует выходные линии регистра и его содержимое поступает по шине данных в процессор.

Внешняя среда

Рис. 6.7. Параллельный обмен на базе буферных регистров

Аналогично идет обращение к устройству вывода. Совпадение адреса устройства на шине адреса с активным уровнем сигнала WRJO обеспечивает "защелкивание" состояния шины данных в регистре вывода.

Характерно, что при таком способе обмена процессор не анализирует готовность ВУ к обмену, а длительность существования адреса, данных и управляющего сигнала целиком определяется тактовой системой процессора и принятым алгоритмом командного цикла. Напомним, что такой способ обмена называется синхронным. Синхронный обмен реализуется наиболее просто, но он возможен только с устройствами, всегда готовыми к обмену, либо процессор должен перед выполнением команды ввода/вывода программными средствами убедиться в готовности ВУ к обмену (обычно в этом случае предварительно анализируется состояние флага готовности, формируемого ВУ). Кроме того, быстродействие ВУ, взаимодействующее с процессором в синхронном режиме, должно гарантировать прием/выдачу данных за фиксированное время, выделенное процессором на цикл обмена.

Во многих микропроцессорных комплектах выпускают специальные интерфейсные БИС, существенно расширяющие (по сравнению с использованием регистров) возможности разработчиков при организации параллельного обмена в МПС. Такие БИС обычно имеют несколько каналов передачи информации, позволяют программировать направление передачи (ввод или вывод) по каждому каналу и выбирать способ обмена— синхронный или асинхронный.

Типичным примером такой БИС может служить программируемый контроллер параллельного обмена (далее "контроллер") 825 5А (отечественный аналог — К580ВВ55).

Контроллер параллельного обмена К580ВВ55 представляет собой трехканальный байтовый интерфейс и позволяет организовать обмен байтами с периферийным оборудованием в различных режимах. Он включает в себя три 8-разрядные канала ввода/вывода А, В и С, буфер шины данных, 8-разрядный регистр управления Y и блок управления.

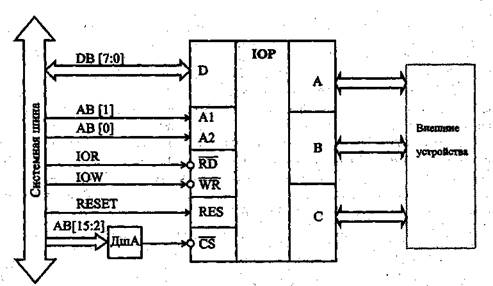

Подключение контроллера к системной шине показано на рис. 6.8. Каналы адресуются двумя линиями адреса А1, АО. В МПС контроллер размещают, как правило, в пространстве адресов ввода/вывода. Поэтому в качестве стробов чтения и записи используются сигналы RDIO, WRIO, для селекции контроллера по CS дешифрируются старшие разряды адреса, а для выбора адресуемого объекта внутри контроллера— два младших.

Рис. 6.8. Подключение контроллера 8255 к системной шине

Каналы контроллера программируются для работы в одном из трех режимов:

□ режим "О" — синхронный однонаправленный ввод/вывод;

□ режим "1" — асинхронный однонаправленный ввод/вывод;

□ режим "2" — асинхронный двунаправленный ввод/вывод.

Режим работы контроллера устанавливается кодом управляющего слова, которое предварительно записывается в регистр управления Y.

В режиме "О" контроллер может работать как четыре порта ввода/вывода: А[7:0]. В(7:0], С[7:4], С[3:0],причем каждый порт может быть независимо запрограммирован на ввод или на вывод. При этом к порту, определенному как выходной, нельзя обращаться по чтению, а на входной порт нельзя выводить информацию.

В асинхронном однонаправленном режиме «1» могут работать только каналы А и В, причём соответствующие линии канала С придаются каналам А и В для передачи управляющих сигналов. Как и в режиме "0", каналы А и В программируются на ввод или вывод(независимо).

В режиме "2" может работать только канал А, к которому в этом случае можно обращаться как по записи, так и по чтению (двунаправленный асинхронный обмен). При этом канал В может быть запрограммирован как на работу в режиме "1", так и в режиме "О".

Выбор режимов каналов и направления передачи данных в них осуществляется загрузкой во внутренний управляющий регистр Y соответствующего кода.

Линии канала С могут работать только в режиме "0", причем независимо можно запрограммировать направление передачи: старшей и младшей тетрады, канала С. Если для каналов А и/или В выбраны режимы "2" и/или "1", то соответствующие линии канала С перестают работать в режиме "0" и используются для передачи управляющих сигналов. Линии канала С, которые не используются при выбранной комбинации режимов каналов А и В, можно использовать как линии ввода или вывода канала С, работающего в «0»-режиме. Кроме того, всегда имеется возможность программного сброса/установки произвольного разряда канала С.

Режим "0" является синхронным и во многом напоминает рассмотренный выше механизм обмена с использованием регистров. Рассмотрим подробнее процесс асинхронного обмена в режиме "1".

Режим " 1" обеспечивает однонаправленную, асинхронную передачу информации между процессором и ВУ. При этом каналы А и В используются как регистры данных, а канал С-— для приёма и формирования управляющих сигналов, сопровождающих асинхронный обмен, причем каждый разряд канала С имеет строго определенное функциональное назначение.

Например, если канал запрограммирован на ввод в режиме "1", то процессор может вводить данные этого канала только "будучи уверенным" в их готовности. Об этой готовности ему должен сообщить контроллер путем установки специального признака— флага в определенном разряде регистра С и, может быть, формированием запроса на прерывание с соответствующим вектором. С другой стороны, внешнее устройство, подключенное к каналу, не должно выдавать новую порцию информации, пока прежняя не будет прочитана процессором.

Для обеспечения синхронизации ввода в режиме "1" каналу придаются три линии канала С для передачи управляющих сигналов:

□ STB (строб записи)— сигнал, формируемый ВУ для записи очередного байта данных в регистр канала:

□ IBF (подтверждение приема) — сигнал, формируемый контроллером для ВУ в тот момент, когда процессор прочитал содержимое регистра канала. Пока сигнал EBF неактивен, ВУ Запрещается вырабатывать новый строб записи;

□ INT (запрос прерывания) — вырабатывается контроллером для процессора после того, как очередной байт данных запишется в регистр канала. Это же событие устанавливает флаг готовности канала в разряде регистра С.

Обмен начинается с подачи ВУ сигнала STB, по которому данные помещаются в регистр канала. Контроллер, во-первых, сбрасывает сигнал IBF, запрещая ВУ выработку Нового строба, и, во-вторых, устанавливает флаг готовности и (может быть) формирует сигнал запроса на прерывание INT процессору. Процессор может достаточно долго не реагировать на сообщение о готовности канала, занятый более приоритетными процедурами. Все это время установлены готовность и INT и сброшен IBF, новая порция информации

не может поступить в канал.

Когда процессор обратится по адресу канала и введет хранящуюся в регистре информацию, контроллер сбрасывает флаг готовности и запрос на прерывание INT и устанавливает сигнал IBF, разрешая ВУ записывать следующий байт в регистр канала. Однако ВУ может быть достаточно инерционным и довольно долго подготавливает следующую порцию информации, но пока ВУ не сформирует новый сигнал STB, контроллер не выработает сигнал готовности и, следовательно, процессор не будет обращаться по адресу канала.

Подобный режим обмена позволяет исключить как потерю информации в контроллере, так и повторный ввод в процессор прежней информации.

Аналогично реализуется и асинхронный, режим вывода. Каналу, запрограммированному на вывод в режиме "1", придаются три линии управления канала С:

□ OBF (выходной буфер заполнен)— сигнал формируется контроллером для ВУ после того, как процессор записал в регистр канала новую порцию информации;

□ АСК. (подтверждение записи)— сигнал от ВУ контроллеру, подтверждающий прием очередного байта;

□ INT (запрос прерывания) — запрос прерывания от контроллера процессору для выдачи процессором в канал следующего байта информации.

Процедуры ввода и вывода в режиме "2" осуществляются аналогично соответствующим процедурам в режиме "1".

Date: 2015-09-18; view: 634; Нарушение авторских прав