Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Накапливающий сумматор

|

|

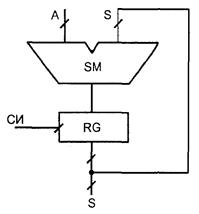

Накапливающий сумматор обычно представляет собою сочетание комбинационного сумматора и регистра, работающее по формуле S:= S + А, согласно которой к содержимому сумматора добавляется очередное слагаемое, и результат замещает старое значение суммы. Структура накапливающего сумматора показана на рис. 11. Очередное прибавление слагаемого тактируется синхроимпульсами СИ. Учитывая особенности функционирования, накапливающие сумматоры называют иногда аккумуляторами.

Рис. 11. Структура накапливающего сумматора

В сериях элементов имеются одноразрядные сумматоры, в том числе с дополнительной входной логикой, двухразрядные и четырехразрядные. Примером стандартных ИС сумматоров могут служить микросхемы ИМЗ серии К555, содержащие четырехразрядный сумматор с последовательным переносом и блок переноса (рис. 2.36), которые непосредственно пригодны для составления из них группового сумматора с цепным переносом.

Микросхемы четырехразрядных сумматоров можно также объединять в групповую структуру с межгрупповым параллельным переносом с помощью специальных блоков ускоренного переноса.

Рис. 12. Структура микросхемы К555ИМ3

В некоторых сериях элементов сумматоры отсутствуют. Причиной этого обычно является наличие арифметико-логического устройства (АЛУ), для которого режим суммирования есть один из возможных режимов.

Цифровые ( двоичные ) компараторы

Цифровой (двоичный) компаратор (устройство сравнения) [от англ. compare – сравнивать] – это КЦУ, определяющее отношения между двумя двоичными словами.

За основные отношения, через которые можно выразить все остальные, обычно берут два – “ равно ” (=) и “ больше ” (>), хотя также можно рассматривать и пару “ равно ” (=) и “ меньше ” (<).

Определим функции, вырабатываемые компараторами, следующим образом: они принимают единичное значение (истинны), если соблюдается условие, указанное в индексе обозначения функции F. Например, функция FA = B = 1, если А = В и принимает нулевое значение при А ≠ В.

Приняв в качестве основных отношения “равно” (=) и “больше” (>), для всех остальных отношений можно записать:

;

;

;

;

;

;

Эти отношения используются как логические условия в микропрограммах, в устройствах контроля и диагностики ЭВМ и т. д.

Эти отношения используются как логические условия в микропрограммах, в устройствах контроля и диагностики ЭВМ и т. д.

В сериях цифровых элементов обычно имеются компараторы с тремя выходами: “ равно ”, “ больше ” и “ меньше ” (рис. 3.11). Для краткости записей в обозначении выходных функций компаратора указывается только слово А.

Соотношения входных и выходных сигналов (таблица истинности) компаратора представлены в табл. 3.11.

Таблица 3.11

| Сравниваемые данные | Входы наращивания | Выходы | |||||||

| A3, B3 | A2, B2 | A1, B1 | A0, B0 | I(A>B) | I(A<B) | I(A=B) | A>B | A<B | A=B |

| A3>B3 | × | × | × | × | × | × | |||

| A3<B3 | × | × | × | × | × | × | |||

| A3=B3 | A2>B2 | × | × | × | × | × | |||

| A3=B3 | A2<B2 | × | × | × | × | × | |||

| –» – | A2=B2 | A1>B1 | × | × | × | × | |||

| –» – | A2=B2 | A1<B1 | × | × | × | × | |||

| –» – | –» – | A1=B1 | A0>B0 | × | × | × | |||

| –» – | –» – | A1=B1 | A0<B0 | × | × | × | |||

| –» – | –» – | –» – | A0=B0 | ||||||

| –» – | –» – | –» – | A0=B0 | ||||||

| –» – | –» – | –» – | –» – | ||||||

| –» – | –» – | –» – | –» – | ||||||

| –» – | –» – | –» – | –» – | ||||||

| –» – | –» – | –» – | –» – |

Три последние строки таблицы отражают режим наращивания каскадов, который может быть последовательным или параллельным. При последовательном наращивании выходы A>B, A<B, A=B от схемы, анализирующей младшие разряды, следует присоединить к одноименным входам последующего каскада. Этим способом с помощью двух 4-разрядных компараторов можно сравнить два восьмиразрядных слова. Нетрудно подсчитать число каскадов для любой бо́льшей длины слова. Однако каждый последовательный каскад добавит время задержки распространения сигнала 15 нс.

Для правильной работы последовательного многокаскадного компаратора на входы I (A>B), I (A<B) следует подать напряжение высокого уровня, а на вход I(A=B) – низкого.

Устройства сравнения на равенство строятся на основе поразрядных операций над одноимёнными разрядами обоих слов.

Слова равны, если равны все их одноимённые разряды, т. е. если в обоих нули или единицы. Признак равенства i -ых разрядов можно вычислить так:

или

.

.

Признак неравенства разрядов

.

.

Признак равенства двух слов A и B в целом

.

.

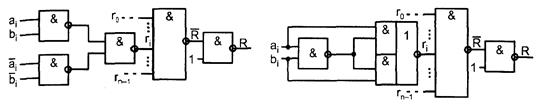

Схема компаратора на равенство в базисе И-НЕ показана на рис. 3.12, а.

а б

Рис. 3.12. Схемы компараторов на равенство

Схема проверки на равенство без парафазных входов (рис. 3.12, б)основана на выражениях для ri ,преобразованных следующим образом:

Построение компаратора на “больше” для одноразрядных слов (табл. 3.12) требует реализации функции запрета по b:  .

.

Таблица 3.12

| a | b | Fa > b |

Функцию FA > B для многоразрядных слов проще всего получить на основе следующих рассуждений. Пусть нужно сравнить двухразрядные слова A=a 1 a 0 и B=b 1 b 0. Если старшие разряды a 1 и b 1 не равны, то результат известен независимо от младших разрядов: при a 1 = 1 и b 1 = 0 имеем А > В, а при a 1 = 0 и b 1 = 1 имеем А < В. Если же a 1 = b 1, то результат ещё неизвестен, и требуется анализ младших разрядов по тому же алгоритму. Поэтому для двухразрядных слов можно записать

.

.

Подобный же подход справедлив и для слов любой разрядности – к анализу следующего разряда нужно переходить только при равенстве предыдущих. Таким образом, для общего случая n -разрядных слов имеем

(3.11)

(3.11)

Правильно рассуждая, мы получили правильный результат. Однако цель минимизации формул при этом не ставилась и на самом деле выражения для FA > B не минимальны. В минимальном варианте признаки равенства ri можно заменить более простыми функциями  , которые равны ri для всех комбинаций, кроме ai = 1 и bi = 0, но это соответствует условию

, которые равны ri для всех комбинаций, кроме ai = 1 и bi = 0, но это соответствует условию  , которое уже проверялось в предыдущем слагаемом уравнения (3.11). Однако для построения компаратора с тремя выходами (“равно”, “больше” и “меньше”) полученный нами вариант (3.11) остаётся предпочтительным, поскольку функции ri всё равно нужны для сравнения на “равно”, и для операций сравнения на “больше” они могут быть взяты в готовом виде.

, которое уже проверялось в предыдущем слагаемом уравнения (3.11). Однако для построения компаратора с тремя выходами (“равно”, “больше” и “меньше”) полученный нами вариант (3.11) остаётся предпочтительным, поскольку функции ri всё равно нужны для сравнения на “равно”, и для операций сравнения на “больше” они могут быть взяты в готовом виде.

Пример реализации компаратора с тремя выходами для двухразрядных слов приведён на рис. 3.13.

Выработка признака A > B в этой схеме производится по соотношению (штрихом отмечены функции с выходов младшей группы):

.

.

Компараторы для слов большой разрядности получают наращиванием размерности путём использования нескольких ИС компараторов. Принцип наращивания хорошо иллюстрируется на том же рис. 3.13.

Примером гибкости цифровой схемотехники может служить возможность построения компаратора на равенство с помощью последовательного соединения демультиплексора и мультиплексора, как показано на рис. 3.14. В работе такого компаратора легко разобраться, если вспомнить, как функционируют входящие в него блоки.

Пример 3.11. Построить на ЛЭ схему сравнения на равенство двух 8-разрядных чисел.

Особенность данной задачи состоит в том, что для её решения практически невозможно построить таблицу: число строк в ней будет 2(8+8) =

= 216 =65536. Подобные задачи решают иначе – методом декомпозиции задачи – разбиения её на более мелкие подзадачи. В нашем случае: два числа равны, если попарно равны их одноименные разряды. Структурная схема такого компаратора показана на рис. 3.15, а.

Рис. 3.13. Пример построения компаратора

Рис. 3.14. Реализация компаратора на равенство

с помощью дешифратора-демультиплексора и мультиплексора

Известно, что функция равенства двух аргументов – это инверсия их суммы по модулю 2. Чтобы исключить из проектируемой схемы 8 инверторов воспользуемся соотношением:

.

.

Решение данной задачи показано на рис. 3.15, б. Оно учитывает, что в семействах ЛЭ нет элемента 8ИЛИ-НЕ, а есть только 4ИЛИ-НЕ.

Рис. 3.15. Узел сравнения на равенство 8-разрядных слов

Отечественной промышленностью выпускаются компараторы ТТЛ 555СП1, 531СП1 и КМОП 561ИП2.

Отечественной промышленностью выпускаются компараторы ТТЛ 555СП1, 531СП1 и КМОП 561ИП2.

Микросхема К555СП1 (рис. 3.16) является 4-разрядным компаратором. Он имеет три выхода: “ A > B ”, “ A < B ”, “ А = В ”, и в зависимости от соотношения чисел А и В активный уровень появляется на одном из этих выходов. Входы “>”, ”<”, ”=” служат для подключения выходов компаратора нижнего уровня, сравнивающего младшие разряды слов бо́льшей битности, при наращивании разрядности компараторов.

Схема параллельного компаратора для двух двадцатичетырехразрядных слов представлена на рис. 3.17.

Здесь младший (нижний в схеме) компаратор СП1 используется как четырёхразрядный, четыре старших как пятиразрядные, т. к. входы I (A>B), I (A<B) служат пятой парой разрядных входов, т. е. А4 и В4 соответственно. На входы I (A=B) старших компараторов подано напряжение нулевого уровня.

Таким способом и однозначную микросхему СП1 можно использовать как пятиразрядный компаратор.

Таким способом и однозначную микросхему СП1 можно использовать как пятиразрядный компаратор.

В КМОП серии компаратор 561ИП2 имеет несколько отличных режимов работы: например при всех низших уровнях входных сигналов I (A>B), I (A=B), I (A<B) выходные A>B, A=B, A<B также низкие (у 555СП1 – высокие), т. е. для анализа работы компаратора надо использовать другую таблицу.

Схема последовательного соединения ИП2 для сравнения двенадцатиразрядных слов представлены на рис. 3.18.

| |||

|

Date: 2016-05-16; view: 2939; Нарушение авторских прав