Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Ш күйлі ТТЛ-сұлбасының жұмыс істеу принципы

К531 сериялы ТТЛ ИС-ң базалық элементі. Сұлбасы оң логикадағы орындайтын функциясы және жұмыс істеу принципы..

К531 (SN74S) сериялы Шоттки транзисторлары бар ТТЛ интегралды микросұлбалар, стандартты ИС-ға қарағанда пайдаланатын қуаты жоғары (20 МВт) болса да, жылдамдығы үш есе жоғары болады (3 нс). Пайдаланатын қуаты төмен (2 МВт), КМ555 (SN74LS) сериялы ТТЛШ ИС-ының жылдамдығы төмен болады (10 нс)

К531 сериялы ТТЛ

К 155 стандартты сериялы ТТЛ интегралды схемаларда кәдімгі ашық кезінде қанығу режимінде жұмыс жасайтын транзисторлар пайдаланылады. Бұл транзисторлар логикалық элемент сұлбасының жабылу кезінде қосымша уақыт кедергісіне, сол себепті сұлбаның жылдамдығының төмендеуіне әкеледі. К531, К555, К1531 және К1533 сериялы ТТЛ интегралды сұлбалардың жылдам-дығын арттыру үшін оларда кәдімгі транзисторлардың орнына қанығу режимде жұмыс жасамайтын Шоттки транзисторлары пайдаланылады.

Жоғарыда қарастырылған ТТЛ элементтерінің сұлбаларынан басқа цифрлы сұлбатехникада үш тұрақты жағдайы бар ТТЛ сұлба және коллекторлық шығысы ашық (бос) ТТЛ сұлбасы пайдаланылады. Коллекторлық шығысы ашық (бос) ТТЛ сұлба арнайы жүктемеге (жарық шамына, жарық диодына және т.б.) жұмыс жасау үшін пайдаланылады.

ш күйлі ТТЛ-сұлбасының жұмыс істеу принципы.

Аталынған сериялардың құрамына кіретін барлық логикалық элементтер схематехникалық бойынша логикалық элементтердің келесі ЖӘНЕ - ЕМЕС (3.1, а – сурет) және НЕМЕСЕ бойынша кеңейткіштің (3.1,ә – сурет) екі базалық сұлбаларының комбинацияларының негізінде алынады. Логикалық элемент ЖӘНЕ – НЕМЕСЕ – ЕМЕС ЛЭ ЖӘНЕ – ЕМЕС мен НЕМЕСЕ бойынша кеңейткіштің бірігуінен алынған. НЕМЕСЕ логикалық кірісі негізінде бірігу санын арттыру үшін 1-а суреттегі 1 және 2 нүктелерге НЕМЕСЕ бойынша кеңейткішті (3.1, ә – сурет) қосу керек. НЕМЕСЕ бойынша кеңейткіш мүмкіншілігі бар ТТЛ ИС барлық серияларында бірігу санының жоғарғы мәні 8-ге тең. Жоғары жүктемелік мүмкіншілігі (n  10) және элементтердің өзара бірігіп жұмыс жасауы олардың салыстырмалы жоғары емес кіріс және жоғары шығыс токтарымен қасыз етіледі.

10) және элементтердің өзара бірігіп жұмыс жасауы олардың салыстырмалы жоғары емес кіріс және жоғары шығыс токтарымен қасыз етіледі.

а) ә)

3.1-сурет. К155 сериялы ТТЛ логикалық элементінің базалық схемасы

(а) және НЕМЕСЕ логикалық кеңеймесі (ә).

3. К500 сериялы ЭБЛ ИС-ң базалық элементі. Сұлбасы, теріс логикадағы орындайтын функциялары және жұмыс істеу принципі.

Микросхемы серии К500 выпускаются в пластмассовом и керамическом корпусах со штыревыми выводами, а микросхемы серии К1500 конструктивно изготавливаются в основном в керамических корпусах с планарным расположением выводов. Схема базового элемента ЭСЛ серии К500, которая показана на рис. 2.7, состоит из трех частей: токового переключателя (ТП), выходных эмиттерных повторителей (ЭП) и цепи источника опорного напряжения (ИОН).

а) б)

Рис. 2.7. Схема базового элемента ЭСЛ серии К500 а) и ее условное обозначение б)

Обычно элементы ЭСЛ имеют два или три входа. Увеличение числа входов приводит к повышению входной паразитной емкости и, как следствие, к снижению быстродействия.

ТП построен на транзисторах Т0, Т1 и Т2 и резисторах RЭ, RК1 и RК2. Основу ТП составляет дифференциальный усилитель, работаю-щий в ключевом режиме, при этом транзисторы Т0, Т1 и Т2 не входят в режим насыщения. ТП служит для усиления входных сигналов, обеспечения требуемой помехоустойчивости элемента, формирова-ния парафазных (прямого и инверсного) выходных сигналов и реализации логических функций на этих выходах.

4. nМДЖ-транзисторлар негізіндегі ЖӘНЕ-ЕМЕС логикалық элемент. Сұлбасы, оң логикадағы орындайтын функциясы және жұмыс істеу принципі.

Ары қарай nМОЖ-транзисторлар негізіндегі базалық логикалық элементтердің құрастыру принциптерін және жұмыстарын қарастырайық. Төменде ЖӘНЕ - ЕМЕС және НЕМЕСЕ - ЕМЕС функцияларын орындайтын екі кірісті логикалық элементтердің электрлік сұлбалары көрсетілінген (4.1-сурет). Бұл сұлбаларда стоктік қорек көзі есебінде оң мәнді кернеу пайдаланылады. Логикалық 1 сигналына кернеудің жоғарғы деңгейі сәйкес, ал логикалық 0 сигналына оң мәнді кернеудің төменгі деңгейі сәйкес. Екі сұлбада да үш транзистордан пайдаланылады. Т0 транзистор стоктік жүктеменің функциясын атқарады, ал Т1 және Т2 транзисторлар логикалық функцияларды орындау үшін пайдаланылады. Олар ашылу және жабылу ауысу режимдерінде жұмыс жасайды. nМОЖ –транзисторлар негізінде құрастырылынған ЖӘНЕ –ЕМЕС функциясын орындайтын логикалық элементтің сұлбасында (4.1, а-сурет) ауысу режимінде жұмыс жасайтын Т1 және Т2 транзисторлар бір-бірімен тізбектеліп қосылынған. Сол себепті сұлбаның шығысында төменгі деңгейлі кернеуді алу үшін Т1 және Т2 транзисторлардың затворларына жоғарғы деңгейлі логикалық 1 сигналына сәйкес кернеулерді беру керек. Соныменен, ЖӘНЕ – ЕМЕС элементтің екі кірістерінде де логикалық 1-ге сәйкес сигналдар болғанда оның шығысында логикалық 0-ге сәйкес сигнал болады. ЖӘНЕ – ЕМЕС логикалық элементтің кірістерінің (ауысу режимінде жұмыс жасайтын кіріс транзисторлардың) санының жоғарғы мәні 4-ке тең (mи = 4). ЖӘНЕ – ЕМЕС логикалық элемент сұлбасында кіріс транзисторлардың санын арттырған кезде сұлбаның топологиясы қиындалынады, сұлбаның тығыздылығы азаяды және оның кернеу бөгеуіліне тұрақтылығы төмендейді (логикалық 0 сигналына сйкес кернеудің артуына байланысты).

НЕМЕСЕ – ЕМЕС сұлбасында (4.1, б-сурет) Т1 және Т2 транзисторлар бір-бірімен параллель қосылынған, сондықтан егер оның тек бір ғана кірісіне логикалық 1-ге сәйкес сигнал берсек, онда схеманың шығысында логикалық 0-ге сәйкес сигнал құрастырылынады. НЕМЕСЕ – ЕМЕС сұлбасының кірістерінің жалпы саны 10-ға тең (mили = 10).

а) б)

4.1-сурет. nМОЖ транзисторында ЖӘНЕ-ЕМЕС (а) және НЕМЕСЕ-ЕМЕС (б) ЛЭ электрлі сұлбалары

5. nМДЖ-транзисторлар негізіндегі НЕМЕСЕ-ЕМЕС логикалық элемент. Схемасы, оң логикадағы орындайтын функциясы және жұмыс істеу принципі.

6. КМДЖ құрылымы негізіндегі ЖӘНЕ-ЕМЕС логикалық элемент. Сұлбасы, оң логикадағы орындайтын функциясы және жұмыс істеу принципі.

7. КМДЖ құрылымы негізіндегі НЕМЕСЕ-ЕМЕС логикалық элемент. Сұлбасы, оң логикадағы орындайтын функциясы және жұмыс істеу принципі.

НЕМЕСЕ – ЕМЕС сұлбасы кірістерінің бірігу коэффициентінің mили мәні тек логикалық 1-ге сәйкес кернеу деңгейінің төмендеуіменен түсіндіріледі. Логикалық 1-ге сәйкес кернеу деңгейінің төмендеуі кіріс транзисторлардың сток – исток тізбектеріндегі ағатын токтарлар негізінде пайда болатын сұлбаның шығысындағы кернеудің төмендеуіменен түсіндіріледі. МОП транзисторлардың кіріс кедергілерінің жоғары болуынан және соған сәйкес транзисторлардың кіріс ағу тогының мәнінің аздығынан осы транзисторлар негізінде құрастырылынған цифрлы интегралды сұлбалардың жүктемелік коэффициенттері (n= 10–20) өте жоғары болады.

Комплементарлы МОЖ (КМОЖ) құрылымы өткізгіштік типі әртүрлі МОЖ транзисторлардан құрастырылынған терістегіш сұлбаға сәйкес(4.2, а-сурет).

а) б) в)

4.2-сурет. КМОП элементтерінің сұлбалары: инвертордың (а), ЖӘНЕ-ЕМЕС (б)

және НЕМЕСЕ-ЕМЕС (в)

Өткізгіштігі n-типтес Т1 транзистордың негізгі электроды (подложкасы) нольдік потенциалға (жерге) қосылынған, ал өткізгіштігі p-типтес Т2 транзистордың подложкасы кернеуі оң мәнді қорек көзіне қосылынған. Т1 және Т2 транзисторлардың затворлары біріктірілінген, олар КМОЖ логикалық элементі сұлбасының кірісі болып есептелінеді. КМОЖ логикалық элементтер nМОП логикалық элементтерге қарағанда статикалық режимде қуатты өте аз пайдаланады (бірнеше және одан аз мкВТ), жылдамдығы жоғары, жүктемелік коэффициенті жоғары (n  15–20) және кернеу бөгеуілі жақсы (логикалық 1-ге және 0-ге сәйкес кернеу деңгейлерінің айырмашылығы жоғары болуы себепті). КМОП интегралды сұлбаларда қуат тек қана сұлба бір жағдайдан екінші жағдайға ауысқан кезде, басқаша айтқанда тек динамикалық режимде ғана пайдаланылады. Бұл режимде шығыс тізбектегі ток жүктемелік паразитті сиымдылықты зарядтау үшін пайдаланылады.

15–20) және кернеу бөгеуілі жақсы (логикалық 1-ге және 0-ге сәйкес кернеу деңгейлерінің айырмашылығы жоғары болуы себепті). КМОП интегралды сұлбаларда қуат тек қана сұлба бір жағдайдан екінші жағдайға ауысқан кезде, басқаша айтқанда тек динамикалық режимде ғана пайдаланылады. Бұл режимде шығыс тізбектегі ток жүктемелік паразитті сиымдылықты зарядтау үшін пайдаланылады.

Логикалық ЖӘНЕ – ЕМЕС функциясын орындау үшін төмендегі nМОЖ-транзисторларды тізбектеп, ал жоғарыдағы pМОП-транзисторларды параллель қосу керек. НЕМЕСЕ – ЕМЕС функциясын орындау үшін nМОЖ транзисторларды параллель, ал pМОЖ- транзисторларды тізбектеп қосу керек. Сонымен қатар КМОЖ структурасын құрайтын nМОЖ және pМОЖ транзисторлардың затворлары бір-бірімен бірігеді және КМОЖ элементтің кірісі болып есептелінеді. Әлбетте КМОЖ логикалық элементтердің кірістерінің бірігу коэффициенті 4-тен жоғары емес(m  4). ЖӘНЕ – ЕМЕС және НЕМЕСЕ – ЕМЕС функцияларын орындайтын КМОЖ сұлбаларда сол функцияларды орындайтын nМОЖ сұлбаларға қарағанда транзисторлардың саны көп. Ол олардың кемшілігі болып есептелінеді.

4). ЖӘНЕ – ЕМЕС және НЕМЕСЕ – ЕМЕС функцияларын орындайтын КМОЖ сұлбаларда сол функцияларды орындайтын nМОЖ сұлбаларға қарағанда транзисторлардың саны көп. Ол олардың кемшілігі болып есептелінеді.

Бірақ та аса төмен тұтыну қуат және жоғарғы тез әрекетті КМОЖ элементтері аса үлкен интегралды сұлбаларды өңдегенде қолданылады.

8. Үш кіріс айнымылысы бар толық дешифратор. Логикалық теңдеулері және оның жұмысын түсіндіретін ақиқаттық кестесі.

Дешифратор немесе декодер дегеніміз кірістегі n-разрядты екілік коданы шығысында ондық санға түрлендіретін комбинациялы типті функционалды түйін. Дешифратордың әрбір шығыс функциясы кіріс сигналдарының мүмкін болатын m комбинацияларының біріне сәйкес келеді. Басқаша айтқанда, кіріс сигналының әрбір нақты комбинациясы үшін оған сәйкес шығыс функциясы мысалы логикалық 1-ге сәйкес келетін белгілі бір мәнді қабылдайды, ал қалғандары логикалық 0 мәнін қабылдайды. Егер n дешифратор кірісі m санды шығыспен m=2n қатынасымен байланысқан болса, онда дешифратор толық дешифратор деп аталады. Мысалы, толық емес дешифратор деп 4 кірісі және 10 шығысы бар дешифраторды айтамыз, ол екілік коданы екілік-ондық кодаға түрлендіру үшін қолданылады. Дешифратор жұмысы шифратордың ақиқат кестесі сияқты кестемен баяндалады, мұнда тек кіріс және шығыс сигналдары орындары ауысқан.

| 9x | 8x | 7x | 6x | 5x | 4x | 3x | 2x | 1x | 0x | 3y | 2y | 1y | 0y |

Ақиқат кестесі

Сұлбатехникалық түрде дешифраторла ЖӘНЕ және ЖӘНЕ-ЕМЕС логикалық элементтерінен жасалынады. Соңғы жағдай үшін дешифратор терістеуші шығысы бар дешифратор деп аталады. Сызықты деп аталатын ең қарапайым дешифратор сұлбасында әрбір шығыс функциясын іске асыру үшін жеке n-кірісті ЖӘНЕ және ЖӘНЕ-ЕМЕС логикалық элементтері қолданылады. ЖӘНЕ (немесе ЖӘНЕ-ЕМЕС) логикалық элементтерінің кірістеріне кіріс сигналының мәніне сейкес комбинация беріледі. ЖӘНЕ-ЕМЕС логикалық элементтерінен тұратын дешифратордың шартты графикалық белгіленуі 5.2-суретте көрсетілген. Әрбір ЖӘНЕ-ЕМЕС логикалық элементтерінің шығысында m шығыс функциясының біреуінің инверсиясы орындалады.

Және бұл жағдайда оның шығысында қозған кірістердің ең үлкенінің номеріне сәйкес екілік кодадағы сан бейнеленеді. Приоритетті шифраторлар одан да күрделі операцияларды орындауға арналған, мысалы, келген сұраныстарға бірінші кезекті қызмет көрсету құқығын таңдап беру.

Кеңінен қолданысқа ие болған дешифратордың сызықты сұлбасының логикалық элементтер саны минималды және каскадты (пирамидалы және ткібұрышты) дешифраторларға қарағанда жылдамдығы жоғары.

5.2-cурет. Дешифратордың шартты графикалық белгіленуі.

Сызықты дешифратор жылдамдығы бір ғана логикалық элементтің қайта қосылу уақытымен анықталады. Дешифратор түрлі комбинациялық сұлбаларда, мысалы, мультиплексорда, демультиплексорда, кода түрлендіргіштерінде қолданылады және жады құрылғыларында дешифратор көмегімен ақпарат жазылатын немесе оқылатын ұяшықтар таңдалынады.

«2n түрден 1» типті дешифратормен қатар, кодалар мен сандарды қандай да бір қажетті формаға түрленіретін арнайы дешифраторларда қолданылады.

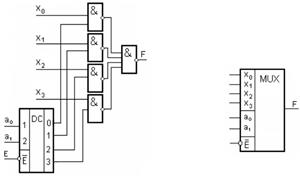

9. 1 стробтаушы, 2 мекендік және 4 ақпараттық кірістері және 1 ақпараттық шығысы бар мультиплексордың функционалды сұлбасы, тағайындалуы, логикалық теңдеуі және жұмыс істеу принципі.

Мультиплексор деп бірнеше кіріс араларынан бір шығысқа келіп түсетін ақпаратты тасымалдауды басқаруға арналған комбинациялық құрылғы. Мультиплексорда ақпараттық кіріспен қатар, адрестік (басқарушы) және мультиплексор жұмысына рұқсат беруші стробтаушы кірістері болады. Адрестік кірістердегі сигналдар дәл қазіргі кезде қандай кіріс шығысқа жалғанғанын білдіреді. Әдетте m – ақпараттық кірі саны мен n – адрестік

кірістері арасында m=2n қатынасы орнатылған.

Құрамында 1 стробтаушы, 2 адрестік және 4 ақпараттық кірісі бар мультиплексор жұмысы келесі логикалық теңдеумен баяндалады:

(5.2)

мұнда Е - стробтау кірісіндегі сигнал, оның активті деңгейі мультиплексор жұмысына рұқсат береді.

Егер жұмыс істеуге рұқсат беруші Е стробтаушы кіріске логикалық 1 сигналы (Е=1) берілсе, онда xi ақпараттық және aj адрестік сигналдардың мәніне (i = 0, 1, 2, 3 және j = 0, 1) қарамастан мультиплексордың шығыс сигналы нөлге тең болады. (2) логикалық теңдеуге сәйкес келетін мультиплексордың сұлбасы және оның шартты графикалық белгіленуі 5.3-суретте көрсетілген.

5.3-суреттегі сұлбада екі кірісті ЖӘНЕ-ЕМЕС логикалық элементтері кірісіне адрестік сигналдар берілетін дешифратордың шығыс сигналдарымен басқарылады.

а) б)

5.3-сурет. Мультиплексор сұлбасы (а) және шартты графикалық белгіленуі (б)

Сонымен, дешифратор көмегімен төрт екі кірісті ЖӘНЕ-ЕМЕС логикалық элементтердің біреуі таңдалынады. Мультиплексор жылдамдығы дешифратордағы ЖӘНЕ-ЕМЕС логикалық элементтеріндегі сигналдарды үлестірудің кідіріс қосындысымен анықталады.

Мультиплексорлар MUX (ағылшынның multiplexor деген сөзінен шыққан) немесе MS (multiplexor selector) белгілерімен белгіленеді.

Жұмысқа рұқсат беруші Е кірісі мультиплексордың функционалды мүмкіндіктерін кеңейту үшін де қолданылады. Мультиплексор универсалды құрылғы болып табылады, оның негізінде түрлі комбинациялық және тізбекті сұлбалар жасалынады. Мультиплексорлар параллельді коданы тізбекті кодаға түрлендіруге арналған сигналдардың коммутатор-селекторы ретінде жиі қоданылады.

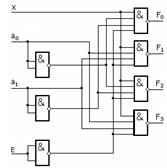

Стробтаушы, 2 мекендік және 1 ақпараттық кірістері және 4 ақпараттық шығыстары бар демультиплексордың функционалды сұлбасы, тағайындалуы, логикалық теңдеуі және жұмыс істеу принципі.

Демультиплексор деректерді адрестік кірістердегі сигналдарға байланысты бір ақпараттық кірістен бірнеше шығыстардың біреуіне тасымалдауды басқаруға арналаған комбинациялы логикалық құрылғы. Сонымен, демультиплексор мультиплексор жұмысына қарама қарсы функцияны орындайды және жалпы жағдайда бір ақпараттық кірісі, n адрестік кірісі және m ақпараттық шығыстары болады. Әдетте, демультиплексорда да мультиплексордағыдай m=2n қатынасы орнатылған. Мұндай жағдайда демультиплексор толық деп аталады, ал m<2n жағдайында толық емес демультиплексор деп аталады.

2 адрестік кірісі, 1 ақпараттық кірісі, стробтау кірісі және 4 ақпараттық шығысы бар демультиплексор жұмысы келесі логикалық теңдеулермен баяндалады:

(5.3)

(5.3)

(5.3) теңдеуге сәйкес ЖӘНЕ-ЕМЕС логикалық элементтерінен жасалған демультиплексор сұлбасы мен шартты графикалық белгіленуі 5.4-суретте көрестілген. Демультиплексор DMS немесе DMX әріптері арқылы белгіленеді.

5.4-суретте көрсетілген демультиплексор сұлбасында ЖӘНЕ-ЕМЕС логикалық элементтерін басқару үшін 2 кірісі бар дешифратор қолдануға болады.

а) б)

5.4-сурет. Демультиплексор сұлбасы (а) және оның шартты графикалық белгіленуі (б)

Демультиплекор шығыстары санын өсіру үшін мультиплексор кірістері санын өсірудегі әдіс қолданылады. Демультиплексорлар тізбекті коданы параллельді кодаға түрлендіру үшін қолданылады. Демультиплексордың ақпараттық кірі-сіне стробтаушы сигнал берсе, ол дешифратор режимінде жұмыс істей алады.

Бірразрядты толық қосындылағыш. Ақиқат кестесі, ЖӘНЕ-ЕМЕС базисіндегі S(сумма) - функциясы үшін логикалық теңдеуі және жұмыс принципі.

Бірразрядты толық қосындылағыш. Ақиқат кестесі, ЖӘНЕ-НЕМЕСЕ-ЕМЕС базисіндегі S(сумма) - функциясы үшін логикалық теңдеуі және жұмыс принципі.

Цифрлық компараторлар екілік кодада берілген екі санды салыстыру операциясын орындайды. Компаратор кірістерінің саны салыстырылатын екі a және b сандары кодасының разрядтылығымен анықталады. Цифрлық компаратордың үш шығысы бар, оларды келесідей сигналдар қалыптасады: FТ – егер a және b екілік сандары өзара тең болса (a = b); FҮ – егер ф санының кодасы b кодасынан үлкен болса (a>b); FК – егер a<b болса.

Date: 2016-05-16; view: 1943; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |