Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Элементная база

|

|

Основой микроэлектроники является интегральная микросхема, с использованием которой выполняются блоки и узлы устройств. В корпусе интегральной микросхемы все элементы соединены определенным образом. При поступлении на вход схемы сигнала на выходе выдаются сигналы, соответствующие выполняемой ею логической функции. Главной характеристикой микросхемы является степень интеграции, т. е. число элементов (вентилей) в корпусе. По степени интеграции микросхемы делятся на четыре класса: ИС — интегральные схемы, содержащие до 40 вентилей; СИС — средние интегральные схемы, содержащие сотни вентилей; БИС — большие интегральные схемы, содержащие тысячи вентилей; СБИС — сверхбольшие интегральные схемы, содержащие десятки тысяч вентилей.

ИС выполняют элементарные логические функции, а также служат для приема и передачи сигналов между узлами устройства или выхода на шину. На базе СИС формируют различного рода регистры, счетчики, дешифраторы, элементы памяти небольшого объема и др. На основе БИС и СБИС формируют, как правило, микропроцессоры и узлы памяти большого объема.

Транзисторные ИС можно разделить на две группы: биполярные и типа металл — окисел (диэлектрик) — полупроводник (МОП).

ИС группы МОП по структуре бывают двух типов: р -МОП — с положительным (р) носителем и n -МОП с отрицательным (п) носителем. Помимо этого бывают комплектарные (взаимодополняющие) КМОП-структуры.

Особенностью МОП-структур является малое потребление мощности, что позволяет увеличить степень интеграции.

ИС на основе биполярных транзисторов в зависимости от технологии изготовления бывают следующих модификаций: ТТЛ — (транзисторно-транзисторная логика); И2Л (интегральная инжекционная логика), ЭСЛ (эмиттерно-связанная логика), ИС с биполярными транзисторами имеют высокое быстродействие, однако степень интеграции этих схем ограничена потребляемой мощностью.

ИС, изготовленные по разным технологиям, имеют различные уровни входных и выходных сигналов. За стандартные приняты уровни ТТЛ-схем, рассчитанные на питание 5В; при использовании других ИС предусматриваются переходные схемы преобразования уровней.

В МОП-структурах функции пассивных элементов (резисторов) выполняют МОП-транзисторы, на затворы которых подается постоянный потенциал. На рис. 2.2, а представлена схема ИС типа И — НЕ, выполняемая на p -МОП транзисторах. Транзистор T1 является нагрузкой, на его затвор подается постоянный потенциал Ср. Затворы транзисторов Т2 и ТЗ являются логическими входами схемы, при подаче на оба эти входа потенциалов логических единиц они открываются и на выходе устанавливается потенциал логического нуля. Схемы требуют отрицательного напряжения источника Е питания, что затрудняет их сопряжение с ТТЛ-схемами.

Рис.2.2 Схема ИС типа И – НЕ, выполненная на р -МОП (а) и КМОП (б) транзисторах

Микросхемы со структурой типа р -МОП имеют тот же (что и микросхемы со структурой п -МОП) принцип выполнения логических операций, но с положительным напряжением источника питания; технология их изготовления несколько сложнее, однако быстродействие много выше.

Технология КМОП-ехем сложнее предыдущих вследствие использования транзисторов как р -МОП, так и п -МОП типа. Основным достоинством КМОП-схем является малая потребляемая мощность в статическом режиме, что объясняется отсутствием в этих схемах пассивных элементов, поглощающих мощность. На рис. 2.2, б представлена схема ИС типа И — НЕ на КМОП-транзисторах типа р (Т1, Т2) и типа п (ТЗ, Т4). Напряжение сигнала логической единицы, подаваемое на входы, открывает транзисторы ТЗ, Т4 и закрывает транзисторы Т1, Т2. В зависимости от комбинации входных сигналов на выходе устанавливается либо низкий уровень (на обоих входах единицы), либо высокий (все остальные комбинации). При любой комбинации входных сигналов ток течет не через всю схему. ИС со структурой типа КМОП с положительной логикой имеют уровни логических сигналов, совместимые с уровнями ТТЛ-схем.

Недостатком структуры типа КМОП является сравнительно низкое быстродействие ИС, обусловленное наличием в схемах паразитных емкостей. Достоинствами КМОП-схем являются возможность широкого диапазона изменения напряжения источника питания (3—12 В), высокая помехоустойчивость (по сравнению с п -МОП схемами), а также возможность использования батарейного питания.

Основным достоинством ИС на биполярных транзисторах является их высокое быстродействие. Серия К511 имеет высокую помехозащищенность и применяется в устройствах автоматики станков. Она состоит из небольшого набора логических ПС, триггеров, десятичного счетчика и десятичного дешифратора. На рис. 2.3, а представлена диодно-транзисторная схема, выполняющая логическую функцию И—НЕ. Диоды Д1 и Д2 совместно с резистором R1 выполняют логическую функцию И, транзистор Т1 и резистор R3 — функцию НЕ; диод ДЗ служит для связи между этими двумя схемами, а через резистор R2 подается напряжение смещения Б1; Е2 — напряжение в цепи.

Рис. 2.3 Схема ИС на основе биполярных транзисторов модификации ЭСЛ:

а - диодно-транзисторная схема, выполняющая логическую функцию И—НЕ;

б - транзисторная схема, выполняющая функцию ИЛИ.

На рис. 2.3, б представлена транзисторная схема, выполняющая логическую функцию ИЛИ. На базы транзисторов Т1, Т2, через резисторы R3, R4 подается низкий потенциал. При подаче высокого уровня на любой из входов транзисторы T1 или Т2 открываются; уровень напряжения на резисторе R5 возрастает, и транзистор ТЗ, связанный по эмиттеру с транзисторами Т1 и Т2, закрывается. Резистор R1 ограничивает токи через транзисторы Т1 и Т2. На выходе схемы через резистор R2 устанавливается высокий уровень, На базу транзистора ТЗ подается напряжение Есм смещения. Из-за сравнительно сложной технологии эти схемы дороги, требуют повышенной мощности питания и имеют низкую помехозащищенность вследствие того, что для повышения быстродействия транзисторы схем работают в ненасыщенных режимах. Транзисторные схемы применяют в основном в больших ЭВМ, где требуется предельно высокое быстродействие.

В различных цифровых устройствах (втом числе и в системах ЧПУ) наиболее широко применяются схемы транзисторно-транзисторной логики (ТТЛ) серии К155. Эта серия состоит примерно из 80 наименований ИС различного функционального назначен Среди них ИС, выполняющие логические функции И, НЕ, И —НЕ, ИЛИ—НЕ, И—ИЛИ—НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ. СИС выполняют функции регистров, счетчиков, дешифраторов, сумматоров, коммутаторов, запоминающих устройств. В составе серии имеются БИС ОЗУ и ПЗУ. Основным элементом ТТЛ-схем является многоэмиттерный транзистор, реализующий логическую операцию И. Число логических входов схемы определяется числом эмиттеров в транзисторе. На рис. 2.4, а приведена схема ИС ТТЛ-структуры, выполняющая логическую функцию И — НЕ. На входе схемы стоит транзистор Т1, коллектор которого соединен с базой транзистора Т2. Резистор R1 ограничивает ток через Т1; резистор R2 является нагрузкой Т2.

Рис. 2.4Схема ИС:

а - ТТЛ-структура, выполняющая логическую функцию И — НЕ;

б - И2Л-схема, выполняющая функцию ИЛИ.

Основным недостатком ТТЛ-схем является повышенная потребляемая мощность, усложняющая источники питания и требующая специальных мер по охлаждению устройств. Уменьшение потребляемой мощности приводит к снижению быстродействия (повышению времени задержки). Для повышения быстродействия ТТЛ-схем в транзисторы вводят нелинейную обратную связь с помощью диодов Шоттки (структура ТТЛШ), препятствующую насыщению транзисторов. По ТТЛШ-схеме строятся маломощные ИС, имеющие высокое быстродействие (серия К555). ИС серии К555 потребляет в четыре раза меньшую мощность, чем аналогичные по выполняемым функциям и быстродействию ИС серии К155.

Так же как КМОП-схемы, И2Л-схемы не имеют пассивных элементов. Они работают при низких напряжениях питания (примерно 1 В) и потребляют малую мощность при сравнительно высоком быстродействии, имея лучший среди рассматриваемых схем фактор качества.

Принцип инжекционного питания заключается в том, что с помощью транзистора-инжектора Ти (рис. 2.4, б) реализуется цепь генератора тока базы многоколлекторного транзистора Т, выполняющего функцию инвертора входного логического сигнала — функции НЕ. Функцию НЕ — ИЛИ можно получить, объединив коллекторные цепи двух схем НЕ.

Рассмотрим подробнее ИС серии К155 (ТТЛ-структура), применяемые во многих УЧПУ второго поколения (Н22, НЗЗ и др.) и представляющие собой ИС низкой степени интеграции, размещенные в 14-штырьковом прямоугольном пластмассовом корпусе. Модификации отличаются числом элементов в корпусе, числом входов и выполняемыми функциями. Все элементы серии можно разделить на три группы: группа 1ЛБ55 (базовая), выполняющая логические функции И — НЕ (семь модификаций); группа 1ЛР55 (расширяемая), выполняющая логические функции И —ИЛИ —НЕ с возможностью расширения по функции ИЛИ (две модификации); группа 1ЛП55, подключаемая к элементам группы 1ЛР55 для расширения по функции ИЛИ (две модификации).

Базовая группа (1ЛБ55) включает в себя три элемента: основной элемент И —НЕ; элемент И — НЕ с большим коэффициентом разветвления (для возможности подключения к выходу элемента большого числа входов других элементов); элемент И — НЕ с открытым коллекторным выходом.

Основные элементы И — НЕ имеют четыре модификации: 1ЛБ551 (содержит в одном корпусе два четырехвходовых элемента И — НЕ); 1ЛБ552 (содержит один восьмивходовый элемент); 1ЛБ553 (содержит четыре двухвходовых элемента); 1ЛБ554 (содержит три трехвходовых элемента). Все элементы серии K155 имеют положительное напряжение (+5 В) коллекторного питания. При этом базовые токи протекают в направлении от базы к эмиттеру, что на принципиальных схемах отражено соответствующим направлением эмиттерной стрелки. Транзисторы элементов надежно запираются нулевым потенциалом и не требуют специального источника напряжения смещения в базовых цепях. В качестве сигнала логической единицы в элементах принят высокий уровень напряжения (+2,4 В и выше). В качестве сигнала логического нуля принят низкий уровень напряжения (+0,45 В и ниже).

Элементы типа И —НЕ (рис. 2.5, а) состоят из четырех транзисторов (Т1—Т4), диода (Д1) и резисторов (R1—R4), Основой элемента (как и всех элементов серии) служит многоэмиттерный транзистор Т1, выполняющий функции И. Если хотя бы на один вход многоэмиттерного транзистора подан низкий уровень напряжения, от базы к эмиттеру через резистор R1 протекает ток и транзистор открыт. Открытый транзистор Т1 подаст на базу транзистора Т2 низкий уровень напряжения и запирает его, в результате чего на транзистор Т3 через резистор R3 — тоже подается низкий уровень напряжения и он запирается. Транзистор Т4 открыт высоким напряжением, поданным на его базу через резистор R2, благодаря чему и на выходе элемента устанавливается высокий уровень напряжения, поступающего через резистор R4, открытый транзистор Т1 и диод Д1.

Если на все входы элемента подается высокий уровень напряжения, на базу транзистора Т2 тоже подается высокий уровень напряжения и он отпирается, отпирая при этом транзистор ТЗ и запирая транзистор Т4. Через открытый транзистор ТЗ на выходе элемента устанавливается низкий уровень напряжения. Остальные модификации элементов типа И —НЕ отличаются только количеством эмиттеров многоэмиттерного транзистора Т1, т. е. числом входов.

Рис.2.5 Схема И—НЕ основного элемента ИС типа ТТЛ с закрытым (а) и открытым (б)

входом.

Схема элемента И — НЕ с большим коэффициентом разветвления работает аналогично описанной выше и отличается только тем, что в целях получения на выходе схемы сигнала большей мощности между коллектором транзистора Т2 ибазой транзистора Т4 включен транзистор, усиливающий ток, протекающий от резистора R2 на базу транзистора Т4. Элемент имеет обозначение 1ЛБ556.

Схема элемента И — НЕ с открытым выходом (рис. 2.5, б) работает аналогично предыдущей схеме (см. рис. 2.5, а), но не содержит транзистора, подающего на выход высокий уровень напряжения. Этот элемент применяют в основном для подключения внешних нагрузок тина реле или индикаторных ламп. Существует две модификации элементов: 1ЛБ5.57 (содержит две четырехвходовые схемы И —НЕ) и 1ЛБ558 (содержит четыре двухвходовые схемы И— НЕ).

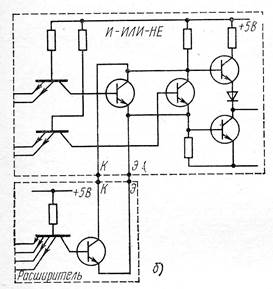

Схема И —ИЛИ —НЕ (рис. 2.6, а) имеет несколько многоэмиттерных транзисторов (Т1—Т6). Схема (в части Т1, Т2, Т3 Т4 Д1, Rl, R2, R3, R4) работает аналогично схеме И —НЕ, однако в нее добавлены еще один многоэмиттерный транзистор Т6 и соединенный с его коллектором транзистор Т5 (включенный параллельно транзистору Т2), что позволяет осуществить функцию ИЛИ. Оба транзистора имеют одну и ту же нагрузку и отпирание любого из них запирает выходной транзистор Т4 и отпирает транзистор ТЗ, в результате чего на выходе схемы устанавливается низкий уровень напряжения.

Схема имеет две модификации: 1ЛР551 (состоит из двух логических элементов, каждый из которых содержит две двухвходовые схемы И, объединенные схемой ИЛИ); ЛР553 (имеет четыре схемы И с общим числом входов равным девяти).

Рис.2.6 Схема И—ИЛИ—НЕ (а) и подключение к этой схеме расширителя (б).

К входам К и Э подключают расширитель по ИЛИ (рис. 2.6, б), представляющий собой многоэмиттерный транзистор T1 и соединенный с ним транзистор Т2. Расширитель имеет две модификации: 1ЛП551 (содержит два четырехвходовых элемента); 1ЛП533 (содержит восьмивходовый элемент).

Условные графические изображения интегральных микросхем показаны на рис. 2.7. Входы микросхемы располагаются слева, выходы — справа. Функции И, ИЛИ изображаются прямоугольником с соответствующим обозначением функции (обозначение &-И, 1-ИЛИ). Функция НЕ обозначается кружочком. Обозначения двух-, трех-, четырех- и восьмивходовых схем И —НЕ (микросхемы 1Л551 — 1Л558) приведены на рис. 2.7, а —г, а обозначения схем И — ИЛИ —НЕ (микросхемы 1Л551—1ЛР554) —на рис. 2.7, д — ж.

Кроме схем И —НЕ, И —ИЛИ —НЕ в серии К155 предусмотрено два типа триггеров. Микросхема 1ТК551 представляет IК -триггер (рис. 2.7, з), имеющий вход S установки единицы и вход R установки нуля. При подаче на входы S и R нуля триггер устанавливается в соответствующее состояние. Триггер имеет два выхода — прямой (Q) и инверсный ( ). Если триггер находится в состоянии единицы, то на выходе Q — единица, а на выходе

). Если триггер находится в состоянии единицы, то на выходе Q — единица, а на выходе  — нуль; если в состоянии нуль, то на выходе Q — нуль, а на выходе

— нуль; если в состоянии нуль, то на выходе Q — нуль, а на выходе  —единица.

—единица.

Отличительной особенностью IК -триггера является наличие входов I и К, а также тактового входа T. При использовании тактового входа Т на входы S и R подаются единицы. Если на все входы I и К подаются единицы, единичный импульс по входу Т переводит триггер в противоположное состояние (аналогично действию импульса на счетном входе потенциально-импульсного триггера), т. е. из состояния «единица» в состояние «нуль», а из состояния «нуль» в состояние «единица». Если хотя бы на один из входов К, подан нуль, а на входах I единицы, импульс по тактовому входу может перевести триггер только в состояние «нуль». Если хотя бы на один из входов I подан нуль, а на входах К единицы, триггер может быть переведен только в состояние «единица». Если нули подаются одновременно на любые из входов I и К, состояние триггера под действием тактовых импульсов не меняется. Временная диаграмма работы IK -триггера под действием импульсов, подаваемых на вход Т, приведена па рис. 2.8. В одном корпусе размещается один К -триггер. С помощью IK -триггеров строятся схемы счетчиков и регистров сдвига, причем принцип их построения аналогичен принципу построения этих схем на потенциально-импульсных триггерах со счетным входом.

Рис. 2.7. Условные графические изображения интегральных микросхем:

а —г схемы — И —НЕ, д — ж схемы— И — ИЛИ —НЕ, з — к — триггеры

Микросхема 1ТК552 представляет собой D -триггер (рис. 2.7, и), имеющий вход S установки единицы, вход R установки нуля, а также вход D и тактовый вход Т. При подаче на вход Т положительного импульса триггер переводится в состояние, аналогичное значению сигнала на входе D. Если в момент прихода импульса на вход Т и на вход D подана единица, то триггер устанавливается в состояние «единица», если нуль — в состояние «нуль». Временная диаграмма работы D-триггера приведена на рис. 2.9 (в одном корпусе располагаются две схемы D-триггеров).

Микросхема 155ТМ5 имеет повышенную степень интеграции и содержит четыре D-триггера, каждый из которых имеет вход D и выход Q; вход D подается сразу на два триггера (рис. 2.7, к).

В последних разработках систем ЧПУ находят применение микросхемы средней степени интеграции, содержащие в одном корпусе десятки схем И, ИЛИ, НЕ. С помощью этих схем в одном корпусе содержатся целые функциональные узлы — регистры сдвига, счетчики, сумматоры, дешифраторы. Условные графические изображения некоторых из этих схем приведены на рис. 2.10.

Рис. 2.8 Временная диаграмма работы IK -триггера

Рис. 2.9 Временная диаграмма работы D -триггера

Рис. 2.10 Условные графические изображения микросхем средней степени интеграции:

а — регистр сдвига, б — двоично-десятичный счетчик, в — дешифратор индикации

Схема RG (рис. 2.10, а) представляет собой регистр сдвига на четыре разряда. Входы (слева) и выходы (справа) этих разрядов обозначаются как 1, 2, 4, 8. По входу МС задается режим управления (занесение информации с входов 1, 2, 4, 8 или сдвиг). Входы С 1, С2 являются входами синхронизации; операции (занесение или сдвиг) производятся по импульсам, поступающим на эти входы. Вход МС является входом регистра сдвига.

Схема СТ2-10 (рис.2.10, б) представляет собой реверсивный декадный счетчик, работающий в двоично-десятичном коде. Входы 1, 2, 4, 8 служат для параллельного занесения информации в счетчик. По входу W подается импульс занесения в счетчик информации с входов 1, 2, 4, 8. По входу R подается импульс установки счетчика в нуль. Импульс по входу +1 увеличивает число, содержащееся в счетчике на единицу. Импульс по входу —1 уменьшает это число на единицу. Выход Р+ является выходом переноса в старший разряд и регистрирует переполнение счетчика под (переход счетчика из состояния 9(1001) к состоянию нуль (0000). Выход Р— является выходом займа из старшего разряда.

Схема DC > (рис. 2.10, а) является дешифратором цифровой индикации. Она дешифрирует подаваемый на ее входы 1, 2, 4, 8 двоично-десятичный код числа и в соответствии с этим кодом открывает один из выходов 0—9. Эти выходы выдерживают высокое напряжение (до 60 В) и могут быть подсоединены непосредственно ко входам газоразрядной индикаторной лампы.

Date: 2016-02-19; view: 2682; Нарушение авторских прав