Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Назначение сигналов процессоров 8086/8088 в максимальном режиме

| Сигнал I/O Назначение |

| AD[0:7] I/O Address/Data — мультиплексированные сигналы шины адреса и данных. Адрес присутствует в начале каждого шинного цикла. В PC эти сигналы через регистр-защелку выводятся на линии Addr[0:7] шины адреса и двунаправленным буферным регистром соединяются с линиями Data[0:7] шины данных. У процессора 8086 мультиплексирована 16-разрядная шина А0[0:15] |

| A[8:15] О Address — сигналы шины адреса, не мультиплексированные у процессора 8088. В PC эти сигналы через регистр-защелку выводятся на линии Addr[8:15] |

| Сигнал I/O Назначение |

| A[16:19]/S[3:6] О Address/Status — старшие биты шины адреса, мультиплексированные с сигналами состояния. Адрес присутствует в начале каждого шинного цикла, после чего сменяется признаками состояния. В битах состояния S6=0, S5 отражает состояние флага прерываний IF, S4 и S3 указывают, какой сегментный регистр используется в данном цикле. В PC информация состояния не используется, а эти сигналы через регистр-защелку поступают на линии Addr[16:19] шины адреса |

| CLK I Clock — сигнал синхронизации процессора частотой 4,77 МГц (8 Мгц в Turbo-XT) |

| RQ/GTO I/O Request/Grant — сигнал запроса (Request) и предоставления (Grant управления локальной шиной, используется для связи с сопроцессором 8087 |

| RQ/GT1 I/O Аналогично RQ/GT0, но с меньшим приоритетом. В PC не используется (на него подается лог. 1) |

| LOCK О Сигнал монополизации управления шиной, вырабатывается на время выполнения команды по префиксу инструкции LOCK |

| NMI I Non Mascable Interrupt — сигнал, высокий уровень которого вызывает немаскируемое прерывание NMI. В PC сигнал на вход NMI поступает от сопроцессора, схемы контроля паритета памяти и сигнала ошибки канала IOCHK через ключ, управляемый битом 7 регистра 0A0h |

| INTR I Interrupt Request — сигнал запроса (высоким уровнем) маскируемого прерывания. В PC поступает с выхода контроллера прерываний i8259A Ц |

| READY I Сигнал подтверждения завершения обмена данными с адресуемой памяти или портом ввода/вывода (готовность). Низкий уровень вызывает появление тактов ожидания (Wait States) во время фазы шинного цикла. Синхронизированный сигнал готовности поступает через микросхему i8284 с линии IOCHRDY системной шины PC |

| RESET I Сигнал аппаратного сброса (высоким уровнем). Синхронизированный сигнал сброса поступает через микросхему i8284 от сигнала POWER GOOD вырабатываемого блоком питания, и кнопки RESET |

| QS0, QSl 0 Queue Status — состояние внутренней очереди команд. В PC эти сигналы поступают на одноименные входы сопроцессора 8087 |

| S[0:2] О Status — сигналы состояния, идентифицирующие выполняемый шинный цикл. Начало и конец цикла индицируются переходом бит состояния из пассивного (111) в активное состояние и обратно. Сигналы поступают на входы контроллера шины i8288, который их декодирует в сигналы состояния системной шиной I0R#, I0W#, MEMR#, MEMWR#, INTA# и ALE |

| BHE#/S7 О Byte High Enable/Status 7 (только для процессора 8086). Сигнал BHE указывает на присутствие данных на линиях AD[8:15] |

Табл.

| ST2 | ST1 | ST0 | Тип машинного цикла |

| Обслуживание прерывания | |||

| Чтение ВУ | |||

| Запись ВУ | |||

| Останов | |||

| Извлечение кода команды | |||

| Чтение ЗУ | |||

| Запись ЗУ | |||

| Пассивное состояние |

Разряды статуса 3..4 определяют сегментный регистр, используемый для вычисления физического адреса:

Табл.

| ST4 | ST3 | Сегментный регистр |

| ES | ||

| CS | ||

| SS | ||

| DS |

ST[5] отражает состояние флага разрешения прерывания IF, ST[6] всегда установлен в 0, когда МП обменивается информацией по магистрали, состояние ST[7] не определено (зарезервировано).

Сигналы QS[1:0] формируются только в максимальном режиме и отражают состояние очереди команд:

Табл.

| QS1 | QS0 | Состояние очереди команд |

| Нет операции | ||

| Очередь очищается | ||

| Извлекается первый байт | ||

| Извлекается очередной байт |

Практически все команды МП i8086 могут работать как со словами (2 байта) так и с байтами. При работе со словами сигнал BHE\ разрешает передачу старшего байта слова.

Сигнал STB отмечает наличие на линиях A/D и A/S адреса.

R и W\ стробируют данные на шине A/D соответственно при чтении и записи.

M-IO\ и OP-IP\ определяют соответственно устройство, с которым производится обмен (память - ВУ) и направление передачи информации (вывод - ввод) относительно процессора.

DE\ стробирует внешний буфер A/D при передаче данных.

Вход TEST\ предназначен для синхронизации программы с внешними процессами. Команда WAIT (ожидание) переводит процессор в режим ожидания, в котором он будет находиться до тех пор, пока на входе TEST\ удерживается высокий уровень сигнала (лог. "1"). При этом все магистрали МП переводятся в высокоимпедансное состояние.

RDY - (готовность) аналогично соответствующему входу МП i8080 обеспечивает возможность асинхронного машинного цикла.

CLR - (сброс) устанавливает все регистры МП в 0, кроме CS, который устанавливается в FFFF и осуществляет запуск командного цикла. Таким образом, стартовый адрес i8086 - всегда FFFF0.

CLC - тактовый сигнал.

INT, INTA\ - соответственно запрос и подтверждение вешнего прерывания (подробнее см. раздел 7).

NMI - запрос внешнего немаскируемого прерывания по фиксированному вектору 2.

HLD, HLDA - соответственно требование и предоставление прямого доступа в память (работает аналогично подсистеме ПДП i8080). В максимальном режиме вместо сигналов HLD, HLDA используются две двунаправленные линии RQ\/Ei\ - запрос шины/разрешение доступа, на которые работает специальная микросхема - арбитр шины.

Временные диаграммы работы МП i8086 в минимальном режиме представлены на Рис.

| Т1 |

| Т2 |

| Т3 |

| A[19:16] |

| CLK |

| Т4 |

| Тw |

| ST7.. ST3 |

| M/IO |

| BHE A/ST |

| ALE |

| A[15:0] |

| DI[15:0] |

| A/D [15:0] |

| RD |

| OP-IP |

| DEN |

Минимальный режим – цикл ЧТЕНИЕ

| Т1 |

| Т2 |

| Т3 |

| A[19:16] |

| CLK |

| Т4 |

| Тw |

| ST7.. ST3 |

| M/IO |

| BHE A/ST |

| ALE |

| A[15:0] |

| D0[15:0] |

| A/D [15:0] |

| WE |

| DEN |

| OP-IP |

Минимальный режим – цикл ЗАПИСЬ

Цикл начинается с формирования в T1 сигнала M/IO, определяющего тип устройства - память или ВУ, с которым осуществляется обмен данными. Длительность сигнала M/IO равна длительности цикла шины, и он используется для селекции адреса устройств. В T1 и в начале T2 МП выдает адрес A[19:16] и A[15:0] и сигнал BHE, который вместе с A0 определяет передачу слова или одного из байтов. По спаду строба ALE адрес фиксируется во внешних регистрах-защелках.

В такте T2 происходит переключение шин: на выводы A[19:16]/ ST[6:3] поступают сигналы состояния; выводы A/D[15:0] в цикле ЧТЕНИЕ переводятся в высокоимпедансное состояние, а в цикле ЗАПИСЬ - на них выдаются данные, предназначенные для записи в устройство.

Циклы ЧТЕНИЕ и ЗАПИСЬ отличаются не только активными значениями сигналов RD и WR и состоянием сигнала OP/IP, но и тем, что в цикле ЗАПИСЬ сигналы DEN и WR становятся активными раньше и имеют большую длительность, чем в цикле ЧТЕНИЕ.

Структура процессорных модулей на базе МП i8086 существенно зависит от выбранного режима работы МП.

Процессорный модуль работает аналогично процессорному модулю на базе i8080, но управляет памятью большего объема и может осуществлять обмен двухбайтовыми словами.

| AB[19:0] |

| A/D[15:0] |

| A/D A/ST OP-IP R W M-IO STB HLDA DEN |

| CPU |

| MIN/MAX |

| “1” |

| A T OE |

| BD (2) |

| B |

| D C OE |

| RG (3) |

| Q |

| DB[15:0] |

| OE OE |

| L |

| RDM |

| WRM |

| RDIO |

| WRIO |

Процессорный модуль на базе 8086 в минимальном режиме

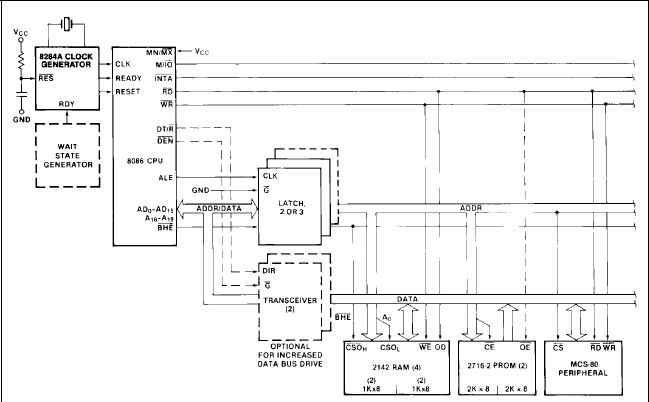

Микропроцессорная система на базе 8086 в минимальном комплекте

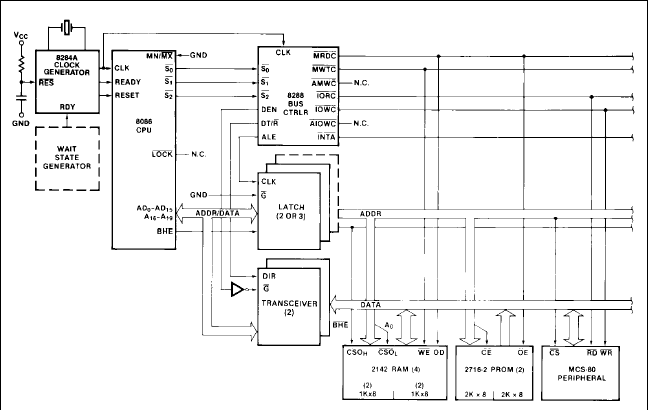

Микропроцессорная система на базе 8086 в максимальном комплекте

Лекция 53

Микропроцессор МП 8086. Архитектура МП 8086

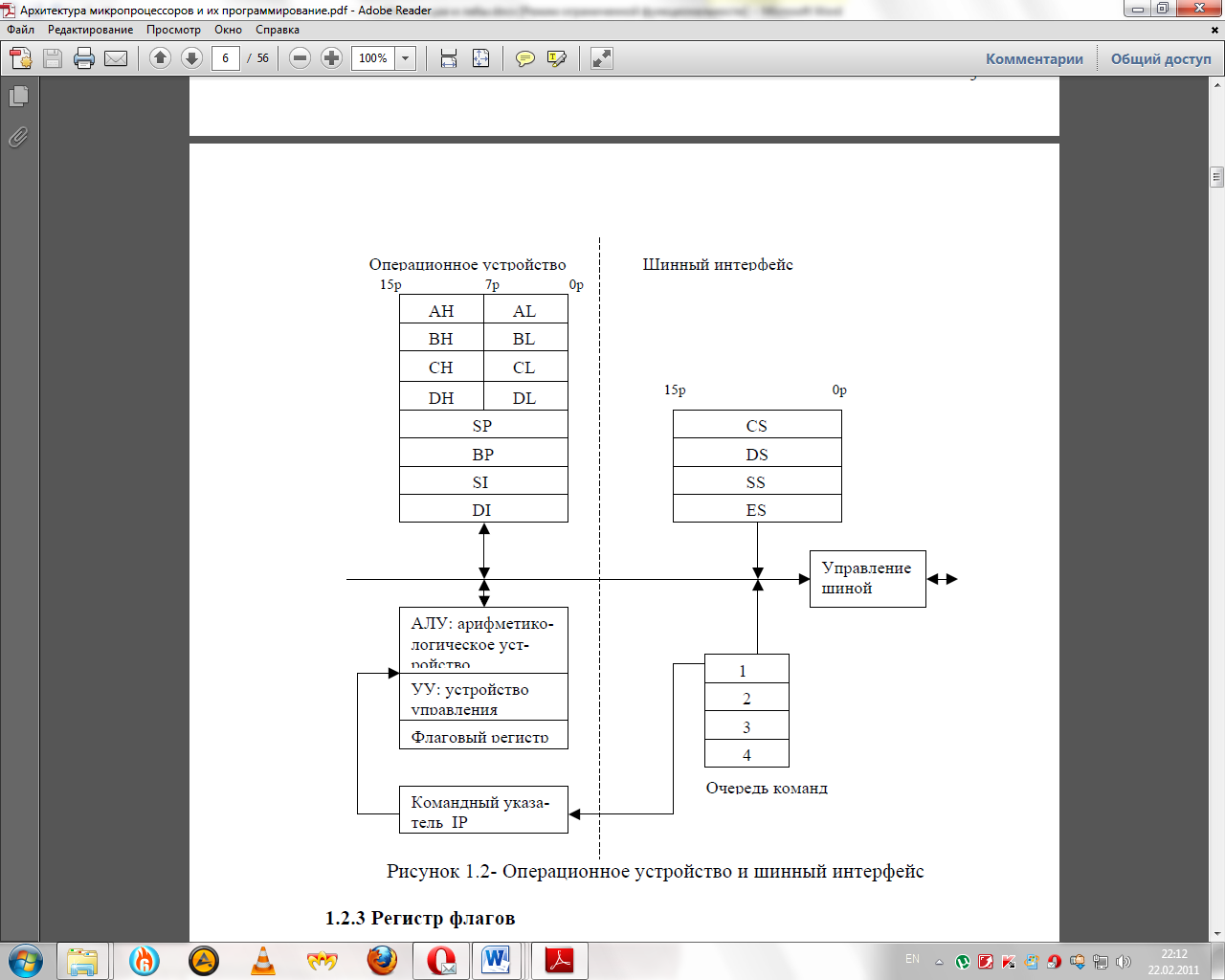

Архитектура МП Intel 8086 в упрощённом виде представлена на рисунке 1. С функциональной точки зрения МП можно разделить на две части: операционное устройство и шинный интерфейс. Все компоненты МП взаимодейст-

вуют между собой посредством систем шин: адресных (16 разрядов), данных (8 разрядов) и управления. В процессоре 8086 имеется несколько быстрых элементов памяти на интегральных схемах, которые называются регистрами. Каждый из регистров предоставляет определенные возможности, которые другими регистрами или ячейками памяти не поддерживаются.

Регистры разбиваются на четыре категории (см. рисунок 1.2):

- регистр флагов:

- регистры общего назначения АХ, ВХ, СХ, DX, BP, SP, DI и SI;

- указатель инструкций IP:

- сегментные регистры CS, SS, DS и ES.

Рисунок 1

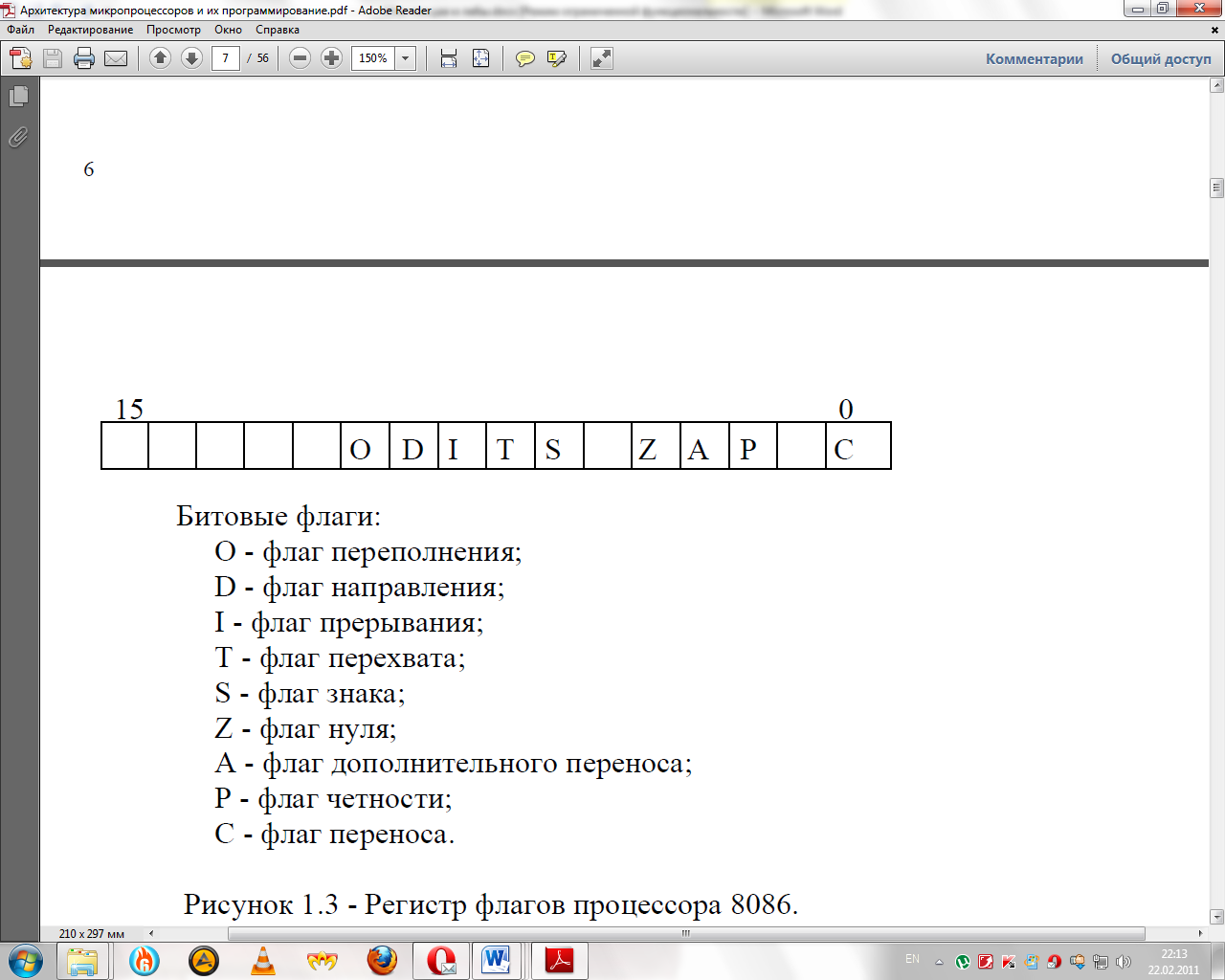

Регистр флагов

Регистр флагов - это 16-разрядный (16-битовый) регистр содержит всю необходимую информацию о состоянии процессора 8086 и результатах последних инструкций (рисунок 2).

Например, если вы хотите знать, получен ли при вычитании нулевой результат, непосредственно после этой инструкции вам следует проверить флаг нуля (бит Z в регистре флагов). Если он установлен (то есть имеет ненулевое значение), это будет говорить о том. что результат нулевой. Другие флаги, такие, как флаги переноса и переполнения аналогичным образом сообщают о результатах арифметических и логических операций.

Другие флаги управляют режимом операций процессора 8086. Флаг направления управляет направлением, в котором строковые инструкции выполняют перемещение, а флаг прерывания управляет тем. будет ли разрешено внешним аппаратным средствам.

Рисунок 2 - Регистр флагов процессора 8086.

Битовые флаги:

O - флаг переполнения:

D - флаг направления:

I - флаг прерывания:

Т - флаг перехвата:

S - флаг знака:

Z - флаг нуля:

А - флаг дополнительного переноса:

Р - флаг четности:

С - флаг переноса.

Так. например, клавиатура или модем, могут временно приостанавливать текущий код для выполнения функций, требующих немедленного обслуживания. Флаг перехвата используется только программным обеспечением, которое служит для отладки другого программного обеспечения (отладчики).

Регистр флагов не считывается и не модифицируется непосредственно. Вместо этого регистр флагов управляется в общем случае с помощью специальных инструкций (таких, как CLD, STI и CMC), а также с помощью арифметических и логических инструкций, модифицирующих отдельные флаги. И наоборот, содержимое отдельных разрядов регистра флагов влияет на выполнение инструкций (например. JZ, RCR и MOVSB). Регистр флагов не используется на самом деле, как ячейка памяти, вместо этого он служит для контроля за состоянием и управления процессором 8086.

Date: 2016-07-18; view: 492; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |