Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Центральный Процессор (ЦП)

F2833x – ЦП может выполнять большинство инструкций типа регистр – регистр и типовые инструкции контроллера, например, операции с байтами и битами в единственном машинном цикле. Архитектура также снабжена мощными способами адресации, которые позволяют компилятору и ассемблерному программатору производить компактный код, который почти переписывается один к одному с кодом C.

F2833x эффективен в типичных математических задачах для цифрового сигнального процессора, а также в системах управления, которыми обычно управляют микроконтроллерные устройства. Это позволяет исключить потребность во втором микропроцессоре во многих установках.

Функциональная схема ЦП приведена на рисунке 2.2.

ЦП включает в себя следующие основные блоки:

– блок управления потоком команд (рганизует последовательность

выполнения команд программы);

– блок генерации адреса команд (формирует адрес на шине команд);

– арифметический модуль адресных регистров (АRAU);

– атомарное арифметико–логическое устройство (АLU);

– умножитель с фиксированной запятой;

– регистры центрального процессора.

Модуль АRAU генерирует значения адресов для обмена с памятью данных. Полученные значения помещаются на шины адреса чтения и записи данных. Модуль также отвечает за увеличение/уменьшение значения в регистре – указателе стека (SР), а также вспомогательных регистров (ХАR0…ХАR7).

АLU выполняет 2–операндные арифметические и логические операции. Операнды в АЛУ поступают из регистров, памяти или из блока управления потоком ииструкций. Результат может быть сохранен в регистре или памяти данных..

Умножитель выполняет перемножение двух операндов вида 32х32 с 64–битным результатом. Помимо самого умножителя для выполнения операции умножения задействованы также регистр множимого (ХТ), регистр произведеиия (Р), аккумулятор (АСС). Результат может быть получен либо в регистре ХТ, либо в аккумуляторе. Умножитель взаимодействует непосредственно с АLU.

Регистры центрального процессора используются для промежуточного хранения данных при вычислениях.

Функциональная схема умножителя с фиксированной точкой и ALUпоказана на рисунке 2.3.

32– на 32–разрядный с фиксированной точкой “Multiply and Accumulate (MAC)” F2833x и его внутренний 64–битный процесс, дают возможность этому DSC эффективно манипулировать с большими числами. К тому же, если данные и коэффициенты запоминаются как двоичные числа длиною в 16 бит или меньше, этот контроллер может выполнять две 16–на 16–бит МАС инструкции одновременно. Терминология для таких инструкций «Двойной Многократный и Накапливающий (DMAC)».

Умножитель использует регистр XT ("eXtended Temp"), чтобы хранить первый операнд и умножает его на второй операнд, который загружается из запоминающего устройства. Если XT загружен из запоминающего устройства данных, а второй операнд извлекается из программного запоминающего устройства то умножение выполняется за один цикл. Результат умножения помещается в регистр P («Продукт») или непосредственно в Аккумулятор (ACC). Если умножить 32–бита на 32–бта то результат будет 64–бита. Система команд F2833x включает две группы операций умножения, чтобы запомнить две 32–разрядных части в P и ACC. Таким образом, мы можем сказать, что регистры ACC и P комбинируются и формируют единственный 64–разрядный регистр.

Три аппаратных сдвиговых регистра (Shift) могут использоваться в параллели с другими аппаратными устройствами ЦП. Сдвиговые регистры обычно используются как промежуточное звено при выполнении в реальном времени умножения/деления на число типа 2n.

Арифметическое Логическое Устройство (ALU) выполняет все другие математические операции кроме умножения. Первый операнд – всегда содержимое Аккумулятора (ACC) или его части. Второй операнд загружается из запоминающего устройства данных, из программного запоминающего устройства, из P регистра или непосредственно из умножителя.

Рисунок 2.2 – Функциональная схема ЦП

Чтобы добавить больше гибкости устройству, используя точность данных c плавающей точкой в C, инженеры Texas Instruments Incorporated добавили в семейство F2833x второй аппаратный умножитель показанный на рисунке 2.4.

Правая сторона рисунка 2.4 все (floating–point) регистры модуля арифметики с плавающей точкой. 8 регистров общего назначения (R0H – R7H), поддерживающий их регистр (STF) статуса и регистр повторений (RB). Последний используется, чтобы выполнять группу элементов машинного кода без потребности в программном обеспечении. Такая технология позволяет конвейеру команд CPU работать быстрее.

Рисунок 2.3 – Функциональная схема умножителя с фиксированной точкой и ALU

Рисунок 2.4 – Функциональная схема регистров арифметических модулей

Левая часть рисунка 2.4 показывает регистры модуля с фиксированной точкой. Он состоит из 3–х регистров ЦП: Аккумулятор (ACC), регистр результата (P) и регистр временного хранения (XT), 8 регистров общего назначения (XAR0.XAR7) и набор регистров управления и статуса, «Программный счетчик» (РС), «Указатель страницы данных» (DP), «Указатель вершины стека» (SP), «Разрешение Прерываний» (IER), «Флаги прерываний» (IFR) и «Разрешение отладочных прерываний" (DBGIER).

Доступны Два основных метода обращения к запоминающему устройству данных:

– способ прямой адресации;

– способ косвенной адресации.

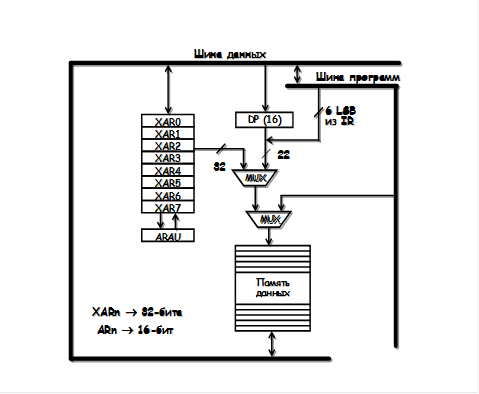

Схема формирования адреса данных показана на рисунке 2.5.

Способ прямой адресации создает 22–разрядный адрес для выборки из запоминающего устройства данных от двух источников: 16–разрядного регистра указателя страницы (DP) –16 старших битов плюс 6 битов, взятых из инструкции.

Рисунок 2.5 – Схема формирования адреса

Преимущество. Как только DP установлен, мы можем обратиться к отобранной странице в любом порядке.

Недостаток. Если есть необходимость обратиться к другой странице, DP должен быть сначала изменен.

Способ косвенной адресации использует один из восьми, 32–разрядных XARn регистров, чтобы хранить 32–разрядный адрес операнда. С помощью ARAU, и арифметической операции над указателями доступно изменение адреса в том же цикле.

Но при случайном обращении к запоминающему устройству данных нужна загрузка регистра указателя новым значением.

Вспомогательное арифметическое устройство (ARAU) может выполнять манипулирование указателями в том же цикле, что и обращение к запоминающему устройству данных. Варианты операций ARAU: пост–инкремент, пре–декремент, индексное сложение и вычитание, операции со стеком, циклическая адресация и бит–реверсивная адресация с дополнительными вариантами.

Атомарные инструкции являются встроенными в контроллер системами. Примерами являются логические операции, такие как AND, OR и EXOR непосредственно осуществляющиеся с памятью данных.

Как правило, эти инструкции должны быть выполнены без перерыва между чтением и записью, они называются "бесперебойными" или "атомарными" инструкциями. В F2833x атомарное Арифметико–логическое устройство (АЛУ) поддерживает такие типы инструкций; как показано на правой части рисунка 2.6.

При традиционном кодировании (левая часть рис. 2.6) инструкция будет выполняться на несколько циклов медленнее, чем атомарные инструкции.

Рисунок 2.6 – Атомарные функции чтения/модификации/записи

Date: 2015-06-06; view: 737; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |