Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Схемы сравнения на равенство

Таблица 5.1

| Е(t) | Т(t) |

|

| c |

| |

| c |

|

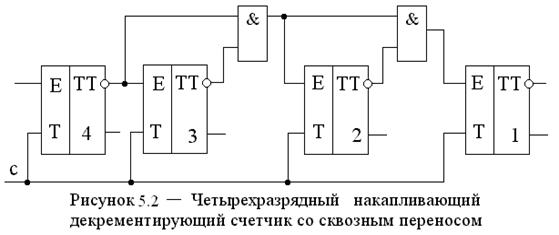

Вычитающий счетчик будет отличаться от суммирующего только тем, что перенос в следующий старший разряд будет определяться инверсным значением предыдущих разрядов (то есть в данном случае сигнал переноса будет сниматься не с прямого, а с инверсного выхода соответствующего триггера).

Результат микрооперации счета является действительным через промежуток времени tсчета = 4tтр с момента подачи в схему синхроимпульса, где tтр – время переключения триггера. Это объясняется тем, что триггеры срабатывают последовательно. Отсюда следует, что период тактирующей серии импульсов (такт операционного автомата) для стабильной работы счетчика должен превышать указанное время.

Для увеличения быстродействия счетчика применяются схемы со сквозным и параллельным переносом. В этих схемах синхросигнал подается параллельно на Т-входы всех триггеров, т.е. все триггеры переключаются одновременно. К моменту переключения триггеров на логических элементах формируются межразрядные переносы по формуле:

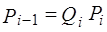

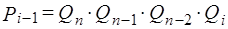

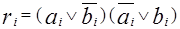

, i = n, n-1, n-2,…1 (для n-разрядного счетчика со сквозным переносом),

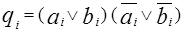

, i = n, n-1, n-2,…1 (для n-разрядного счетчика со сквозным переносом),

(для n-разрядного счетчика с параллельным переносом), где Pi – перенос в i -ый разряд триггера, Qi – прямой выход i -го триггера.

(для n-разрядного счетчика с параллельным переносом), где Pi – перенос в i -ый разряд триггера, Qi – прямой выход i -го триггера.

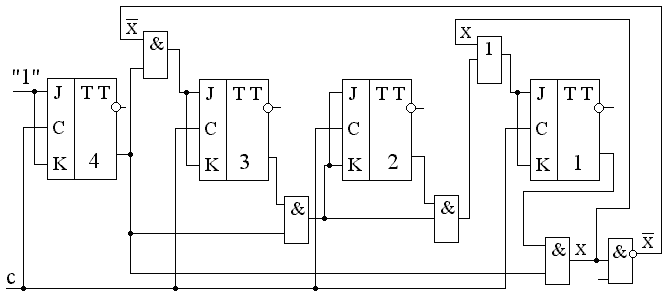

Приведенные выше формулы справедливы для суммирующих счетчиков. В соответствующие формулы для вычитающих счетчиков сигналы  войдут с инверсией (будут сниматься с инверсных входов триггеров). Функциональная схема четырехразрядного вычитающего счетчика со сквозным переносом приведена на рисунке 5.2. В этой схеме tсчета = tтр+2tкс, где tкс- время задержки комбинационной схемы, формирующей сигнал переноса. Для счетчика с параллельным переносом tсчета = tтр+ tкс.

войдут с инверсией (будут сниматься с инверсных входов триггеров). Функциональная схема четырехразрядного вычитающего счетчика со сквозным переносом приведена на рисунке 5.2. В этой схеме tсчета = tтр+2tкс, где tкс- время задержки комбинационной схемы, формирующей сигнал переноса. Для счетчика с параллельным переносом tсчета = tтр+ tкс.

Обратите внимание, что в схеме используются двухступенчатые триггеры. Первая ступень двухступенчатого триггера синхронизируется, как правило, прямым значением синхросигнала и, следовательно, срабатывает по нарастающему фронту синхроимпульса (будем называть его просто фронтом), вторая ступень синхронизируется инверсным значением синхросигнала и соответственно срабатывает по ниспадающему фронту синхроимпульса (будем называть его срезом). Следовательно, переключение JK-триггера осуществляется по ниспадающему фронту (срезу) синхроимпульса (это необходимо учитывать при построении временных диаграмм счета).

Преимущество двухступенчатых элементов памяти состоит в том, что момент приема информации на триггер с его входов (срабатывание первой ступени) и момент выдачи информации на выходы триггера (срабатывание второй ступени) разделены во времени (на время длительности синхроимпульса минус время срабатывания первой ступени триггера). Это позволяет схемам, в которых используется двухступенчатая память, работать устойчиво, когда один и тот же запоминающий элемент (триггер) в одном и том же такте является и источником и приемником информации. Примером может служить рассматриваемая схема счетчика (рисунок 5.2). По фронту синхроимпульса в схеме счетчика переключаются первые ступени всех триггеров в соответствии со сформированными на логических элементах (вентилях) сигналами межразрядных переносов (длительность синхроимпульса должна быть больше, чем время переключения первой ступени триггеров). Переключение осуществится корректно, т. к. во время длительности синхроимпульса информация на выходах триггеров (выходах второй ступени), используемых для вычисления сигналов переноса, не изменяется. По срезу синхроимпульса информация с первой ступени триггеров переписывается на вторую ступень. Следующее срабатывание схемы произойдет по следующему синхроимпульсу.

Постройте временные диаграммы работы схем, изображенных на рисунках 5.1 и 5.2, и убедитесь, что эти схемы действительно выполняют микрооперацию счета.

Если речь идет о синтезе счетчиков, считающих в заданной системе счисления (по заданному модулю), то необходимо синтезировать счетчик, считающий по модулю q, где q – основание системы счисления. Например, нужно синтезировать двоичный счетчик, считающий по модулю 10 (q=10). В этом случае разрабатывается m-разрядный двоичный счетчик  , обеспечивающий переключение из состояния (q-1) в состояние 0 для инкрементирующего режима и из состояния 0 в состояние (q-1) для декрементирующего режима.

, обеспечивающий переключение из состояния (q-1) в состояние 0 для инкрементирующего режима и из состояния 0 в состояние (q-1) для декрементирующего режима.

Пусть требуется синтезировать инкрементирующий накапливающий двоичный счетчик по модулю десять (q=10) с параллельным переносом. Для реализации такого счетчика необходимо четыре триггерных элемента (m=4). I-ый разряд накапливающего счетчика можно реализовать на JK-триггере серии 74НС (вспомните одно из заданий первой лабораторной работы: синтезировать T-триггер на JK-триггере).

Пусть кроме микрооперации счета операционный элемент будет выполнять микрооперации сброса у0: С(1:4):=0000 и установки у1: С(1:4):=0101 и выдавать осведомительный сигнал x=(С(1:4):=0000).

Таблица истинности JK-триггера с установочными RS-входами, изображенного на рисунке 5.3, - таблица 5.2.

На основе анализа таблиц 5.1 и 5.2 можно обосновать организацию Е-входа путем объединения J и K входов. При таком объединении на J и K вход триггера будет поступать один и тот же сигнал. Если этот сигнал равен нулю, триггер хранит свое состояние, в противном случае триггер переключается в противоположное состояние по срезу синхроимпульса, поступившего на вход С (используется в качестве тактового входа Т), согласно таблице 5.2.

Таблица 5.2

|

|

|

|

|

|

| X | X | X | Не определено | ||

| X | X | X | |||

| X | X | X | |||

| X | X |

| |||

| |||||

|

Пусть микрооперация счета инициируется управляющим сигналом y2. Тогда для организации параллельного переноса на С-входы всех триггеров необходимо подать сигнал  , а JK-входы использовать для подачи межразрядного переноса.

, а JK-входы использовать для подачи межразрядного переноса.

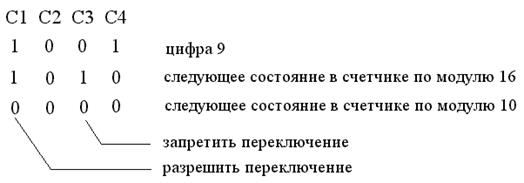

Обычный суммирующий четырехразрядный двоичный счетчик автоматически устанавливает комбинацию 0000 после комбинации 1111 (15 в двоичной системе). Это счетчик по модулю 16.

Суммирующий двоичный счетчик по модулю 10 (основание системы счисления) должен считать от 0000 до 1001 (9 в двоичной системе счисления), а затем сбрасываться в 0000. Сброс счетчика можно осуществлять по установочным RS-входам при помощи сигнала xmod = (C(1:4)=1010). При этом комбинация 1010 будет появляться на выходах регистра кратковременно (tтр+ tкс), что не повлияет на логику работы схемы, хотя может сказаться на надежности. Другими словами, при переходе счетчика из состояния 1001 в состояние 0000 через состояние 1010, присутствующее на выходах счетчика в течение времени выработки осведомительного сигнала и времени переключения триггеров, на выходе Q3 возникает кратковременный остроконечный импульс, вызывающий переходный процесс.

Построим таблицу зависимости функций возбуждения RS-входов от управляющих сигналов и сигнала xmod (таблица 5.3).

Таблица 5.3

| y | R1 | S1 | R2 | S2 | R3 | S3 | R4 | S4 |

| у0 | ||||||||

| у1 | ||||||||

| xmod |

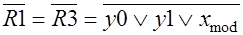

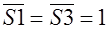

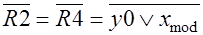

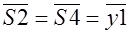

На основе данной таблицы строятся функции возбуждения входов.

;

;  ;

;

;

;

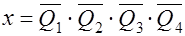

Осведомительный сигнал x=(С(1:4):=0000) может быть сформирован в соответствии с функцией

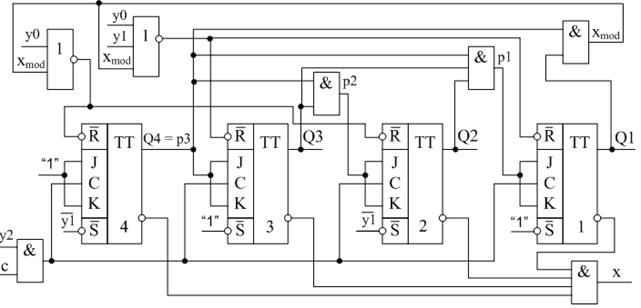

Схема счетчика приведена на рисунке 5.4. Постройте временные диаграммы работы счетчика, особое внимание уделите моменту переключения в из состояния 1001 в состояние 0000 через состояние 1010 (кратковременно присутствующее на выходах счетчика).

Примечание - Вычитающий счетчик по модулю 10 считает от 1001 до 0000, а затем устанавливается в 1001. Установку счетчика в состояние 1001 можно осуществлять по установочным RS-входам при помощи сигнала

xmod = (C(1:4)=1111). Недостаток организации счета по модулю при помощи RS-входов рассмотрен выше.

Рисунок 5.4 – Схема четырехразрядного накапливающего инкрементирующего

счетчика по модулю 10

Если для реализации счетчика используются двухступенчатые триггеры, как в рассмотренном примере, то для реализации модуля счета можно использовать синхронные JK-входы триггеров. Этот подход лишен недостатка, присутствующего при управлении по асинхронным установочным RS-входам. Управление модулем счета в суммирующем счетчике осуществляется максимально возможной цифрой (а не модулем счета), а в вычитающем счетчике – минимально возможной цифрой (т.е. нулем).

Схема суммирующего счетчика по модулю 10 с управлением по JK- входам приведена на рисунке 5.5 (в схеме реализована только микрооперация счета).

Рисунок 5.5 – Схема инкрементирующего счетчика С(1:4) по модулю 10

с управлением по JK-входам

Обычный четырехразрядный счетчик (по модулю 16) из состояния 1001 переходит в состояние 1010. Счетчик по модулю десять после состояния 1001 должен перейти в состояние 0000. Напомним, что в счетчике со сквозным или параллельным переносом сигнал переноса, переводящий (по очередному синхросигналу) схему в следующее состояние вычисляется на логических элементах исходя из текущего состояния счетчика. Поэтому, когда счетчик находится в состоянии 1001 (осведомительный сигнал  равен 1) нужно сделать равным нулю перенос в третий разряд (т.е. домножить перенос в третий разряд на

равен 1) нужно сделать равным нулю перенос в третий разряд (т.е. домножить перенос в третий разряд на  ) и сделать равным единице перенос в первый разряд (т.е. сложить перенос в первый разряд с

) и сделать равным единице перенос в первый разряд (т.е. сложить перенос в первый разряд с  ). Стратегия коррекции переносов для обеспечения модуля счета, равного 10 изображена на рисунке 5.6.

). Стратегия коррекции переносов для обеспечения модуля счета, равного 10 изображена на рисунке 5.6.

Рисунок 5.6. – Стратегия коррекции переносов

в инкрементирующем счетчике по модулю 10.

5.3. Содержание работы

В лабораторной работе необходимо разработать, собрать и отладить схему синхронного трехразрядного двоичного счетчика на JK-триггерах, считающего по модулю М (счетчик должен выполнять только микрооперацию счета). Тип счетчика, способ организации цепей переноса и модуль счета М определяются индивидуальным заданием. В ходе тестирования схемы нужно убедиться в правильности работы счетчика, подавая на его вход импульсы от генератора одиночных импульсов.

В последней части задания требуется разработать двухразрядный восьмеричный счетчик, соединив выход F/8 счетчика-делителя (старший восьмеричный разряд), имеющегося в составе макета «Trigger», и вход трехразрядного накапливающего суммирующего счетчика с последовательным переносом на раздельных JK-триггерах (младший восьмеричный разряд).

5.4. Варианты индивидуальных заданий

Варианты заданий приведены в таблице 5.4.

Таблица 5.4 – Варианты заданий для синхронного счетчика на JK-триггерах.

| № вар. | Тип счетчика | Способ распространения переноса | Модуль счета М |

| Вычитающий | Параллельный | ||

| Суммирующий | Сквозной | ||

| Суммирующий | Параллельный | ||

| Вычитающий | Сквозной | ||

| Вычитающий | Параллельный |

5.5. Внеаудиторная подготовка

5.5.1. Изучить классификацию счетчиков, методы их проектирования и схемные реализации: [1], стр. 308-318; [2], стр.128-140; [4], стр. 216-244; [5]. Обратить особое внимание на способы распространения переносов, т. к. они несколько отличаются от способов распространения переносов в комбинационных счетчиках.

5.5.2. Разработать схему трехразрядного накапливающего счетчика на раздельных JK-триггерах в соответствии с индивидуальным заданием (счетчик должен выполнять только микрооперацию счета). В качестве сигналов счета рекомендуется использовать синхроимпульсы. Провести анализ работы схемы.

5.5.3. Разработать схему трехразрядного накапливающего суммирующего счетчика с последовательным переносом на раздельных JK-триггерах.

Изучить микросхемы счетчиков К155ИЕ6, К155ИЕ7: [6], стр. 87-91. Эти микросхемы имеют аналоги в серии 74HC**. Одним из аналогов является счетчик-делитель, входящий в состав макета «Trigger».

5.5.4. Разработать двухразрядный восьмеричный счетчик, соединив выход F/8 счетчика-делителя (младший восьмеричный разряд), имеющегося в составе макета «Trigger», и вход трехразрядного накапливающего суммирующего счетчика с последовательным переносом на раздельных JK-триггерах (старший восьмеричный разряд).

5.6. Выполнение работы в лаборатории

Последовательно собрать и отладить счетчики, схемы которых разработаны в процессе домашней подготовки. Проверить их функционирование, подавая на вход импульсы с генератора одиночных сигналов. Двоичные счетчики проверить в динамическом режиме с помощью осциллографа, снять временные диаграммы.

5.7. Контрольные вопросы

5.7.1. Назовите характеристики быстродействия счетчика.

5.7.2. Сравните по быстродействию схемы с последовательным, сквозным и параллельным переносами.

5.7.3. В каких случаях целесообразно использовать цепи группового переноса?

5.7.4. Сформулируйте общий метод настройки счетчика на заданный модуль счета.

5.7.5. Как синтезировать счетчик, меняющий состояния в заданной последовательности? Синтезируйте трехразрядный счетчик, считающий в последовательности 0,3,5,2,7,0,3,....

6. ЛАБОРАТОРНАЯ РАБОТА №5. СХЕМЫ СРАВНЕНИЯ КОДОВ

6.1. Цель работы

Изучить способы формирования осведомительных сигналов A=B, A>B, получить навыки наладки и использования схем сравнения кодов, ознакомиться с описанием микросхем компараторов [2], стр. 157-167.

6.2. Краткие теоретические сведения

Схемой сравнения называется ОЭ, на котором вычисляется значение отношения между двумя позиционными кодами равной длины. Основными отношениями являются выражения  и

и  , которые в зависимости от значений операндов принимают значения ложь (0) или истина (1).

, которые в зависимости от значений операндов принимают значения ложь (0) или истина (1).

В микропрограммах отношения используются как логические условия и их значения представляются осведомительными сигналами, вырабатываемыми на выходе соответствующих схем сравнения в ОА. В зависимости от типа вычисляемых отношений выделяются:

1) схемы сравнения на равенство (неравенство), вычисляющие отношения  (

( );

);

2) схемы сравнения на больше (меньше), вычисляющие отношения  (

( ).

).

Нетрудно убедиться, что схема сравнения на равенство позволяет вычислять отношения  и

и  и схема сравнения на больше позволяет вычислять отношения

и схема сравнения на больше позволяет вычислять отношения  ,

,  ,

,  ,

,  . После ознакомления с данной главой объясните почему.

. После ознакомления с данной главой объясните почему.

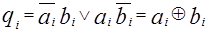

Схемы сравнения на равенство

Сравнение на равенство (неравенство) выполняется поразрядно над одноименными разрядами операндов. Операнды равны, если все одноименные разряды операндов имеют одинаковые значения. Операнды не равны, если хотя бы в одном разряде операнды имеют различное значение.

Значение признака равенства i-ых разрядов (i = 1, 2, …, n) сравниваемых слов  и

и  :

:

Значение признака неравенства i-ых разрядов сравниваемых слов:

(исключающее или – сложение по модулю 2)

(исключающее или – сложение по модулю 2)

Выше приведены функции в дизъюнктивной нормальной форме. Те же функции в конъюнктивной нормальной форме:

;

;

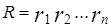

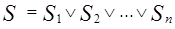

Признак равенства R двух n-разрядных двоичных слов  и

и  вычисляется как конъюнкция

вычисляется как конъюнкция

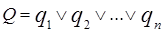

и признак неравенства Q – как дизъюнкция

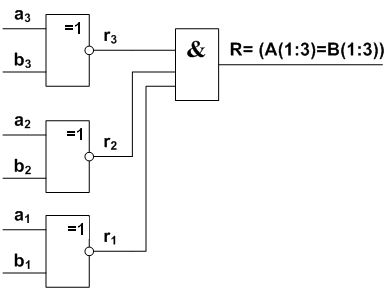

Схема сравнения R=(А(1:3)=В(1:3)) приведена на рисунке 6.1. Заметим, что на макете L-T всего два элемента «Исключающее Или» (=1). Третий можно спроектировать на основе элементов «И», «ИЛИ», «НЕ».

Рисунок 6.1 – Схема сравнения R=(А(1:3)=В(1:3))

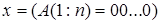

Микрооперация сравнения слов на равенство может выполняться на регистре, состоящем из триггеров со счетным входом. Регистр хранит код  . По управляющему сигналу

. По управляющему сигналу  на счетные входы регистра (входы, переключающие триггеры в противоположное состояние при поступлении на них активного уровня сигнала) подается код

на счетные входы регистра (входы, переключающие триггеры в противоположное состояние при поступлении на них активного уровня сигнала) подается код  , в результате чего регистр

, в результате чего регистр  устанавливается в состояние

устанавливается в состояние  . Если операнды

. Если операнды  и

и  равны, то регистр устанавливается в состояние

равны, то регистр устанавливается в состояние  , отмечаемое осведомительным сигналом

, отмечаемое осведомительным сигналом  , который после выполнения микрооперации

, который после выполнения микрооперации  сигнализирует о равенстве значений слов

сигнализирует о равенстве значений слов  и

и  .

.

Микрооперация сравнения слов на равенство может выполняться на сумматорах, если на момент выполнения микрооперации заблокировать цепи межразрядных переносов. При этом сумматор выполняет сложение операндов по модулю 2 и нулевое значение на выходе сумматора соответствует равенству операндов.

Схемы сравнения на больше (меньше)

Сравнение на больше  можно выполнять на сумматоре (или вычитателе) путем определения знака разности

можно выполнять на сумматоре (или вычитателе) путем определения знака разности  : если разность имеет отрицательный знак, то отношение

: если разность имеет отрицательный знак, то отношение  истинно, в противном случае оно ложно. Когда необходимость в использовании сумматора отсутствует и требуется вычислять отношения вида

истинно, в противном случае оно ложно. Когда необходимость в использовании сумматора отсутствует и требуется вычислять отношения вида  , целесообразно использовать схему сравнения, поскольку она экономичнее сумматора в смысле количества оборудования.

, целесообразно использовать схему сравнения, поскольку она экономичнее сумматора в смысле количества оборудования.

Вычисление отношения  между двумя n-разрядными словами

между двумя n-разрядными словами  и

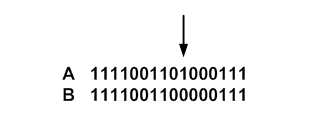

и  сводится к последовательному сравнению разрядов операндов, начиная от старших. Принцип сравнения ясен из рисунка 6.2.

сводится к последовательному сравнению разрядов операндов, начиная от старших. Принцип сравнения ясен из рисунка 6.2.

|

Рисунок 6.2 – Сравнение кодов «на больше»

Если в  -ом разряде (i = 1, 2, …, n) имеем

-ом разряде (i = 1, 2, …, n) имеем  , то отношение

, то отношение  истинно; если

истинно; если  , то отношение

, то отношение  ложно, и, если

ложно, и, если  или

или

, то значение отношения определяется путем анализа значений в следующем младшем разряде, а при

, то значение отношения определяется путем анализа значений в следующем младшем разряде, а при  отношение ложно. Определим булеву функцию, на основе которой может быть вычислено значение двоичной переменной

отношение ложно. Определим булеву функцию, на основе которой может быть вычислено значение двоичной переменной  , представляющей отношение

, представляющей отношение  . Пусть

. Пусть  - переменная, принимающая значение 1, если факт истинности отношения вытекает из анализа значений в разряде

- переменная, принимающая значение 1, если факт истинности отношения вытекает из анализа значений в разряде  .

.

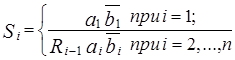

Из правила сравнения следует:

,

,

где  - признак равенства значений операндов в разрядах от

- признак равенства значений операндов в разрядах от  до

до  включительно и

включительно и  - признак равенства

- признак равенства  -ых разрядов сравниваемых кодов. Если

-ых разрядов сравниваемых кодов. Если  , то и

, то и  , т.е.

, т.е.

.

.

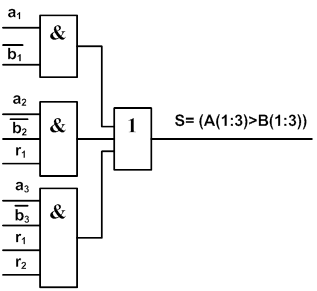

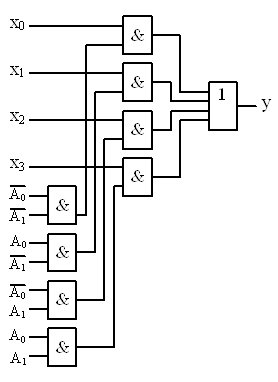

Схема сравнения S=(A(1:3)>B(1:3)) приведена на рисунке 6.3.

Оцените максимальную задержку сигнала  по отношению к моменту поступления операндов

по отношению к моменту поступления операндов  и

и  . Если необходимо увеличить быстродействие схемы, то по аналогии со способами ускорения сложения n-разрядная схема делится на группы по k разрядов и организуются обходные цепи передачи сигналов.

. Если необходимо увеличить быстродействие схемы, то по аналогии со способами ускорения сложения n-разрядная схема делится на группы по k разрядов и организуются обходные цепи передачи сигналов.

|

Рисунок 6.3 – Схема сравнения S=(A(1:3)>B(1:3))

6.3. Содержание работы

В процессе работы необходимо синтезировать схемы сравнения на равенство и на больше (меньше) трехразрядных двоичных кодов и промоделировать их работу на макете L-T. Затем, используя схему сравнения на равенство и схему трехразрядного накапливающего счетчика, построить двоичный счетчик с настраиваемым модулем счета (рисунок 6.4).

|

Рисунок 6.4 – Трехразрядный двоичный счетчик с

настраиваемым модулем счета

В данной схеме значение модуля счета набирается на кнопочном регистре В. В каждом такте счетчик А выполняет микрооперацию счета, увеличивая свое состояние на 1. В момент равенства кодов А и В сигнал R=1 сбрасывает счетчик в нулевое состояние.

6.4. Внеаудиторная подготовка

6.4.1. Изучить принципы построения схем сравнения: [2], стр. 157-167; [6], стр. 142-150.

6.4.2. Разработать схему трехразрядного компаратора, формирующего осведомительный сигнал x1=(A(3:1)>B(3:1)) или x2=(A(3:1)<B(3:1)).

6.4.3. Разработать схему трехразрядного компаратора, формирующего осведомительный сигнал x3=(A(3:1)=B(3:1)).

6.4.4. На основе схемы сравнения на равенство и схемы накапливающего счетчика по модулю 8, синтезировать трехразрядный счетчик, модуль счета которого задается кнопочным регистром. Сигнал x3 использовать для формирования сброса счетчика.

6.5. Выполнение работы в лаборатории

6.5.1. Собрать и наладить схему сравнения кодов на больше или меньше (задается преподавателем). Подать на ее входы числа A и B с кнопочных регистров и, изменяя их значения, убедиться в том, что сигналы сравнения x1 (x2) вырабатываются правильно.

6.5.2. Собрать и отладить схему сравнения кодов на равенство. Изменяя значения А и В убедиться, что сигнал x3 принимает значение 1 только при А=В.

6.5.3. Исследовать схему в динамическом режиме. С этой целью одно из чисел (например, A) подать с выхода счетчика. При фиксированном значении кнопочного регистра B и изменяемом по синхросигналам состояниям счетчика снять с помощью осциллографа временную диаграмму.

6.5.4. Собрать схему счетчика, считающего по модулю, задаваемому кнопочным регистром. Убедиться в правильности работы. Снять временную диаграмму и сравнить ее с построенной заранее.

6.6. Варианты заданий

Предполагается, что каждый студент синтезирует, проектирует и тестирует три операционных элемента: а) схема сравнения на больше, б) схема сравнения на равно, в) трехразрядный счетчик с настраиваемым модулем счета.

6.7. Контрольные вопросы

6.7.1. Где в компьютере могут использоваться схемы сравнения кодов? Приведите примеры.

6.7.2. Оцените быстродействие схем сравнения. Какие вы видите пути увеличения быстродействия?

6.7.3. Какие вы знаете микросхемы компараторов? Как их использовать в схемах?

6.7.4. Как можно вычислить значение осведомительных сигналов A=B, A>B, не используя схемы сравнения?

7. ЛАБОРАТОРНАЯ РАБОТА № 6. ДЕШИФРАТОРЫ (ШИФРАТОРЫ), МУЛЬТИПЛЕКСОРЫ (ДЕМУЛЬТИПЛЕКСОРЫ) И ИХ ИСПОЛЬЗОВАНИЕ ПРИ ПРОЕКТИРОВАНИИ ЦИФРОВЫХ УСТРОЙСТВ РАЗЛИЧНОГО НАЗНАЧЕНИЯ

7.1. Цель работы.

Изучить методы проектирования и схемные реализации двоичных шифраторов, дешифраторов, мультиплексоров и демультиплексоров, получить навыки синтеза, наладки, исследования и применения схем подобного класса.

7.2. Краткие теоретические сведения

Перечисленные в названии лабораторной работы операционные элементы комбинационного типа предназначены для преобразования многоразрядного входного кода в выходной код, построенный по иному, чем первый правилу. Закон функционирования таких схем обычно задается таблицей входов и выходов.

Дешифратор осуществляет преобразование n-разрядного двоичного позиционного кода в  -разрядный унарный код. Из всех

-разрядный унарный код. Из всех  выходов дешифратора только на одном, а именно на том, номер которого равен поданному на вход двоичному коду, будет логическая единица.

выходов дешифратора только на одном, а именно на том, номер которого равен поданному на вход двоичному коду, будет логическая единица.

Шифратор выполняет функцию, обратную дешифратору, т.е. преобразует унарный двоичный код в позиционный, значение которого определяет номер единичной компоненты входного набора.

Синтез схем шифраторов и дешифраторов сводится к построению для каждого разряда выходного слова булевой функции, определяющей связь данного разряда с входными наборами двоичных переменных.

В таблицах 7.1, 7.2 представлены, соответственно правила преобразования для кодов: «код 2,1» и «код 1 из 4».

Таблица 7.1. Таблица 7.2

| Входной код «2,1» | Выходной код «1 из 4» | ||||

| х1 | х0 | y3 | y2 | y1 | y0 |

| Выходной код «1 из 4» | Входной код «2,1» | ||||

| х3 | х2 | х1 | х0 | y1 | y0 |

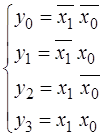

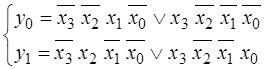

Таблица 7.1 задает работу дешифратора, а таблица 7.2 – шифратора. Соответствующие системы булевых функций представлены ниже:

;

;

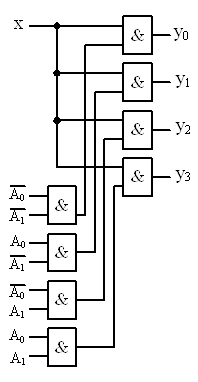

В цифровых устройствах часто решается задача передачи информации от m различных источников к n приемникам через общую шину (канал общего использования). Для решения такой задачи на входе шины устанавливается операционный элемент, называемый мультиплексором, который в зависимости от кода (адреса Am) подключает ко входу шины один из источников информации. При этом, установленный на выходе шины операционный элемент, называемый демультиплексором, обеспечивает передачу информации приемнику, определяемому кодом (адресом An).

Логика функционирования мультиплексора для m=4 представлена таблицей 7.3, где  - выходы независимых источников информации. Таблица 7.4 определяет логику функционирования демультиплексора в случае n=4, где

- выходы независимых источников информации. Таблица 7.4 определяет логику функционирования демультиплексора в случае n=4, где  - входы приемников информации.

- входы приемников информации.

Таблица 7.3 Таблица 7.4

| Входы | Адрес | Выход | |

| A1 | A0 | y | |

|

| ||

| |||

| |||

|

| Вход | Адрес | Выход | ||||

| A1 | A0 |

|

|

|

| |

|

| |||||

| ||||||

| ||||||

|

Мультиплексор и демультиплексор содержат дешифратор адреса. Дешифратор управляет логическими вентилями, разрешающими передачу информации (при конкретном адресе) только через один из вентилей.

На рисунках 7.1 и 7.2 изображены схемы мультиплексора и демультиплексора соответственно. Поведение операционных элементов специфицировано таблицами 7.3 и 7.4.

Как уже говорилось выше, мультиплексоры, дешифраторы, демультиплексоры могут применяться для синтеза операционных элементов, например, шин для передачи данных.

Рисунок 7.1 – Мультиплексор Рисунок 7.2 – Демультиплексор

Шина – операционный элемент (ОЭ), служащий для выполнения микрооперации передачи информации, например, между регистрами:

y1: B(1:n):= A(1:n),

y2: B(1:n):= ù A(1:n) (инверсная передача).

Регистр А называют источником информации, а регистр B – приемником.

Регистр А называют источником информации, а регистр B – приемником.

Шины состоят из цепей.

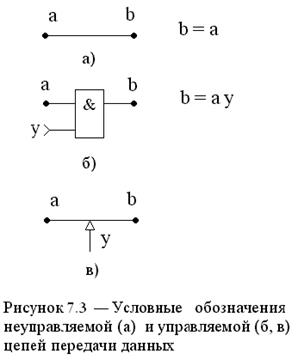

Цепь – ОЭ, служащий для передачи одного бита информации. В простейшем случае цепь – это проводник. Информация на его концах совпадает ( , рисунок 7.3, а). На рисунке 7.3,б показана управляемая цепь. Информация передается по цепи только при наличии управляющего сигнала у (

, рисунок 7.3, а). На рисунке 7.3,б показана управляемая цепь. Информация передается по цепи только при наличии управляющего сигнала у ( ). Условное изображение управляемой шины на структурных схемах ОУ приведено на рисунке 7.3, в.

). Условное изображение управляемой шины на структурных схемах ОУ приведено на рисунке 7.3, в.

Виды цепей:

- однофазные,

- парафазные.

Однофазные цепи (управляемые или неуправляемые) передают только прямое или только инверсное значение сигнала. Парафазные цепи передают оба значения сигнала (рисунок 7.4).

Сложность парафазной шины увеличивается в два раза по сравнению с однофазной, что позволяет достичь выигрыша по быстродействию, если приемниками информации являются RS-триггеры (JK-триггеры). В данном случае парафазная шина позволяет передать информацию за один такт.

Сложность парафазной шины увеличивается в два раза по сравнению с однофазной, что позволяет достичь выигрыша по быстродействию, если приемниками информации являются RS-триггеры (JK-триггеры). В данном случае парафазная шина позволяет передать информацию за один такт.

Для однофазной шины используется два такта.

1) В первом такте приемный регистр обнуляется (на R-входы всех триггеров регистра подаются единицы Ri:=1).

2) Во втором такте устанавливаются только единицы в нужных разрядах регистра (Si:= a).

Проектирование однотактных и двухтактных (парафазных и однофазных) цепей приема и установки кода рассматривалось выше в примере 1 (синтез регистра на раздельных триггерах).

Прием информации на D-триггер с помощью однофазной цепи осуществляется за один такт.

N-разрядная шина состоит из N одноразрядных цепей.

Шины могут быть раздельными и общими. При реализации передач в системе регистров раздельными шинами каждая передача осуществляется по собственной шине, связывающей соответствующий источник с соответствующим приемником, при подаче в схему соответствующего управляющего сигнала уi. Общая шина (магистраль) – это схемное решение, в котором все возможные передачи между регистрами осуществляются по единственной шине.

Date: 2015-09-05; view: 1729; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |