Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Разработка поведенческой VHDL-модели микросхемы

Поведенческая модель описывает отображение входов проекта в выходы, не раскрывая структуру проекта. Благодаря этому свойству поведенческая модель является основным средством формального описания проекта в следующих случаях:

● в начале процесса проектирования, когда составляется абстрактная спецификация на проект и отсутствуют детали его реализации;

● при наличии в проекте частей, представляющих интеллектуальную собственность.

Разработаем поведенческую VHDL-модель микросхемы КР1533ИР8, условно-графическое изображение которой приведено на рис.1. Микросхема представляет собой два JK -триггера, срабатывающих по отрицательному фронту тактового сигнала и имеющих входы сброса. На рис.1.1 показано расположение всех 14 выводов микросхемы, а назначение каждого из выводов описано в табл.1.1. Информация о выводах служит исходными данными для построения VHDL-модуля entity (рис.1.3), описывающего интерфейс данной микросхемы.

Рис.1.2. Расположение выводов

| entity KP1533ИР8 is port(R: in Bit; C: in Bit; A: in Bit; B: in Bit; Q1: inout Bit; Q2: inout Bit; Q3: inout Bit; Q4: inout Bit; Q5: inout Bit; Q6: inout Bit; Q7: inout Bit; Q8: inout Bit; end KP1533TB11; |

Рис.1.3. VHDL-модуль entity для микросхемы KP1533ИР8

Интерфейс содержит четыре порта R, C, A, B с режимом in и восемь портов Q1, Q2,Q3,Q4,Q5,Q6,Q7,Q8 с режимом out. Все порты имеют тип Bit. Заметим, что число портов на два меньше числа выводов микросхемы. Порты соответствуют информационным выводам, исключая питание и общий. Для построения модуля использованы зарезервированные слова entity, is, port, in, out, inout, end и разделители ‘(’, ‘:’, ‘;’, ‘:=’, ‘’’, ‘)’.

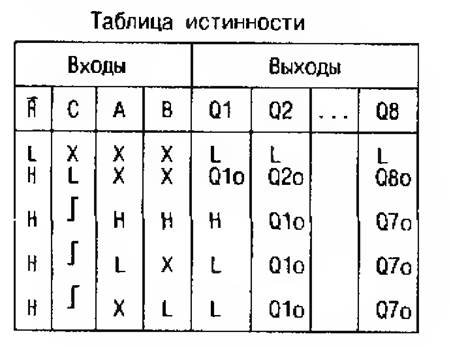

VHDL-модуль architecture поведенческого уровня строится по табл.1.2, описывающей функционирование триггеров в зависимости от уровней сигналов на их входах.

Таблица 1.2

В табл.1.2 0 – низкий уровень сигнала (логический 0), 1 – высокий уровень сигнала (логическая 1), X – безразличное значение, 1/0 - отрицательный фронт сигнала, Q0 – предыдущее значение. Низкий уровень напряжения U0 на входe R устананавливает выходы регистра в нулевое состояние вне зависимости от состояния других входов (С, A и B). При наличии на входe R напряжения высокого уровня U1 то данные, поданные на на входы А и В передвигаются на одну позицию вправо с приходом каждого положительного перепада на тактовый вход С. Причем, запись высокого логического уровня на выход Q1 происходит только при высоком логическом уровне на обоих входах А и В.

VHDL-модуль architecture приведен на рис.1.4. Модуль начинается с зарезервированного слова architecture, за которым следуют имя модуля Behavior, зарезервированное слово of, имя KP1533ИР8 модуля entity. После зарезервированного слова process следует список (R,C,A,B) сигналов, события на которых запускают процесс, вызывая выполнение входящих в него операторов с первого по последний. Вычисление выполняется с помощью условных операторов if, операторов присваивания :=, операции проверки на равенство ‘=’ и логических операций and и not. Положительный фронт на сигнале C моделируется выражением C'Event and C='1', в котором C'Event - атрибут, идентифицирующий событие на сигнале C. Назначение новых состояний выходным портам выполняется с помощью условных операторов if, операторов назначения сигнала <=, операций проверки на равенство ‘=’ и на неравенство ‘/=’ лишь в случае отличия новых состояний от предыдущих. В левой части оператора назначения сигнала указывается имя сигнала. Правая часть включает выражение, определяющее значение сигнала, и после зарезервированного слова after включает выражение, определяющее время (1ps), после которого сигнал получает это значение.

| architecture Behavior of KP1533ИР8 is begin T: process(R,С,A,B) variable (Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8); begin if R='0' then (Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8)_Temp:='0’; elsif R='1' and C'Event and C1='1' then ifA='1' and B='1' then Q8<='Q7' after 1ps; Q7<='Q6' after 1ps; Q6<='Q5' after 1ps; Q5<='Q4' after 1ps; Q4<='Q3' after 1ps; Q3<='Q2' after 1ps; Q2<='Q1' after 1ps; Q1<='1' after 1ps; elsif A='0' or B='0' or (A='1' and B='1') then Q8<='Q7' after 1ps; Q7<='Q6' after 1ps; Q6<='Q5' after 1ps; Q5<='Q4' after 1ps; Q4<='Q3' after 1ps; Q3<='Q2' after 1ps; Q2<='Q1' after 1ps; Q1<='0' after 1ps; end if; end if; end process T; |

Рис.1.4. VHDL-модуль architecture

Среда тестирования (Test_Bench) создается как отдельный объект проекта на языке VHDL (рис.1.5). Все сигналы, воздействующие на тестируемый модуль, представленный VHDL-модулями KP1533ИР8 и Behavior, генерируются внутри среды, поэтому VHDL-модуль entity среды с именем KP1533ИР8_T не включает параметров настройки и портов. Архитектура среды тестирования (VHDL-модуль architecture с именем TB_Architecture) построена на смешанном структурно-потоковом уровне. Тестируемый модуль объявлен как компонент (component) с именем KP1533ИР8 и двенадцатью формальными портами. Объявление компонента используется для определения одной его копии с именем UUT посредством параллельного оператора конкретизации компонента, входящего в исполнительную часть модуля architecture среды тестирования. Оператор конкретизации включает отображение формальных портов (port map) компонента на фактические одноименные сигналы R, C, A, B, Q1…Q8, объявленные в разделе объявлений архитектуры TB_Architecture. Все порты и сигналы имеют тип Bit. Входные сигналы, для которых порты имеют режим in, inout, являются внешними стимулами для тестируемого модуля и генерируются вне его. Они генерируются, за исключением сигналов C в модуле T_Architecture посредством параллельных операторов назначения сигнала. Правая часть оператора содержит последовательность разделенных запятой транзакций, описывающих будущую временную диаграмму для сигнала, имя которого составляет левую часть оператора. Каждая транзакция представляется парой выражений. Первое выражение определяет значение сигнала. Второе выражение, стоящее после зарезервированного слова after, определяет время, через которое, начиная с текущего момента веремени, сигнал получит значение. Второй элемент пары может опускаться, время в этом случае принимается равным нулю. Например, в результате выполнения оператора R<='1', '0' after 400ns, '0' after 400ns; сигнал R сначала получит значение '1', через 400ns получит значение '0', а через 400ns от текущего момента времени снова получит значение '1'. Таким образом, операторы назначения сигнала устанавливают последовательность событий на каждом сигнале. Для генерации тактирующих сигналов C используется специальное средство среды Active-VHDL. Это средство позволяет определить временные диаграммы сигналов. Сигналы периодически изменяют значение с ‘0’ на ‘1’ и с ‘1’ на ‘0’, причем время цикла составляет 50n s, что обеспечивает частоту 20MHz. На протяжении 50% времени значение сигнала равно ‘0’ и на протяжении 50% времени значение равно ‘1’. VHDL-модуль configuration связывает копию UUT компонента KP1533ИР8 с объектом проекта, представленным интерфейсом KP1533ИР8 и архитектурным телом Behavior.

События на входных сигналах определяют порядок перезапуска процессов, моделирующих работу регистра. Процессы, в свою очередь, вычисляют временные диаграммы для сигналов Q1..Q8.

| entity KP1533ИР8_T is end KP1533TBИР8_T; architecture TB_Architecture of КР1533ИР8_t is -- Component declaration of the tested unit component KP1533ИР8 port(R: in Bit; C: in Bit; A: in Bit; B: in Bit; Q1: out Bit; Q2: out Bit; Q3: out Bit; Q4:out Bit; Q5: outBit; Q6: out Bit; Q7: out Bit; Q8: out Bit;) end component; --Stimulus signals - signals mapped to the --input and inout ports of tested entity signalR: Bit; signalC: Bit; signal A: Bit; signal B: Bit; signal Q1: Bit; signal Q2: Bit; signal Q3: Bit; signalQ4: Bit; signal Q5: Bit; signalQ6: Bit; signalQ7: Bit; signalQ8: Bit; | begin --Unit Under Test port map UUT: KP1533ИР8 port map(R => R, C => C, A => A, B => B, Q1 => Q1, Q2 => Q2, Q3 =>Q3, Q4 => Q4, Q5 => Q5, Q6 => Q6, Q7 => Q7, Q8 => nQ2); R<='1', '0' after 400ns, '0' after 400ns; A<='1', '0' after 30ns, '1' after 30ns, '0' after30ns; B<='1', '0' after 60ns; C<='0', '1' after25ns, '0' after 25ns; end TB_Architecture; configuration Testbench_for_KP1533ИР8 of KP1533ИР8_T is for TB_Architecture for UUT: KP1533ИР8 use entitywork.KP1533ИР8 (Behavior); end for; end for; end Testbench_for_KP1533ИР8; |

Рис.1.5. Среда тестирования поведенческой модели

Date: 2016-07-25; view: 1097; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |