Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

Микросхемы серии К176

Все микросхемы серии независимо от назначения и сложности характеризуются электрическими параметрами, которые имеют следующие значения [4,5]:

Напряжение источника питания, В..... 9±5%

Выходное напряжение логического О, В.... <0,3

Выходное напряжение логической 1, В.... >8,2

Статическая помехоустойчивость, В..... 0,9

Входной ток логического 0, мкА...... — 0,1

Входной ток логической 1, мкА...... <0,1

Коэффициент разветвления по выходу (статический) 100

Максимальный выходной ток в состояниях 0 и 1, мА 1

Наименьшее сопротивление нагрузки, яри которой сохраняется уровень логической 1 на выходе, кОм 150

Диапазон допустимых значений входного напряжения, iB............. — 0,2-+ Uи.п

Среднее время задержки распространения сигнала через логический элемент, нc...... 250

Наибольшая частота переключения триггера, МГц. 1

Потребляемая мощность одним логическим элементом в статическом режиме, мкВт..... <0,25

Конструктивно микросхемы оформлены в пластмассовые корпуса с 14 или 16 выводами.

Логические микросхемы выполняют операции И, НЕ, И-НЕ, ИЛИ-НЕ. Каждая микросхема состоит из нескольких логических элементов, которые объединены по цепям питания, но функционально автономны, т. е. могут использоваться независимо один от другого. Элемент, выполняющий логическую операцию НЕ, т. е. инвертор, представляет собой ключ (см. рис. 4). При входном сигнале 1 на его выходе устанавливается уровень 0, а при входном сигнале 0 выходной сигнал имеет уровень 1.

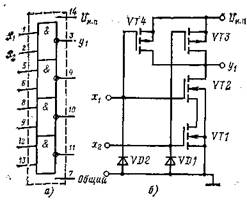

Примером микросхемы с логическими элементами И-НЕ может служить К176ЛА7, содержащая четыре таких элемента с двумя входами каждый (рис. 5,а). Принципиальная схема логического элемента И-НЕ (рис. 5,6) состоит из двух КМДП-ключей, нижние транзисторы VT1, VT2 которых соединены последовательно, а верхние VT3, VT4 параллельно. Диоды VD1, VD2 предохраняют входы от воздействия больших отрицательных напряжений. Если хотя бы на одном из входов Х1 или х2 присутствует сигнал с уровнем 0, то один из нижних транзисторов закрыт, а один из верхних открыт. Поэтому на выходе элемента независимо от значения сигнала на другом входе устанавливается напряжение высокого уровня, т. е. сигнал 1. Только при наличии 1 на обоих входах, когда нижние транзисторы открыты, а верхние закрыты, на выходе устанавливается сигнал 0. Таким образом, логический элемент реализует функцию И-НЕ: y — XiXi.

Рис. 5. Микросхема К176ЛА7:

а — принципиальная схема; б — логический элемент И-НЕ

Рис. 6. Микросхема К176ЛЕ5:

а — принципиальная схема; б — логический элемент ИЛИ-НЕ

Примером микросхемы, содержащей логические элементы ИЛИ-НЕ, может служить К176ЛЕ5 (рис. 6,а). Она содержит четыре таких элемента с двумя входами каждый. Принципиальная схема логического элемента ИЛИ-НЕ (рис. 6,6) состоит из двух КМПД-ключей, нижние транзисторы которых соединены параллельно, а верхние последовательно. При поступлении „ сигнала 1 хотя бы на один из входов, например Xi, нижний транзистор VT1 откроется, а верхний VT3 закроется и независимо от сигнала на втором входе на выходе элемента установится уровень логического 0. Только при сигнале 0 на обоих входах, когда нижние транзисторы закрыты, а верхние открыты, на выходе установится уровень 1. Таким образом, логический элемент реализует функцию ИЛИ-НЕ: y=Xi+x2.

Сопоставлением режимов работы рассмотренных логических элементов нетрудно убедиться в том, что для их блокирования необходимо на один из входов подать сигнал 0 для элемента И-НЕ и сигнал 1 для элемента ИЛИ-НЕ. В этом случае элементы устанавливаются в состояния соответственно 1 и 0 независимо от значения сигналов на других входах. Потребляемая логическими микросхемами мощность в статическом режиме составляет 1 — 2 мкВт.

В составе серии есть также логические микросхемы, содержащие элементы с тремя, четырьмя и девятью входами, универсальный элемент, который можно использовать, в частности, как усилитель мощности с током нагрузки до 2 мА.

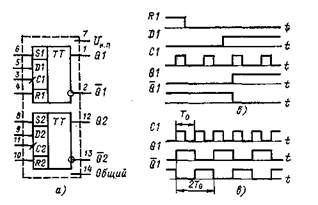

Рис. 7. Микросхема КП6ТМ2:

а — принципиальная схема, б — временные диаграммы D-триггера, в — временные диаграммы T-триггера

Триггеры являются основными элементами регистров и счетчиков. Серия содержит JK-триггер К176ТВ1 и D-триггеры в двух вариантах исполнения: с одним установочным входом R (установка 0) КД76ТМ1 и с двумя установочными входами S (установка 1) и R (установка 0) К176ТМ2. Каждая из указанных микросхем содержит по два одинаковых триггера, связанных по цепям питания, но функционально самостоятельных.

Все триггеры построены по двухступенчатой структурной схеме и поэтому могут быть преобразованы в триггер со счетным входом (T-триггер) [6]. Для построения регистра или счетчика-делителя можно использовать любой из триггеров. Однако в ряде случаев, в частности при реализации регистров и счетчиков с последовательным переносом, отдается предпочтение D-трштерам, требующим меньшего числа соединений в схемах. Из двух микросхем с ГЛтриггера-ми более универсальной в отношении установки начального состояния является микросхема К176ТМ2, содержащая два D-триггера с входами установки 0 и 1 (рис. 7,а). Рассмотрим основные режимы работы этого триггера.

Триггер имеет информационный вход D, вход С для тактовых сигналов, входы S, R для установки триггера соответственно в единичное и нулевое начальные состояния и два выхода — прямой Q и инверсный Q. Состояние триггера определяется по уровню напряжения на прямом выходе Q. Высокому уровню напряжения соответствует единичное состояние триггера, обычно обозначаемое как Q = l. Низкому уровню напряжения на выходе Q соответствует нулево» состояние триггера Q=0. Сигнал на инверсном выходе имеет значение, обратное значению сигнала на прямом выходе.

Для установки триггера в начальное единичное состояние необходимо на вход S подать сигнал 1 и затем после установки снять его. Аналогично для установки триггера в нулевое начальное состояние сигнал 1 подается на вход R. При работе триггера на установочных входах должен быть обеспечен нулевой потенциал. Сигнал установки должен быть снят в момент изменения тактового сигнала с высокого уровня на низкий (рис. 7,6). Он может быть снят и при нулевом уровне сигнала на входе С, но в таком случае необходимо обеспечить задержку длительностью не менее 1 мкс момента поступления на входе С сигнала 1. Эта задержка необходима для записи в триггер информации со входа D. Информация записывается вначале в первую ступень триггера, затем с приходом сигнала 1 на вход С она переписывается во вторую ступень и появляется на выходах триггера.

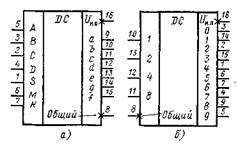

Рис. 8. Микросхемы дешифраторов: a-К176ИД2, б-К176ИД1

Для наглядного представления о том, что информация на выходе триггера появляется после изменения тактового сигнала с 0 на 1, вход С обозначается как прямой динамический символ треугольника, направленного вершиной вовнутрь [Такое обозначение входа С триггеров серии К176 удобно и широко распространено, но не соответствует характеру процессов, происходящих в триггерах двухступенчатой структуры [6]. Вход С у таких триггеров статический, а не динамический.]. Если аналогичное воздействие на триггер оказывается при изменении сигнала на входе С с) на 0, то этот вход обозначается как инверсный динамический (вершиной наружу).

Для применения D-триггера в счетчиках с последовательным переносом необходимо предварительно преобразовать его в Г-триггер, соединив инверсный выход со входом D. Вход С становится счетным: при подаче на него импульсов с периодом повторения Tо на выходе триггера формируется последовательность импульсов, которые имеют длительность Tо и период повторения 2Г0. Таким образом, триггер делит частоту следования входных сигналов на два или, иначе, считает входные импульсы по модулю 2 (рис. 7. в).

Дешифраторы в серии К.176 выпускают в нескольких вариантах, каждый из которых имеет свою область применения. Микросхема К176ИД2 (рис. 8,а) выполняет функции дешифратора четырехэлементного кода с преобразованием его в семиэлементный код для управления семисегментным индикатором. Эта микросхема имеет четыре информационных входа и семь выходов и предназначена для совместного применения с двоично-десятичным счетчиком.

Входы S, М, К являются управляющими. При М=К=0 сигнал на входе S определяет либо рабочий режим преобразования (S = l) либо режим хранения выходного кода (S = 0). При М=Л независимо от значения сигналов на входах S, К выходной код инвертируется. При М=0, К=1 обеспечивается гашение индикатора.

Функциональным аналогом микросхемы К176ИД2 является микросхема К176ИДЗ. Отличие этого дешифратора от рассмотренного состоит в том, что он имеет высоковольтный выход и способен выдерживать напряжение до 27 В. Такой дешифратор применяется, в частности, для управления многоразрядным катодолюминисцентным индикатором в устройствах с динамической индикацией (см. рис. 2), например в настольных электронных часах «Электроника 2-06» (см. § 11).

Дешифратор К176ИД1 (рис. 8,6) относится к другому типу дешифраторов. Он имеет четыре входа и десять выходов и предназначен для дешифрования двоично-десятичного кода: каждой из десяти комбинаций входных сигналов соответствует сигнал 1 на одном из выходов. Такие дешифраторы применяют для управления многокатодными газоразрядными индикаторами, а также в блоке программирования сигнального устройства (см. рис. 3).

Регистры по назначению классифицируются на два вида: регистры хранения и регистры сдвига. На основе регистров сдвига с перекрестной ОС построены многие счетчики, входящие в серию К176, в частности К176ИЕЗ, К176ИЕ4, К176ИЕ8, К176ИЕ17 и др. В составе серии К176 регистры сдвига представлены рядом микросхем: К176ИР2 содержит два функционально автономных четырехразрядных регистра, К176ИРЗ — один четырехразрядный регистр, К176ИР10 — 18-разрядный регистр и др.

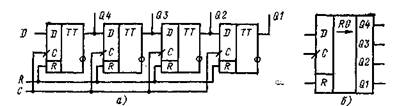

Каждый из регистров микросхемы К176ИР2, построенный по схеме рис. 9,а, имеет информационный вход D, тактовый вход С, вход установки R и четыре выхода по одному от каждого разряда. Информация в такой регистр записывается последовательно во времени через вход D так, что с каждым очередным тактовым импульсом записываемая комбинация продвигается поэлементно от старшего разряда к младшему (прямой сдвиг, иначе называемый сдвиг вправо) до заполнения всех разрядов регистра. Направление сдвига указывается стрелкой на условном обозначении регистра (рис. 9,6). Регистр может быть построен так, что его заполнение производится со входа младшего разряда (сдвиг влево или обратный сдвиг). Регистры, которые допускают сдвиг в обоих направлениях, называются реверсивными. К реверсивным относится регистр К176ИРЗ.

Счетчики-делители, входящие в серию КГ76, построены либо на основе регистра сдвига с перекрестной ОС (К176ИЕЗ, К176ИЕ4, К176ИЕ8 и др.), либо ло схеме с последовательным переносом (К176ИЕ5, К176ИЕ12, К176ИЕ18).

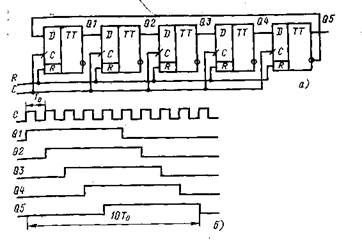

Счетчик на регистре сдвига с перекрестной ОС с инверсного выхода последнего триггера на вход D первого триггера (рис. 10,а) имеет коэффициент счета 2n, где n — число триггеров в схеме регистра. Следовательно, для получения делителя на 10 необходим пятиразрядный регистр сдвига (рис. 10,а), а делителя на 6 — трехразрядный регистр.

Временные диаграммы (рис. 10,6) иллюстрируют особенности работы счетчика: вначале он заполняется 1, затем, освобождаясь от них, заполняется 0. Эта особенность обусловлена характером процессов, происходящих в регистре сдвига: с каждым тактовым импульсом сигнал переходит от одного триггера к другому, продвигаясь, таким образом, от входа схемы к ее выходу. Из диаграммы нетрудно видеть, что получаемые на любом из выходов колебания характеризуются одинаковым периодом повторения 2я Го, где Го — период повторения входных сигналов, взаимно сдвинутых во времени. Сдвиг соседних последовательностей равен одному периоду То входных сигналов.

Рис. 9. Регистр сдвига:

а — Функциональная схема, б — условное обозначение

Рис. 10. Счетчик на регистре с перекрестными связями:

а — функциональная схема, б — временные диаграммы

Реализация схемы счетчика возможна на всех рассмотренных ранее триггерax. При использовании D-триггеров (К176ТМ1, К176ТМ2) схема их соединения должна соответствовать рис. 10,а. В случае применения JК-триггеров (К176ТВ!) входы I, К каждого последующего разряда следует соединить соответственно с прямым и инверсным выходами предыдущего разряда, а ОС обеспечить соединением прямого и инверсного выходов последнего разряда соответственно со входами К и J первого разряда. Входы С, R объединяются так же, как на рис. 10,а.

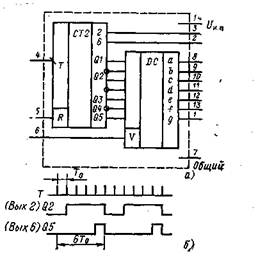

По рассмотренному принципу, как уже отмечалось, построены многие микросхемы счетчиков-делителей серии К176. Микросхема К176ИЕ4 (рис. 11,а) состоит из двух выполненных в одном кристалле функциональныех узлов: пятиразрядного счетчика и дешифратора его состояний с преобразованием выходного кода счетчика в семиэлементный код для управления сегментами индикатора. Выходы дешифратора для удобства обозначают теми же символами, что и сегменты индикатора (рис. 11,6). Формируемые на этих выходах сигналы будем называть сегментными. Для возбуждения сегмента соответствующий ему сегментный сигнал должен иметь уровень 1.

Рис. 11. Микросхема К176ИЕ4:

а — принципиальная схема, б — соответствие обозначений выходов микросхемы и сегментов индикаторов

Рис. 12. Микросхема К176ИЕЗ:

а — принципиальная схема, б — временные диаграммы сигналов на выходах 2 (вывод 3) и 6 (вывод 2)

При необходимости с помощью управляющего сигнала на входе V (вывод 6) можно инвертировать сегментные сигналы. Для этого на вход V следует подать напряжение с уровнем логической 1. В обычном режиме работы микросхемы напряжение на этом входе равно 0. Для обеспечения управления ЖКИ, требующим переменного напряжения, на вход V подается последовательность импульсов с частотой 64 Гц (см. § 8).

Микросхема К176ИЕ4 имеет еще два выхода, которые обозначены цифрами 4 и 10. Выход 4 (вывод 3) — выход четвертого разряда счетчика, который на схеме рис. 10,а обозначен Q4, а выход 10 (вывод 2) — это выход Q5 последнего разряда счетчика. Изменения напряжений на этих выходах в процессе работы микросхемы приведены на рис. 10,6. Как видно, это одинаковые по форме и временным характеристикам сигналы, один из которых Q4 изменяет свой уровень с 0 на 1 после четвертого входного сигнала (именно на это указывает цифра 4 на условном обозначении выхода), а другой Q5 — после пятого, так что взаимный сдвиг этих сигналов равен одному периоду повторения входных импульсов. Выход 10 используется для получения сигналов с частотой следования в 10 раз меньшей, чем частота входных импульсов.

Для установки нулевого состояния счетчика необходимо на вход R подать напряжение высокого уровня, которое затем должно быть снято и при работе счетчика иметь уровень 0.

Микросхема К176ИЕЗ (рис. 12,а) по структурной схеме аналогична К176ИЕ4. Отличие состоит в том, что пятиразрядный счетчик (см. рис. 10,а) в процессе работы принимает шесть состояний из десяти возможных. Такой режим счетчика обеспечен внутренними связями, исключающими четыре «лишних» состояния: после шестого входного импульса все триггеры в схеме счетчика сбрасываются в нулевое состояние. В результате на выходе 6 (вывод 2), который является выходом последнего триггера Q5, формируется импульсная последовательность с частотой повторения в шесть раз меньшей, чем частота входных сигналов (рис. 12,6). На выходе 2 (вывод 3), который является выходом второго триггера Q2, получается последовательность импульсов с такой же, как на выходе 6, частотой повторения, но отличающихся по форме: напряжение на этом выходе изменяет свой уровень с 0 на 1 после второго импульса в каждой серии из шести импульсов на входе.

Сигналы с выходов 4 и 2 в микросхемах соответственно К176ИЕ4 и КД76ИЕЗ используются как сигналы ОС, устанавливающие счетчики единиц и десятков часов в нулевое состояние по достижению ими состояний, соответствующих 24 ч.

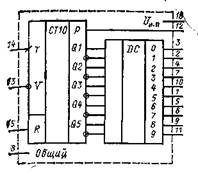

Микросхема К176ИЕ8 (рис. 13) состоит из пятиразрядного счетчика на основе рассмотренной схемы регистра (см. рис. 10,а) и дешифратора его состояний с десятичным выходным кодом: каждому из десяти состояний счетчика соответствует сигнал 1 на одном из выходов, обозначенных десятичными цифрами от 0 до 9. Кроме выходов дешифратора у микросхем есть выход переноса Р (вывод 12), на котором выделяются импульсы, частота повторения которых в 10 раз меньше частоты входной последовательности сигналов.

Микросхема имеет три входа: для счетных импульсов — вход Т (вывод 14), для установки счетчика в нулевое состояние — вход R (вывод 15), для сигнала разрешения — инверсный вход V (вывод 13). Сигнал на входе V, имеющий единичный уровень, переводит счетчик в режим хранения. Разрешающим является сигнал с уровнем 0.

Таким образом, рассмотренная микросхема может быть использована в качестве делителя на 10 с возможностью управления многокатодным газоразрядным индикатором, а также в качестве десятиканального распределителя импульсов. Широкое применение микросхем К176ИЕ8 находит в часах для реализации блока программирования сигнального устройства (см. § 7). В таком качестве она использована в настольных электронных часах «Электроника 2-05» (см. § 11).

Рис. 13. Микросхема К176ИЕ8

Рис. 14. Счетчик с последовательным переносом:

а — функциональная схема, б — временные диаграммы

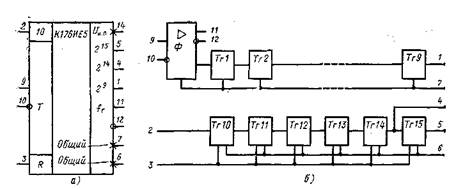

Счетчик с последовательным переносом строится на Г-триггерах соединением прямого или инверсного выхода предыдущего триггера со счетным входом; последующего. Для реализации такого счетчика могут быть использованы как D-триггеры (К176ТМ1, К176ТМ2), так и JK-триггеры (К176ТВ1). Схема четырехразрядного счетчика на D-триггерах и временные диаграммы, иллюстрирующие ее работу, приведены на рис. 14. Для реализации этой схемы требуются две микросхемы К176ТМ1 или К176ТМ2.

Коэффициент (модуль) счета равен 2п, где n — количество триггеров в схеме счетчика, т. е. его разрядность. Временные диаграммы показывают, что опрокидывание последующего триггера происходит всякий раз, когда состояние предыдущего триггера изменяется с 1 на 0. Сигналы, снимаемые с выходов Q1, Q2, Q3, Q4, имеют период повторения соответственно 2Т0, 4Г0, 8Г0, 16Г0, где То — период повторения входных сигналов.

Для дешифрования состояния счетчика используются все его выходные сигналы одновременно. В таком случае имеет значение, в каком режиме работает счетчик: суммирования или вычитания. В суммирующем счетчике (рис. 14) с приходом на вход Т очередного импульса результат счета в форме комбинации выходных сигналов Q4 (старший разряд), Q3, Q2, Q1 увеличивается на единицу. Например, после комбинации 0101, соответствующей десятичной цифре 5, следует комбинация 0110 (цифра 6).

Рис. 15. Микросхема К176ИЕ5:

Date: 2015-05-23; view: 11658; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |