Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

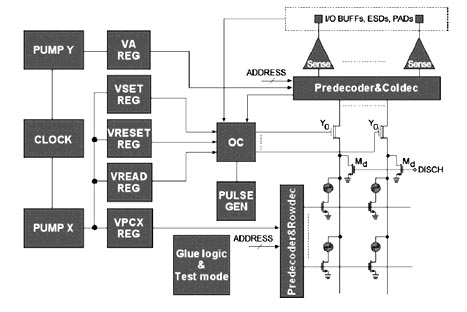

Организация PRAM

Приведеные схемы PRAM изготовленной по стандартной КМОП технологии. Ячейка занимала 1,55 мкм х 0,85 мкм, толщина под затворного диэлектрика МОП транзисторов составляла 15 нм, двухслойный затвор изготавливался на основе поли кремния и силицида титана. Соединения были двухслойными (Ti/Cu). Высокое сопротивление - логический 0, низкое сопротивление - 1. При считывании измерялось сопротивление адресуемой ячейки. При этом на ячейку подавалось определенное напряжение, и считывался ток, который сравнивался с некоторым управляемым эталонным током. Напряжение считывания 400 мВ, 1,5 В при записи 1 (операция “ Set ”) и 2 В при записи 0 (операция “ Reset ”). Матрица накопителя имела 2048 строк и 2048 столбцов. Контроль этих напряжений осуществлялся с помощью управляющего блока “ОС”, сигнал с которого поступал на затворы транзисторов запоминающих ячеек. Управляющие транзисторы имели пороговое напряжением 350 мВ, В импульсном режиме, напряжение шины необходимое в SET и RESET режимах получалось с помощью простой регулировки соответствующих напряжений на затворах транзисторов.

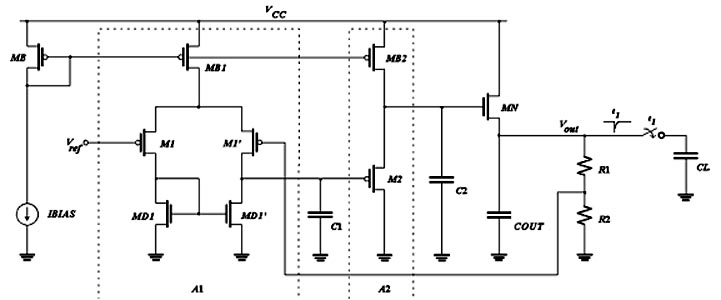

Транзисторы разряжают все шины после любых операций чтения или записи, таким образом, чтобы не допускать ложных программирующих напряжений на параллельных не выбранных ячейках во время последующих операций. Необходимые программирующие напряжения, выше чем стандартный источник (1.8 В). В связи с этим, были встроены два генератор подкачки заряда (charge pumps) показанные на нижнем рис. справа. Генератор подкачки заряда (через регуляторы) обеспечивает питающие напряжения для SET, RESET, чтения и дешифратора строчной шины. Другой генератор подкачки заряда предназначен обеспечивать программирующую мощность передоваемую через переключатель столбцов (в этом отношении, метод смещения выбранной каскадной шины позволяет регулятору соответствовать техническими требованиями релаксации и уменьшить потребляемую мощность). Для обоих генераторов подкачки заряда была использована схема утроителя напряжения. Было взято напряжение 3.3 В в качестве, смещения дешифратора столбцов во время операций чтения и программирования. Блок «ОС» обеспечивал необходимые уровни напряжений импульсов на затворах силовых транзисторов. Эти транзисторы не выполняли выборку уровня и, поэтому одно из таких устройств, связано с каждой шиной массива. Во время выполнения операции чтения или программирования, потенциалы затворов всех силовых транзисторов (которые предварительно были разряжены таким, образом чтобы окончательно изолировать ячейки памяти вовремя холостой команды) должны быть повышены до читающего или программирующего напряжений. Поэтому, большая нагрузочная ёмкость заряжалась с помощью соответствующих регуляторов напряжений. Для того, чтобы гарантировать быстрое восстановление выходного напряжения в начале любой операции чтения, для минимизации считывающего времени обращения, была использована схема для считывающего регулятора напряжений, представленная на рис.(второй сверху) 5.

Этот регулятор содержит входной дифференциальный каскад, схему сдвига уровня, и n канальный МОП выходной истоковый повторитель (смещённый при помощи резистивной цепи). Входной сигнал 0 В. Напряжение питания (5.2 В) обеспечивалось с помощью генератора подкачки заряда. Выбранная структура регулятора обеспечивала короткое время восстановления вместе с малым потреблением энергии. Действительно, падение выходного напряжения регулятора возникало в результате возрастания напряжения затвор-исток транзистора и, поэтому выходной ток, соответственно выходное напряжение быстро восстанавливалось. В дополнении, цепь обратной связи также повышает напряжение затвора выходного n-канального МОП транзистора, соответственно вносит добавочный выходной ток. Описанная схема регулятора напряжения не может обеспечивать нормальную работу внутренних узлов, когда требуется выходное напряжение больше чем 3 В. В связи с этим благоразумнее использовать, стандартные структуры регуляторов.

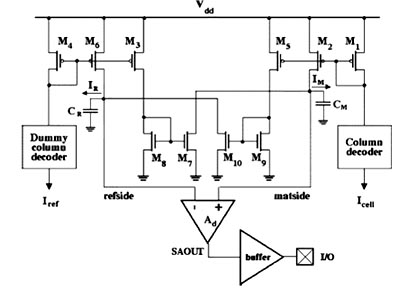

Схема усилителей считывания показана на рис. 6. Схемы усилителей были полностью симметричны, с аналогичной помеха защищённостью благодаря ёмкостной связи с экранирующей подложкой, источником питания и землёй, чтобы обеспечить нулевое смещение и не допускать систематического смешения (наводки). После перезаряда и стабилизации шины (соответствующий цепи не показанной на рисунке), определялось различие токов (разница между током выбранной ячейки и опорным током). Различая токов, были проинтегрированы на шунтирующие ёмкости на выводах matside и refside. Результирующие напряжения сравнивались с помощью блока, который производит фиксированный выходной цифровой сигнал SAOUT. Этот сигнал подавался на выходной буфер и на устройство ввода-вывода (I / O).

Date: 2015-05-22; view: 353; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |