Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

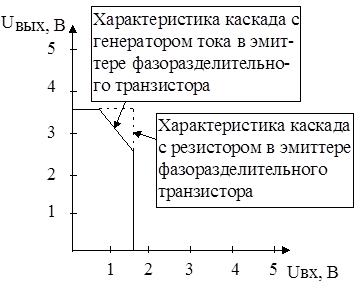

Передаточная характеристика

Рис. 7.5.3. Передаточная статическая характеристика логического элемента ТТЛ

Здесь пунктиром показана характеристика логического элемента с генератором тока вместо эмиттерного сопротивления фазоразделительного каскада, а сплошной линией, – характеристика логического элемента с обычным резистором в эмиттере фазоразделительного транзистора.

Из этой характеристики следует, что генератор тока вместо эмиттерного сопротивления в фазоразделительном каскаде не только повышает быстродействие логического элемента за счет более быстрого рассасывания накопленных зарядов в области базы нижнего транзистора выходного двухтактного каскада при закрывании этого транзистора, но и улучшает передаточную характеристику ТТЛ логического элемента.

8. Логика на МОП транзисторах

В цифровых микросхемах если и применяются полевые транзисторы, то только с изолированным затвором (МОП) и только с индуцированным каналом.

МОП транзисторы имеют четыре вывода:

1) исток, – от которого начинают движение в канале носители электрического заряда;

2) сток, – к которому движутся в канале носители заряда;

3) затвор, – потенциал на котором посредством электрического поля управляет толщиной канала (затворяет или отворяет путь протекания тока, – движения носителей заряда: электронов или дырок);

4) подложка, – полупроводниковый кремниевый кристалл, в объеме которого на малом расстоянии друг от друга методом диффузии сделаны две области с проводимостью, обратной проводимости подложки – это области стока и истока.

На поверхности подложки между стоком и истоком создают тонкий слой окисла кремния (кварцевого стекла SiO2), а поверх него напыляют алюминиевый затвор. Когда на затвор такого МОП транзистора относительно подложки подается отпирающее напряжение, то внутри подложки под затвором между стоком и истоком индуцируются (наводятся) носители заряда с проводимостью, противоположной проводимости подложки, но совпадающей с проводимостью стока и истока. Если теперь подключить сток и исток к источнику питания, то через них и через наведенный канал потечет ток.

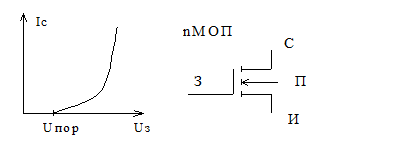

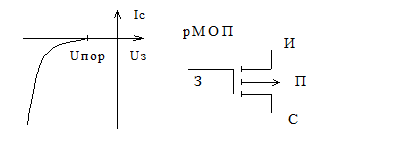

Зависимости тока Iс стока от напряжения затвор–подложка Uз для транзистора с разной проводимостью канала приведены на рис. 8.1. и рис. 8.2.

Рис. 8.1. Зависимость тока Iс стока от напряжения затвор–подложка Uз для транзистора с p проводимостью подложки

Рис.8.2. Зависимость тока Iс стока от напряжения затвор–подложка Uз для транзистора с n проводимостью подложки

На этих же рисунках показаны также и условные графические обозначения этих транзисторов. Следует обратить внимание на то что вывод истока транзистора является как бы продолжением вывода его затвора. Зачастую линию канала вместо штриховой рисуют сплошной (как у МОП транзисторов с встроенным каналом).

МОП транзисторы называют в соответствии с проводимостью канала, а стрелки в их условных графических обозначениях соответствуют проводимости подложки, которая, как было сказано, для таких транзисторов противоположна проводимости канала. Направление стрелки показывает проводимость подложки (внутрь, – транзистор p– типа, наружу, – n– типа). Как известно обозначения n – NEGATIVE (отрицательный, при этом носители заряда, – электроны), а p – POSITIVE (положительный, при этом носители заряда, – дырки).

Значение порогового напряжения при питании + 5 В обычно лежит в пределах: Uпор = 1,5... 3 В. При другом напряжении питания значение порогового напряжения лежит в пределах: Uпор = Uпит/3... 2Uпит/ 3.

Для МОП транзисторов характерны два существенных отличия их от обычных биполярных транзисторов:

– сопротивление канала практически линейно, т. е. ток стока почти линейно зависит от напряжения сток–исток;

– имеется почти полная взаимозаменяемость стока и истока, т.к. ток в канале может протекать в обоих направлениях в зависимости от полярности напряжения, приложенного к каналу.

В цифровых микросхемах эти особенности не являются определяющими, но помнить о них не вредно.

8.1. Инверторы на n –МОП и p –МОП транзисторах

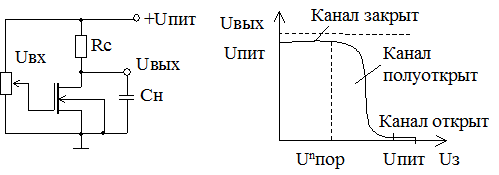

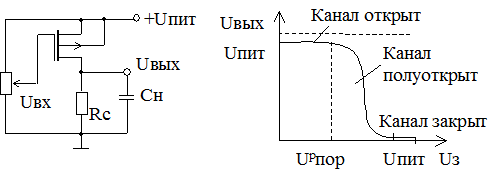

Рис. 8.1.1. Схема включения n –МОП транзистора и передаточная характеристика такого каскада

Здесь Rc – сопротивление стоковой нагрузки, аналогичное сопротивлению коллекторной нагрузки в n–p–n транзисторах.

Оценим с помощью простых расчетов быстродействие такого каскада. Сопротивление канала Rк меняется от десятков МОм в закрытом состоянии до 1…10 кОм в открытом при изменении входного напряжения Uзи от 0 до +Uпит. Считаем, что U1вых = Uпит;

Если Rс = 40 кОм, Rк.откр. = 4 кОм, Uпит. = 10 В, Cнагр. = 20 пФ, и поскольку U0вых = Uпит.× Rк.откр. / (Rс + Rк.откр.), t0,1ф. = Rс × Cнагр., t1,0ф. = Rк.откр. × Cнагр., fmax=1/(t0,1ф.+ t1,0ф.), то:

U0вых = 10 × 4 / (40 + 4) = 0.9 В, t0,1ф. = 40 кОм × 20 пФ = 800 нс

t1,0ф. = 4 кОм × 20 пФ = 80 нс, fmax=1/(t0,1ф.+ t1,0ф.) =1МГц

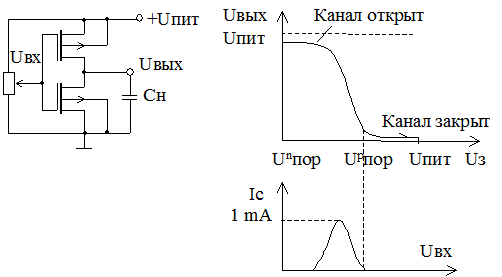

Рис. 8.1.2. Схема включения р –МОП транзистора и передаточная характеристика такого каскада

Так же, как и в предыдущем случае оценим с помощью простых расчетов быстродействие такого каскада.

Считаем, что Uвх. = Uпит. – Uзи,

Поскольку U1вых = Uпит.× Rс / (Rc + Rк.откр.), t0,1 = Rк.откр.× Cнагр., t1,0 = Rс × Снагр., fmax=1/(t0,1ф.+ t1,0ф.), то при Uпит. = 10 В, Rс = 40 кОм, Rк.откр. = 4 кОм, Снагр. = 20 пФ:

U1вых = 9,1 В, U0вых = 0 В,

t,0,1 = 80 нс, t1,0 = 800 нс, fmax =1 МГц

Вместо резистора Rс в действительности (в частности в серии К172) стоит специальный нагрузочный p– МОП транзистор с сопротивлением постоянно открытого канала Rк.откр. = 25…40 кОм.

Эти микросхемы имеют малое быстродействие (tзд.р. = 1 мкс), большую мощность потребления (порядка 40 мВт / логический элемент) и уровни U1вых = 7,5 В, U0вых = 2,3 В, не совместимые с уровнями ТТЛ микросхемами, поэтому в новых разработках серия К172 не применяется.

8.2. Инвертор на КМОП транзисторах

Рис. 8.2.1. Схема включения инвертора на взаимодополняющих, комплиментарных р –МОП и n –МОП транзисторах, передаточная характеристика такого каскада и график импульса тока, протекающего через инвертор при его переключении

Если учесть, что роль сопротивления стоковой нагрузки Rc при перезаряде Cнагр. играют поочередно n– МОП и p– МОП транзисторы с сопротивлением открытого канала Rк.откр. на порядок меньшим, чем резисторы Rс в двух предыдущих случаях, то становится понятно почему быстродействие КМОП логических элементов на порядок выше чем у n– МОП и p– МОП логических элементов: tзд.р. = 0,06 мкс для К561 при Сн = 15 пФ, Uпит = 5 В. В КМОП инверторах U1вых» Uпит, а U0вых» 0.

Мощность, потребляемая логическим элементом КМОП в статическом режиме, близка к нулю (Pстат. = 10 – 4 мВт / корпус), но с ростом частоты переключения схемы динамическая потребляемая мощность Pдин растет в соответствии с формулой:

Pдин = 2 × Cнагр. × f × U2пит,

где Cнагр. – эквивалентная емкость нагрузки микросхемы; f, – частота переключения; Uпит, – напряжение питания.

Такая зависимость объясняется импульсами сквозного тока через оба транзистора в момент переключения.

Например, при частоте переключения f = 1 МГц, Uпит = 10 В, Снагр = 50 пФ потребляемая мощность достигает Pдин = 10мВт.

Зависимость мощности, потребляемой микросхемами различных серий в том числе и КМОП, от частоты переключения приведена на рис.5.2.2.

Очень высокое входное сопротивление МОП транзисторов (Rвх»1012 Ом) ставит проблему защиты от пробоя изоляции входных цепей МОП схем. Основная опасность идет от статического электричества, наводок силовых электромагнитных полей. Для защиты от пробоя на входе каждого КМОП логического элемента в составе микросхемы включают стабилитрон VD1. Его практически никогда не рисуют на схемах логических элементов, но помнить о том, что он есть в каждом КМОП логическом элементе надо.

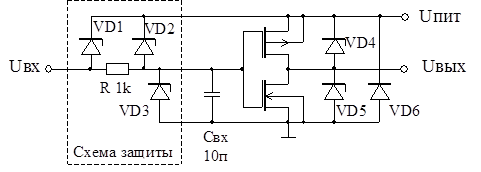

Рис. 8.2.2. Эквивалентная схема КМОП инвертора

В структуре логического элемента КМОП заложены защиты как входов, так и выходов логического элемента. Они обеспечиваются технологией изготовления. На рис.2.6.2. показана эквивалентная схема инвертора КМОП. Цепь R, D1, D2, D3 представляет собой резисторно–диодную структуру с распределенными параметрами, введенную в кристалл логического элемента рядом с p– МОП и n– МОП транзисторами и названа схемой защиты.

Эта цепь защищает вход инвертора от пробоя, резистор защищает выход предыдущего каскада от импульсной токовой перегрузки при заряде емкости Cвх. Диоды D1, D2 и D3 изготовлены таким образом, что напряжение пробоя их в обратном включении составляет 25…50 В, и при сигналах на входе логического элемента, превышающих напряжение пробоя, эти диодные стабилитроны открываются и предохраняют входы полевых транзисторов от высоковольтных выбросов, которые могут привести к пробою изоляции между затвором и каналом полевого транзистора.

Различные p–n переходы, получившиеся при изготовлении областей стоков, истоков и кармана в подложке (кристалле кремния с n проводимостью) на схеме показаны как D4…D6.

Предельно допустимый ток входных стабилитронов 10мА, ток диода D6 больше. При неисправной полярности питания этот диод D6 может сгореть сам или сжечь источник питания, если в источнике нет защиты от короткого замыкания по выходу.

Если потенциалы входов и выходов МОП транзисторов не выходят за пределы 0…+Uпит., то об всех этих диодах можно забыть, поскольку напряжения пробоя этих встроенных стабилитронов превышает 25 В, т.е. больше напряжения питания.

8.3. КМОП логические элементы И–НЕ и или –не

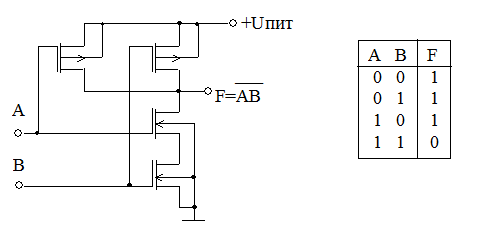

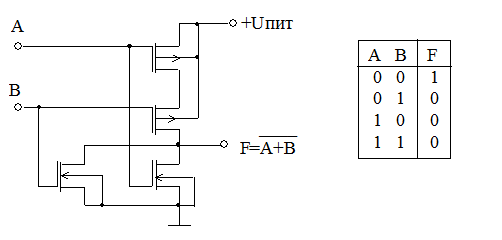

Рис 8.3.1. Схема КМОП логического элемента И–НЕ и его таблица истинности

Чтобы открыть оба нижних транзистора надо, чтобы на входе A и входе B была логическая единица, при этом оба верхних транзистора закроются и на выходе Q будет логический ноль. Если хотя бы на одном или на обоих входах будет логический ноль, то хотя бы один из нижних транзисторов закроется, один из верхних откроется, при этом на выходе будет логическая единица.

Рис 8.3.1. Схема КМОП логического элемента ИЛИ–НЕ и его

таблица истинности

Если на входах A или B (или на обоих) логическая единица, то откроется один или оба из нижних транзисторов, при этом закроется один или оба верхних транзистора, тогда на выходе логический ноль. Если на обоих входах логический ноль, то закроются оба нижних и откроются оба верхних транзистора, при этом на выходе логическая единица.

8.4. Двунаправленный ключ КМОП

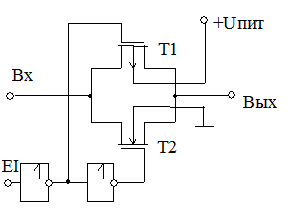

Рис.8.4.1. Упрощенная схема КМОП двунаправленного ключа

Двунаправленным ключом называют также коммутатор цифровых и аналоговых сигналов, переключатель, ключ коммутации (КК). В состав ключа коммутации входят два инвертора, управляющие двумя параллельно включенными комплементарными транзисторами собственно ключа.

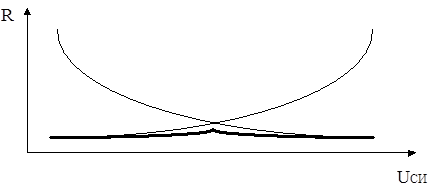

Каждый из этих транзисторов имеет внутреннее сопротивление, существенно зависящее от коммутируемого напряжения, а параллельное их соединение имеет намного меньшую заисимость общего сопротивления от коммутируемого напряжения, как это показано на рис.8.4.2.

Рис.8.4.2. Зависимости внутреннего сопротивления комплементарных транзисторов от напряжения сток–исток, показанные тонкими линиями, и заисимость их общего сопротивления, показанная жирной линией, от напряжения, коммутируемого ключем

Рассмотрим два режима работы ключа коммутации:

1. На управляющем входе EI = 1. На выходе первого управляющего инвертора 0, значит и верхний p– МОП транзистор T1 открыт, при этом на выходе второго инвертора 1, значит и нижний n– МОП транзистор T2 открыт. Следовательно в ключе открыты оба транзистора.

2. На управляющем входе EI = 0. На выходе первого управляющего инвертора 1, значит и верхний p– МОП транзистор T1 закрыт, при этом на выходе второго инвертора 0, значит и нижний n– МОП транзистор T2 закрыт. Следовательно в ключе оба транзистора закрыты.

Для ключа К176КТ1 характерны следующие параметры:

Rоткр. =500 Ом; tзд.р. = 10…25 нс.

При Rнагр. = 10 кОм, fсиг. = 10 кГц развязку между входом и выходом можно определить из: 20 дб ×(Uвых.откр. / Uвых.закр.) ³ 65 дб.

Сопротивление открытого ключа К561КТ3 еще меньше, чем ключа К176 КТ1, а именно Rоткр. = 80 Ом.

8.5. Схемотехника КМОП микросхем малой

интеграции

В КМОП логике не один базовый элемент как в ТТЛ (4И–НЕ), а два базовых элемента: инвертор НЕ и ключ коммутации КК. Напряжение между затвором и подложкой МОП транзистора открывает или закрывает канал транзистора, причем открыт или закрыт транзистор не зависит от напряжения на стоке и истоке (лишь бы не открылись диоды структуры полупроводникового кристалла). Это позволяет соединить каналы МОП транзисторов последовательными цепочками, а также подавать на эти каналы любые напряжения (в пределах 0…+Uпит) с уверенностью, что все это не изменит состояние канала, не изменит его сопротивление.

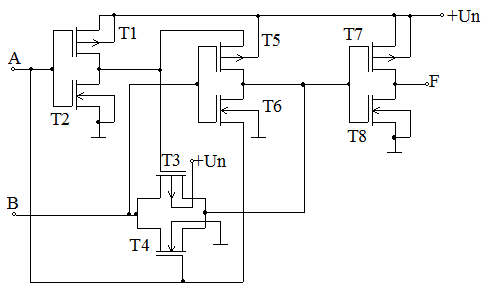

Рис.8.5.1. Схема КМОП "исключающее ИЛИ" К176ЛП2

Для примера построения КМОП микросхем можно рассмотреть микросхему КМОП "исключающее ИЛИ" К176ЛП2. При анализе ее работы следует помнить, что из каждой пары транзисторов верхний p –МОП открывается логическим нулем, нижний n –МОП, – логической единицей. В каждом из трех инверторов один из транзисторов открыт, второй закрыт, в ключе коммутации одновременно открываются или закрываются оба транзистора. При анализе работы схемы основное внимание надо уделить рассмотрению работу инвертора на T5 и T6, поскольку состояния транзисторов этого инвертора зависят не только от потенциалов на их затворах, но и от потенциалов на их истоках.

8.6. Разновидности Выходов КМОП микросхем и

особенности их подключения

В КМОП, как и в ТТЛ, есть схемы с открытым стоком и Z– состоянием. Выходы логического элемента КМОП не рекомендуется соединять непосредственно между собой, как в ТТЛ. Особенно важно это для элементов с повышенным выходным током. Если требуется увеличить выходной ток, то допускается параллельное соединение входов и выходов логических элементов, но они должны быть из одного корпуса микросхемы. Нельзя применять емкости нагрузки C > 500 пФ для обычных логических элементов и C > 5000 пФ для буферных и высоковольтных оконечных элементов, поскольку такой конденсатор равноценен короткому замыканию для импульса тока; если же последовательно с выходом логического элемента включить гасящий резистор для ограничения импульса тока, то емкость нагрузки может быть любой.

При соединении выходов логического элемента с шиной питания или с корпусной шиной через один из выходных транзисторов протекает ток, ограничиваемый только сопротивлением открытого канала. Этот ток вызывает нагрев транзистора и всего логического элемента и может вызвать тепловой пробой, если рассеиваемая мощность превышает допустимую: 100 мВт для одного транзистора и 500 мВт для корпуса микросхемы. Благодаря отрицательному температурному коэффициенту тока канала МОП транзисторов они обладают внутренней кратковременной защитой от нагрева. Ориентировочные значения токов короткого замыкания и рассеиваемой мощности даны в таблице 1, приведенной в [2].

Таблица 8.1

Токи короткого замыкания и рассеиваемая мощность МОП транзисторов в зависимости от напряжения питания при 25 0 С

| р–каналь | ный | n–каналь | ный | |

| Uпит, В | I, мА | Р, мВт | I, мА | Р, мВт |

| 5.1 | 0,13 | 4.4 | 0,097 | |

| 26.5 | 7,0 | 6,25 | ||

| 42,1 | 52.4 | 41,3 |

В некоторых КМОП микросхемах выходные каскады имеют повышенную нагрузочную способность, такие микросхемы называют буферными или драйверами. По сравнению с обычными микросхемами они имеют меньшее сопротивление открытого канала, как это можно видеть по таблице 2.

Таблица 8.2

Сопротивление открытого канала выходных транзисторов обычных и буферных микросхем в зависимости от напряжения питания

| Напряжение питания, В | ||

| Сопротивление открытого канала, кОм | ||

| – при буферном выходном каскаде | 1,5 | 0,5 |

| – при обычном выходном каскаде | 2,5 | 0,75 |

8.7. Подключение Входов КМОП микросхем

Входы КМОП микросхем никогда не должны оставаться ни к чему неподключенными – это одно из обязательных правил.

Входное сопротивление КМОП микросхем почти на десять порядков больше, чем ТТЛ микросхем, и соответственно, примерно во столько же раз сильнее влияют помехи на “висящий”, ни к чему не подключенный, вход КМОП микросхемы, чем на такой же вход ТТЛ микросхемы.

Из практики работы с микросхемами ТТЛ серий известно, что на свободном, ни к чему не подключенном входе ТТЛ микросхемы самопроизвольно устанавливается так называемая "висячая единица", т.е. напряжение, примерно равное полтора вольта. Это можно показать, анализируя входную статическую характеристику логического элемента ТТЛ, представленную на рис. 2.4.6.1, на которой при входном токе, равном нулю, напряжение примерно равно полутора вольтам.

Практика работы с КМОП микросхемами показывает, что часто при обрыве дорожки платы, идущей к какому–либо входу КМОП микросхемы, на выходе этой микросхемы появляется переменное напряжение с частотой питающей сети.

Иногда при обрыве соединения на входе КМОП микросхемы напряжение на этом входе медленно дрейфует, плавает. При этом возможны так называемые "мерцающие" отказы в работе устройства, когда устройство нормально работает некоторое время, а затем без какой–либо причины оно выходит из строя, а затем, через какое–то время устройство вновь начинает нормально работать.

Из–за тиристорного эффекта, присущего КМОП микросхемам (особенно их первым сериям), устройства с этими микросхемами не разрешается вставлять в разъемы, на которых уже могут присутствовать напряжения питания и входные сигналы. В таких случаях возможны ситуации, когда напряжение на вход КМОП микросхемы поступает раньше, чем напряжение питания. При этом полупроводниковые структуры КМОП инвертора могут открыться аналогично тиристору, включенному анодом к плюсу питания, а катодом, – к земле.

Такой тиристор перегружает источник питания, а главное, перегревается сам, и вполне может через некоторое время (через секунду – другую) сгореть от теплового пробоя. По этой же причине устройства с КМОП микросхемами не разрешается вытаскивать из разъемов на которых присутствуют напряжения питания и входные сигналы.

Без потери работоспособности неиспользуемые И входы КМОП микросхем могут быть подключены непосредственно к плюсу питания, а ИЛИ входы, – к корпусной шине; при этом пороги переключения соседних входов немного смещаются. Можно неиспользованные входы КМОП микросхем подключать параллельно соседним используемым, но при этом эти входы дополнительно нагружают выход предыдущей микросхемы пропорционально числу подключенных входов.

Очень большое входное сопротивление КМОП микросхем позволяет при расчете разветвления сигналов с одного выхода на несколько входов пренебрегать активной, резистивной составляющей их входного сопротивления. Число входов, которые допустимо подключать к одному выходу КМОП микросхемы, определяется эквивалентной входной емкостью одного входа и предельной емкостью нагрузки, при которой характеристики микросхем (в основном динамические) не выходят из заданных пределов.

Входная емкость большинства КМОП микросхем составляет 5... 15 пф, а максимальная емкость нагрузки, при которой характеристики микросхем не выходят из заданных пределов, обычно равна 500 пф, поэтому обычно коэффициент разветвления Кразв. = 30... 100.

Статическая помехоустойчивость КМОП микросхем зависит от напряжения питания и увеличивается с его ростом. Допустимое напряжение помех можно выразить как долю напряжения питания таким образом:

U0пом» U1пом» Uпит / 3.

Особенностью КМОП микросхем является очень большой разброс и нестабильность напряжения переключения, – область входных напряжений, в которой может находиться порог переключения КМОП микросхем, составляет примерно треть напряжения питания (тогда как для ТТЛ микросхем эта область на один … два порядка меньше).

9. Эмиттерно–связанная логика.

Микросхемы эмиттерно–связанной логики (ЭСЛ) являются самыми быстродействующими из всех типов логик, и обеспечивается это за счет целого ряда особенностей этой логики.

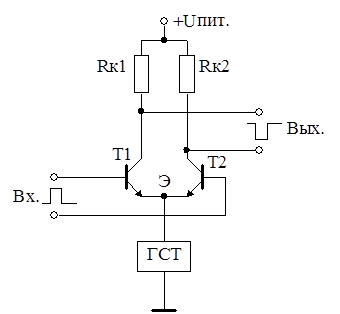

Главная особенность эмиттерно–связанной логики (ЭСЛ), повышающая ее быстродействие, заключается в том, что схема ее логического элемента основана на дифференциальном усилителе (балансном каскаде), дифференциальном переключателе тока, показанном на рис. 3.1, два транзистора которого переключают ток и не попадают в режим насыщения. Благодаря этому значительно сокращается время выхода транзисторов логического элемента из открытого состояния и существенно повышается общее быстродействие.

В эмиттерную цепь этих транзисторов включен генератор стабильного тока (ГСТ), который ограничивает величину тока, протекающего через тот из двух транзисторов, который открыт.

Рис.9.1. Основа ЭСЛ логического элемента, – дифференциальный усилитель, в эмиттерную цепь которого включен генератор стабильного тока (ГСТ).

Величина тока, задаваемая генератором стабильного тока (ГСТ), и сопротивления резисторов коллекторных нагрузок каскадов выбраны такими, чтобы исключить режим насыщения транзисторов в открытом состоянии независимо от разброса усиления этих транзисторов, что невозможно обеспечить в КМОП и в обычных ТТЛ сериях (кроме серий с транзисторами Шоттки).

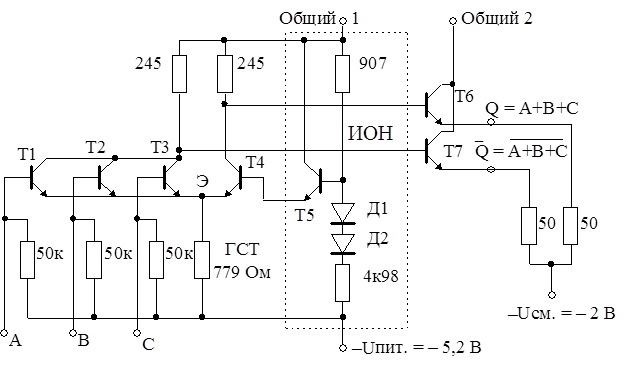

В ЭСЛ микросхемах имеется два противофазных выхода, – прямой и инверсный, поэтому в устройствах на ЭСЛ микросхемах отсутствуют промежуточные инверторы, которые в устройствах на ТТЛ и КМОП микросхемах вносят дополнительную задержку и снижают быстродействие.

С целью уменьшения времени перезаряда паразитных емкостей за счет уменьшения выходного сопротивления ЭСЛ логических элементов в их схемы введены мощные эмиттерные повторители с сопротивлениями нагрузки малой величины 50 Ом.

Уменьшение задержки распространения в ЭСЛ сериях достигается также и за счет уменьшения длительности фронтов выходных импульсов за счет уменьшения перепада напряжения на фронтах импульсов:

В ЭСЛ сериях U1ВЫХ = – 0,96 В, U0ВЫХ = – 1,65 В,

DUВЫХ = | U1ВЫХ – U0ВЫХ | = 0,69 В,

В ТТЛ сериях U1ВЫХ = 3,6 В, U0ВЫХ = 0,1 В,

DUВЫХ = | U1ВЫХ – U0ВЫХ | = 3,5 В,

В КМОП сериях при питании +9 В U1ВЫХ = 9 В, U0ВЫХ = 0 В,

DUВЫХ = | U1ВЫХ – U0ВЫХ | = 9 В.

Даже если бы крутизна фронтов выходных импульсов у микросхем ЭСЛ, ТТЛ и КМОП была бы одинаковой, то только за счет уменьшения перепада напряжения на фронтах импульсов длительности фронтов выходных импульсов в ЭСЛ были бы в пять раз меньше, чем в ТТЛ, и в тринадцать раз меньше, чем в КМОП.

Но уменьшение перепада напряжения на фронтах импульсов означает меньшую разницу между уровнями нуля и единицы, а значит и помехи меньшей величины могут привести к неправильному срабатыванию ЭСЛ микросхем. Для снижения влияния помех в ЭСЛ микросхемах применяются следующие приемы:

1. С корпусной шиной в ЭСЛ микросхемах соединен положительный вывод питания, а не отрицательный, как во других логиках. При таком подключении чувствительность логического элемента к помехам по питанию (отрицательному) ослабляется благодаря наличию генератора стабильного тока и чем выше степень его стабилизации тем сильнее ослабляется эмиттерный синфазный сигнал помехи.

2. Порог переключения ЭСЛ логического элемента стабилизируется с помощью источника опорного напряжения (ИОН), который фиксирует напряжение на базе одного из транзисторов дифференциального переключателя тока.

3. Корпусная шина питания (положительного) маломощных чувствительных каскадов микросхем развязана от корпусной шина питания мощных выходных повторителей, являющихся основными источниками помех.

4. Сопротивления нагрузки выходных эмиттерных повторителей подключаются не к шине отрицательного питания, а к отдельному источнику смещения. Напряжение источника смещения меньше, чем на шине отрицательного питания, поэтому мощность, рассеиваемая этими сопротивлениями нагрузки, практически на порядок снижена.

Вышеуказанные средства обеспечивают приемлемую помехоустойчивость ЭСЛ микросхем. Схема трехвходового логического элемента приведена на рис.3.2.

Рис.9.2. Схема трехвходового логического элемента ЭСЛ серии К500

В первых ЭСЛ сериях (отечественная серия К500) в качестве генератора стабильного тока (ГСТ) служил резистор, сопротивление которого больше, чем сопротивления коллекторных нагрузок.

В процессе развития ЭСЛ серий (отечественная серия К1500) были применены следующие улучшения:

– стали использоваться более быстродействующие транзисторы с граничной частотой fТ» 4,5 ГГц, что обеспечивает tЗД» 0,75 нс (вместо fТ» 1,5 ГГц, которая обеспечивала tЗД» 2 нс в серии К500);

– стала применяться более плотная "упаковка", т.е. вместо десяти логических элементов на миллиметр поверхности кристалла микросхемы в серии К500 в следующей серии К1500 двадцать логических элементов на миллиметр поверхности кристалла и это при том, что число транзисторов в одном логическом элементе увеличилось вдвое;

– стали использоваться более стабильные и сложные генераторы стабильного тока и источники опорного напряжения;

– напряжение питание уменьшили с 5,2 В до 4 В, но при этом обеспечивается совместимость между этими сериями по уровням логического нуля и единицы.

В ЭСЛ сериях неиспользованные входы можно оставлять ни к чему не подключенными, так как они внутри микросхем соединены с минусом питания через резисторы 50 кОм.

Выходы ЭСЛ микросхем можно соединять друг с другом с учетом их полярности: прямые выходы можно соединять в монтажное ИЛИ, а инверсные выходы, – в монтажное И.

ЛИТЕРАТУРА

Основная

1. Зельдин Е.А. Цифровые интегральные микросхемы в информационно–измерительной аппаратуре. Л. Энергоатомиздат. 1986 г. стр. 93. УДК 681.518.3:621.3.049.77.

2. Потемкин И.С. Функциональные узлы цифровой автоматики.– М.: Энергоатомиздат, 1988.– 320 с.

3. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник.– М.: Радио и связь, 1990.– 304 с.

4. Цифровые интегральные микросхемы: Справочник.– Богданович М.И. и др.– Мн.: Беларусь, 1991.– 493 с.

5. Шило В.Л. Популярные цифровые микросхемы: Справочник.– 2–е изд., исправленное.– М.: Радио и связь, 1989.– 352 с.

6. Янсен Й. Курс цифровой электроники: В 4–х т. Пер. с голланд.– М.: Мир, 1987.

Дополнительная

1. Отраслевой стандарт. Микросхемы интегральные полупроводниковые серий 131, К131, 155, К155, 158, К158. Руководство по применению. ОСТ 11340.909–80.

2. Отраслевой стандарт. Микросхемы интегральные серий 564. Руководство по применению. ОСТ 11340.907–80.

3. Храбров Е.А., Красовская Н.А. Методические указания и задания по выполнению контрольной работы для студентов специальности 20.05 по курсу "Основы Цифровой электроники" заочного факультета. Гомельский политехнический институт.: Метод.указ.№ 1907, 100 экз., 1994.– 34 с.

4. Храбров Е.А. Практическое руководство по выполнению лабораторных работ по курсу "Электронные цепи дискретного действия" для студентов специальности Т.07.02.01. Гомельский политехнический институт.: Метод.указ.№ 2255, 50 экз., 1998.– 15 с.

Содержание

Введение..............................................................................................3

1.Достоинства и недостатки цифровой электроники........................3

2. Двоичные сигналы..........................................................................5

3. Системы счисления в цифровой электронике...............................8

4. Алгебра логики.....................................................................…......12

4.1. Функции Булева базиса И, ИЛИ, НЕ........................................13

4.2. Инвертирующие базисы, отрицательная логика........................17

4.3. Совершенные нормальные формы (СДНФ и СКНФ)

записи булевых выражений..........................................…..........21

4.4. Преобразование таблицы истинности в булево выражение.....22

4.5. Основные законы булевой алгебры и правила

преобразований..............................................................….......23

4.6. Минимизация логических функций алгебраическим

способом и по картам Карно..........................................….......23

4.7. Построение комбинационных логических схем по

заданным булевым выражениям..............................................28

4.8. Особенности построения логических схем в

инвертирующих базисах...........................................................30

5. Цифровые микросхемы

5.1. Классификация и обозначения цифровых микросхем.............33

5.2. Параметры цифровых микросхем.............................................38

6. Диодные схемы И, ИЛИ, транзисторная схема НЕ,

диодно–транзисторная логика.............................................…....42

7. Транзисторно–транзисторная логика...........................................47

7.1. Транзисторы Шоттки.........................................................…....49

7.2. Состав ТТЛ логических микросхем малой интеграции.……...50

7.3. Выходные каскады ТТЛ микросхем..........................................53

7.4. Входные каскады ТТЛ микросхем...................................…......58

7.5. Статические характеристики ТТЛ микросхем..................….....59

8. Логика на МОП транзисторах..............................................….....61

8.1. Инверторы на n– МОП и p– МОП транзисторах..............….......63

8.2. Инвертор на КМОП транзисторах..........................................…64

8.4. КМОП логические элементы И–НЕ и ИЛИ –НЕ...................….67

8.6. Двунаправленный ключ КМОП..........................................…....68

8.7. Схемотехника КМОП микросхем малой интеграции............…69

8.8. Разновидности выходов КМОП микросхем и особенности

их подключения.........................................…..............................70

8.9. Подключение входов КМОП микросхем....……........................71

9. Эмиттерно–связанная логика....................................................….73

Литература...................................................................................…...76

30.09.03

Date: 2015-05-09; view: 2764; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |