Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

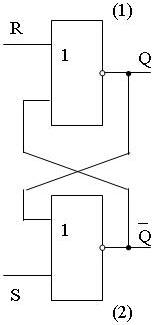

Триггеры

Триггером называют логическую схему с положительной обратной связью, имеющую два устойчивых состояния – единичное и нулевое, которые обозначаются соответственно "1" и "0". В основе любого триггера находится кольцо из двух инверторов (рис. 5.5.1, а, б, в). Триггер является элементом памяти последовательностных логических устройств, на схемах он обозначается буквой "Т".

Рис. 5.5.1. Структурная схема триггера

При подаче питания в результате переходных процессов один из инверторов устанавливается в единичное состояние, а другой – в нулевое. В дальнейшем состояние логических элементов (ЛЭ) сохраняется, так как сигнал с выхода одного ЛЭ поддерживает состояние другого ЛЭ. Общепринято такую схему называть элементом памяти или защелкой.

Входы триггера разделяют на информационные и управляющие (вспомогательные). Это разделение в значительной степени условно.

Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации. Как правило, триггеры имеют 2 выхода: прямой и инверсный.

Триггеры классифицируют по способу приема информации, принципу построения и функциональным возможностям.

По способу приема информации различают асинхронные и синхронные триггеры. Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «стробирующий», «тактирующий».

Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С.

Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С -вход) или от 1 к 0 (инверсный динамический С -вход).

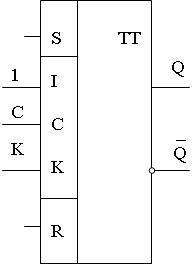

По способу построения различают одно- и двухступенчатые триггеры. В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом – две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают "ТТ. "

По функциональным возможностям триггеры разделяют на следующие классы:

· с раздельной установкой состояния 0 и 1 (RS -триггеры);

· универсальные (JK -триггеры);

· с приемом информации по одному входу D (D -триггеры, или триггеры задержки);

· со счетным входом Т (Т -триггеры).

Входы триггеров обычно обозначают следующим образом:

· S – вход для установки в состояние «1»;

· R – вход для установки в состояние «0»;

· J – вход для установки в состояние «1» в универсальном триггере;

· К – вход для установки в состояние «0» в универсальном триггере;

· Т – счетный (общий) вход;

· D – вход для установки в состояние «1» или в состояние «0»;

· V – дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V).

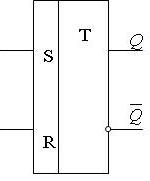

Асинхронный R-S триггер. Схемных реализаций R-S триггеров достаточно много, поэтому необходимо говорить, прежде всего, о логических операциях, т.е. надо составить таблицу истинности (табл. 5.5.1). Условное обозначение R-S триггера приведено на рис. 5.5.2.

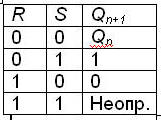

Таблица 5.5.1.

|

|

Рис.5.5.2. Условное обозначение R-S триггера

Триггер этот называется асинхронным, т.к. переходит в новое состояние сразу после поступления входного сигнала. При отсутствии сигналов на обоих входах триггер сохраняет на своем выходе предшествующее состояние, т.е.  . При подаче "1" на "установочный" вход S триггер переходит в состояние

. При подаче "1" на "установочный" вход S триггер переходит в состояние  . При поступлении "1" на "сбросовый" вход R триггер устанавливается в состояние

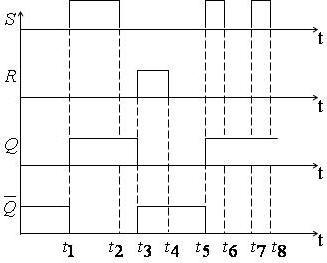

. При поступлении "1" на "сбросовый" вход R триггер устанавливается в состояние  . Т.е. триггер – это аналог реле, но может рассматриваться и как элемент памяти, т.к. сохраняет информацию при R=S=0. Команда "включить-выключить S=R=1 " является недопустимой. На рис. 5.5.3. приведены временные диаграммы работы триггера. При

. Т.е. триггер – это аналог реле, но может рассматриваться и как элемент памяти, т.к. сохраняет информацию при R=S=0. Команда "включить-выключить S=R=1 " является недопустимой. На рис. 5.5.3. приведены временные диаграммы работы триггера. При  , когда S=1, триггер переходит в состояние Q=1 и сохраняет его до прихода сигнала R=1 в момент

, когда S=1, триггер переходит в состояние Q=1 и сохраняет его до прихода сигнала R=1 в момент  , когда Q=0,а

, когда Q=0,а  .

.

|

|

| Рис.5.5.3. Временные диаграммы работы R-S триггера | Рис.5.5.4. Реализация R-S триггера на логических элементах " И-НЕ " |

Реализация R-S триггера возможна на логических элементах " И-НЕ " и " ИЛИ-НЕ ".

На рис. 5.5.4. использованы элементы "И-НЕ", таблица истинности соответствует таблице 5.5.1. Действительно, при R=S=0,  . Предположим при этом, что исходное состояние триггера

. Предположим при этом, что исходное состояние триггера  =1.

=1.

Тогда на нижнем (втором) элементе на обоих входах сигналы "1", а следовательно  . На входах же элемента первого имеем

. На входах же элемента первого имеем  =1 и

=1 и  , тогда на его выходе

, тогда на его выходе  Т.е.

Т.е.  , что соответствует таблице 5.5.1.

, что соответствует таблице 5.5.1.

А теперь предположим, что при тех же R=S=0 имеем в исходном состоянии  . Тогда на входах второго элемента имеем

. Тогда на входах второго элемента имеем  = 1 и

= 1 и  , а на его выходе

, а на его выходе  . На входах же первого элемента имеем

. На входах же первого элемента имеем  и

и  , значит на выходе

, значит на выходе  . Или

. Или  что соответствует все той же таблице 5.5.1. (первой строке).

что соответствует все той же таблице 5.5.1. (первой строке).

Рассмотрим вторую строку: R =0, S =1 или  =1,

=1,  =0. Тогда

=0. Тогда  обязательно, а на выходе второго элемента

обязательно, а на выходе второго элемента  . На входах же первого элемента

. На входах же первого элемента  =0,

=0,  , значит на его выходе

, значит на его выходе  . Если предположить, что на выходе второго элемента как-то было

. Если предположить, что на выходе второго элемента как-то было  , то на входах первого имеем

, то на входах первого имеем  =0 и

=0 и  , а на его выходе

, а на его выходе  и тогда на входах второго

и тогда на входах второго  =1 и

=1 и  , а на выходе

, а на выходе  , т.е. всё правильно.

, т.е. всё правильно.

Третья строка: R =1, S =0 или  =0,

=0,  =1. На выходе второго элемента при

=1. На выходе второго элемента при  =0 обязательно будет

=0 обязательно будет  . Тогда на входах первого элемента

. Тогда на входах первого элемента  =1 и

=1 и  значит на выходе

значит на выходе  , что правильно.

, что правильно.

Четвёртая строка: S =1, R =1 или  =0,

=0,  =0. Тогда должно быть

=0. Тогда должно быть  и

и  . Но это неприемлемо по двум причинам:

. Но это неприемлемо по двум причинам:

· не могут прямое и инверсное значения одной и той же величины быть одинаковыми ( );

);

· состояние на практике  =1 является неустойчивым и после снятия сигналов на входах, т.е.

=1 является неустойчивым и после снятия сигналов на входах, т.е.  и

и  триггер самопроизвольно придет в одно из двух возможных устойчивых состояний, когда либо

триггер самопроизвольно придет в одно из двух возможных устойчивых состояний, когда либо  , либо

, либо  . Поэтому команда R=S =1 не используется, а триггер этого состояния не запоминает.

. Поэтому команда R=S =1 не используется, а триггер этого состояния не запоминает.

На рис. 5.5.5. приведена схема асинхронного R-S триггера, выполненного на элементах " ИЛИ-НЕ ".

Таблица истинности для схемы на рис. 5.5.4. остается прежней, т.е. описывается табл. 5.5.1.

Рис. 5.5.5. Схема асинхронного R-S триггера, выполненного на элементах "ИЛИ-НЕ"

Первая строка таблицы 5.5.1. R= 0, S= 0. Предположим, что  =1, тогда на выходе второго элемента получаем

=1, тогда на выходе второго элемента получаем  . На входах первого элемента R =0 и

. На входах первого элемента R =0 и  , а на выходе

, а на выходе  , что верно – триггер сохранил своё состояние. Если предположить, что

, что верно – триггер сохранил своё состояние. Если предположить, что  , то на выходе второго получим

, то на выходе второго получим  , на входах первого R =0 и

, на входах первого R =0 и  , а значит

, а значит  , т.е. всё выполняется.

, т.е. всё выполняется.

Вторая строка: R =0, S =1; При S =1 вне зависимости от того, что идёт по второму входу на выходе второго элемента получаем  ; На входах первого элемента имеем R =0 и

; На входах первого элемента имеем R =0 и  , значит на выходе получаем

, значит на выходе получаем  .

.

Третья строка: R =1, S =0. При R =1 на выходе первого элемента обязательно будет  . Тогда на входах второго элемента S =0 и

. Тогда на входах второго элемента S =0 и  , значит

, значит  , что верно.

, что верно.

Четвёртая строка R =1= S по тем же причинам, что и для реализации на элементах "И-НЕ" не используется.

Синхронные триггеры. Все синхронные триггеры имеют дополнительный "тактовый" вход, на который подаются тактовые импульсы. Этот вход используется в случае необходимости синхронизировать процесс переключения многих триггеров (в ЭВМ к примеру). Т.е. такой триггер воспринимает информацию на своих входах только при наличии тактового импульса и переходит в новое состояние в момент среза (окончание) тактового импульса.

В течение же самого тактового импульса на выходе триггера сохраняется предшествующее состояние  , информация о котором может быть использована при определении направления его переключения. Отсюда большие логические возможности, чем у асинхронных триггеров.

, информация о котором может быть использована при определении направления его переключения. Отсюда большие логические возможности, чем у асинхронных триггеров.

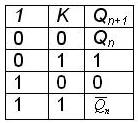

J-K триггер. J-K триггер называют ещё универсальным в связи с тем, что при соответствующем подключении входов он может выполнять функции R-S, D-Т триггеров.

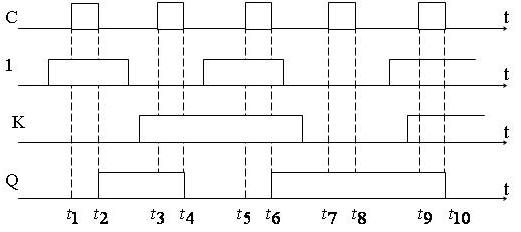

Обозначение J-K триггера приведено на рис. 5.5.6., а работа описывается таблицей 5.5.2.

Таблица 5.5.2.

|

|

Рис.5.5.6. Обозначение J-K триггера

Аналогично R-S триггеру J-K триггер при нулевых сигналах на своих входах сохраняет предыдущее состояние. Тактовый вход "С" логической функции не выполняет, он только синхронизирует работу. Сигнал "1" на входе J включает триггер в состояние  . Сигнал "1" на входе K выключает (сбрасывает) триггер

. Сигнал "1" на входе K выключает (сбрасывает) триггер  . При J=K =1 состояние триггера меняется на противоположное по отношению к начальному, что его отличает существенно от R-S триггера. На рис.5.5.7. приведены временные диаграммы работы J-K триггера. При С =1 (

. При J=K =1 состояние триггера меняется на противоположное по отношению к начальному, что его отличает существенно от R-S триггера. На рис.5.5.7. приведены временные диаграммы работы J-K триггера. При С =1 ( ), J =1 в момент среза импульса

), J =1 в момент среза импульса  триггер переходит в состояние Q =1. На интервале

триггер переходит в состояние Q =1. На интервале  триггер информацию не воспринимает.

триггер информацию не воспринимает.

Рис.5.5.7. Временные диаграммы работы J-K триггера

На интервале  при K =1, J =0 в момент

при K =1, J =0 в момент  триггер переключается Q =0. На интервале

триггер переключается Q =0. На интервале  триггер информацию не воспринимает, а в момент

триггер информацию не воспринимает, а в момент  при J =1, К =1 переходит в противоположное состояние Q =1. На интервале

при J =1, К =1 переходит в противоположное состояние Q =1. На интервале  информация не воспринимается, а в момент

информация не воспринимается, а в момент  при J =1, К =1 триггер снова меняет свое состояние Q =0.

при J =1, К =1 триггер снова меняет свое состояние Q =0.

В общем случае схемная реализация J-K триггеров достаточно сложна, однако при их выполнении в виде ИМС она разработчика может не интересовать. Промышленность выпускает J-K триггеры в виде ИМС с дополнительными входами R и S. Это асинхронные входы: при R =0, S =1 триггер сразу устанавливается  , а при R =1, S =0 в

, а при R =1, S =0 в  . На основе J-K триггера строится целый ряд других триггеров.

. На основе J-K триггера строится целый ряд других триггеров.

Синхронный R-S триггер на базе J-K триггера. Используем в качестве установочных входов J=S и K=R, исключим возможность ситуации J=K =1, тогда в таблице 5.5.2. используются первые три строки, как у обычного R-S триггера. Отличием является лишь наличие тактового входа С, импульс приходящий по которому, позволяет воспринимать информацию на входах R и S. Переключение происходит в момент среза тактового импульса. Обозначение такого триггера приведено на рис. 5.5.8.

Рис.5.5.8. Обозначение синхронного R-S триггера на базе J-K триггера

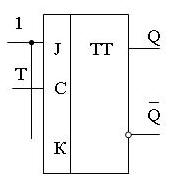

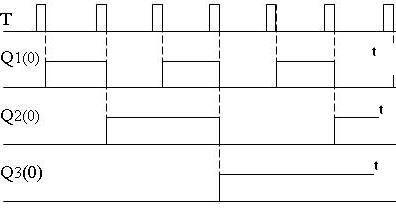

Счётный Т-триггер. Т -триггер работает в соответствии с 4-й строкой таблицы 5.5.2. Для реализации этого в J-K триггере входы J и K подсоединяют к потенциалу, соответствующему логической единице: J=K =1. Таким образом, триггер переключается в противоположное состояние в момент среза тактового импульса  . Т.е. счётный триггер имеет только единственный вход, который обозначается Т (см. рис. 5.5.9.). Временные диаграммы приведены на рис. 5.5.10.

. Т.е. счётный триггер имеет только единственный вход, который обозначается Т (см. рис. 5.5.9.). Временные диаграммы приведены на рис. 5.5.10.

|

|

| Рис. 5.5.9.Счётный Т -триггер | Рис. 5.5.10. Временные диаграммы работы J-K триггера |

Очевидно, что частота сигнала Q вдвое ниже, чем частота тактовых импульсов. Счётные триггеры широко используются в счётчиках, распределителях, делителях частоты, переключающих устройствах.

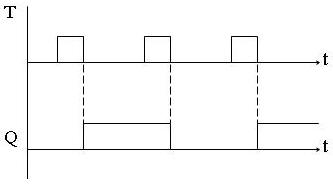

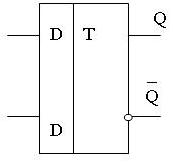

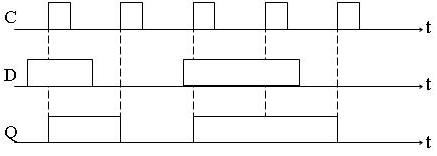

D -триггер (ячейка памяти). D -триггер помимо тактового входа C имеет ещё лишь один вход D и работает в соответствии со 2-й и 3-й строками таблицы 5.5.2. Т.е. триггер запоминает сигнал на входе D в момент тактового импульса и хранит его до следующего тактового импульса  . Поэтому D -триггер является элементом памяти. D -триггеры выпускаются в виде отдельных ИМС, в каждом корпусе как правило 2 или 4 триггера. Отличительной особенностью D триггеров в виде микросхем является переключение не по срезу, а по фронту тактового импульса. Обозначение и диаграммы работы D -триггера на ИМС приведены соответственно на рис. 5.5.11. и на рис. 5.5.12.

. Поэтому D -триггер является элементом памяти. D -триггеры выпускаются в виде отдельных ИМС, в каждом корпусе как правило 2 или 4 триггера. Отличительной особенностью D триггеров в виде микросхем является переключение не по срезу, а по фронту тактового импульса. Обозначение и диаграммы работы D -триггера на ИМС приведены соответственно на рис. 5.5.11. и на рис. 5.5.12.

|

|

| Рис. 5.5.11.Обозначение D -триггера | Рис. 5.5.12. Временные диаграммы работы D- триггера |

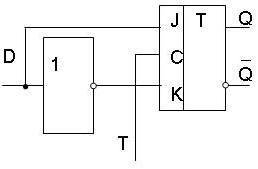

Иногда ИМС D -триггеров снабжают установочными входами R и S. D -триггер выполняется и на основе J-K триггера при условии обеспечения J =  = D. Для этого на входе J-K триггера включают элемент " НЕ ", как показано на рис. 5.5.13. Т.е. здесь помимо тактового входа С имеется только один вход D. Очевидно, что здесь так же реализуется вторая и третья строки табл. 5.5.2.

= D. Для этого на входе J-K триггера включают элемент " НЕ ", как показано на рис. 5.5.13. Т.е. здесь помимо тактового входа С имеется только один вход D. Очевидно, что здесь так же реализуется вторая и третья строки табл. 5.5.2.

Рис. 5.5.13. D -триггер с установочными входами

5.5.2. Счётчики

Счетчик – такое устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счетчики строятся на Т -триггерах.

Основной параметр счетчика – модуль (коэффициент) счета – максимальное число единичных сигналов, которое может быть сосчитано счетчиком. Счетчики обозначают через "СТ" (от англ. counter).

Счетчики классифицируют:

1. По модулю счета:

· двоично-десятичные;

· двоичные;

· с произвольным постоянным модулем счета;

· с переменным модулем счета;

2. По направлению счета:

· суммирующие;

· вычитающие;

· реверсивные;

3. По способу формирования внутренних связей:

· с последовательным переносом;

· с параллельным переносом;

· с комбинированным переносом;

· кольцевые.

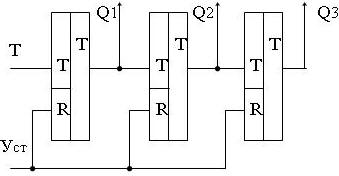

Двоичные счётчики производят счёт поступающих импульсов в двоичной системе счисления, и результат записывается в двоичном коде. Максимальное число N, которое может быть записано в счётчике, равно ( ), где n-число разрядов счетчика. Каждый разряд счетчика включает в себя триггер со счётным запуском, т.е. синхронный Т-триггер. На рис. 5.5.14. приведена схема 3-х разрядного двоичного счётчика на сложение, она выполнена путём последовательного соединения трёх счётных триггеров. Счёт возможен от 0 до 7. Если надо увеличить N, то увеличивают количество разрядов подключением дополнительных триггеров.

), где n-число разрядов счетчика. Каждый разряд счетчика включает в себя триггер со счётным запуском, т.е. синхронный Т-триггер. На рис. 5.5.14. приведена схема 3-х разрядного двоичного счётчика на сложение, она выполнена путём последовательного соединения трёх счётных триггеров. Счёт возможен от 0 до 7. Если надо увеличить N, то увеличивают количество разрядов подключением дополнительных триггеров.

|

|

| Рис. 5.5.14. Схема 3-х разрядного двоичного счётчика на сложение на трёх счётных триггерах | Рис. 5.5.15. Временные диаграммы работы счётчика |

Первый триггер – младший разряд, его сигнал  поступает на вход второго разряда, выход которого

поступает на вход второго разряда, выход которого  заведен на вход третьего разряда. Первый триггер переключается срезами входных импульсов. Срезом

заведен на вход третьего разряда. Первый триггер переключается срезами входных импульсов. Срезом  управляется второй триггер, а срезом

управляется второй триггер, а срезом  управляется третий триггер. Очевидно, что состояние разрядов счётчика представляет запись числа поступивших импульсов в двоичном коде, что подтверждается таблицей 5.5.3.

управляется третий триггер. Очевидно, что состояние разрядов счётчика представляет запись числа поступивших импульсов в двоичном коде, что подтверждается таблицей 5.5.3.

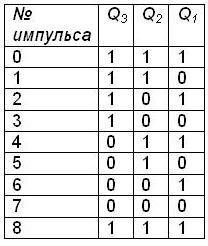

Таблица 5.5.3.

После записи максимального числа импульсов (в нашем случае – 7) счётчик автоматически обнуляется, т.е. устанавливается  . При дальнейшем поступлении импульсов начинается новый цикл счёта.

. При дальнейшем поступлении импульсов начинается новый цикл счёта.

На рис. 5.5.16. приведена схема двоичного 3-х разрядного счётчика на вычитание и таблица его состояний табл. 5.5.4.

Таблица 5.5.4.

|

|

Рис. 5.5.16. Схема двоичного 3-х разрядного счётчика на вычитание

Работа его заключается в том, что на вход триггера i -го разряда подается сигнал с инверсного выхода предыдущего разряда  . Переключение i -го разряда происходит по срезу

. Переключение i -го разряда происходит по срезу  импульса, т.е. по фронту импульса

импульса, т.е. по фронту импульса  (в отличие от счетчика на сложение, где переключение происходило по срезу

(в отличие от счетчика на сложение, где переключение происходило по срезу  импульса). Перед началом работы подачей сигнала на установочные входы триггеров устанавливается состояние:

импульса). Перед началом работы подачей сигнала на установочные входы триггеров устанавливается состояние:  . На счётчике имеет место запись линейно убывающих чисел по мере поступления входных импульсов.

. На счётчике имеет место запись линейно убывающих чисел по мере поступления входных импульсов.

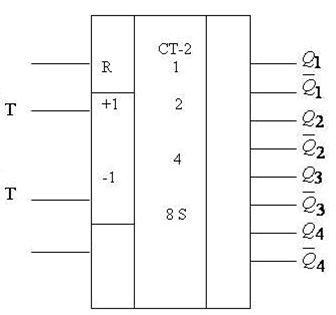

На практике возникает необходимость в счётчиках, которые могли бы поочередно осуществлять как сложение, так и вычитание поступающих импульсов. Такие счетчики называются реверсивными. Они имеют два счётных входа, при поступлении импульсов на один из которых идёт процесс сложения, а при поступлении на другой – вычитания из числа записанного в счётчике (первый вход обозначают " + ", а второй – " - "). Эти счетчики так же имеют установочные входы. Промышленность выпускает многочисленные счётчики в интегральном исполнении, в том числе и реверсивные, пример которого показан на рис. 5.5.17. Это ИМС 4-х разрядного реверсивного счётчика с установочными входами R и S для всех разрядов.

Рис. 5.5.17 Реверсивный счётчик

Выпускаются счётчики и с произвольным коэффициентом счёта, к примеру, на десять положений (счёт от 0 до 9), на 12 положений (от 0 до 11). Часто возникает необходимость построения счётчика с числом  . Такие счётчики называются счётчиками с произвольным коэффициентом счёта. Строятся такие счётчики на основе обычных двоичных счетчиков с исключением у них соответствующего числа "избыточных состояний". Число этих избыточных состояний находят, как:

. Такие счётчики называются счётчиками с произвольным коэффициентом счёта. Строятся такие счётчики на основе обычных двоичных счетчиков с исключением у них соответствующего числа "избыточных состояний". Число этих избыточных состояний находят, как:

–Kсч,

–Kсч,

где –  -количество состояний двоичного счетчика; Kсч – требуемый коэффициент (модуль) счёта (у обычного двоичного счетчика Kсч =

-количество состояний двоичного счетчика; Kсч – требуемый коэффициент (модуль) счёта (у обычного двоичного счетчика Kсч =  ). Способы создания таких счётчиков разнообразны, но все они базируются на введении обратных связей (ОС).

). Способы создания таких счётчиков разнообразны, но все они базируются на введении обратных связей (ОС).

Счётчики находят широкое применение в вычислительной технике и управляющих устройствах. В общем случае счётчики – это цифровые аналоги генераторов линейно изменяющихся напряжений.

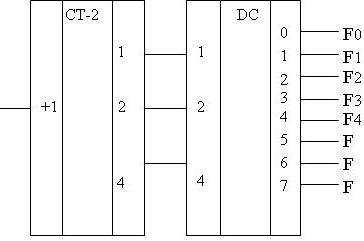

На основе счётчиков строятся распределители импульсов, т.е. устройства, формирующие импульсы поочередно на М -выходах. Реализуют их посредством сочетания счётчика и дешифратора, как показано для одного примера на рис. 5.5.18. Каждому числу, записанному на счётчике (в пределах счёта  ), соответствует появление импульса на соответствующем выходе дешифратора.

), соответствует появление импульса на соответствующем выходе дешифратора.

Рис. 5.5.18. Счётчики распределители импульсов

Date: 2015-05-09; view: 1433; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |