Полезное:

Как сделать разговор полезным и приятным

Как сделать объемную звезду своими руками

Как сделать то, что делать не хочется?

Как сделать погремушку

Как сделать так чтобы женщины сами знакомились с вами

Как сделать идею коммерческой

Как сделать хорошую растяжку ног?

Как сделать наш разум здоровым?

Как сделать, чтобы люди обманывали меньше

Вопрос 4. Как сделать так, чтобы вас уважали и ценили?

Как сделать лучше себе и другим людям

Как сделать свидание интересным?

Категории:

АрхитектураАстрономияБиологияГеографияГеологияИнформатикаИскусствоИсторияКулинарияКультураМаркетингМатематикаМедицинаМенеджментОхрана трудаПравоПроизводствоПсихологияРелигияСоциологияСпортТехникаФизикаФилософияХимияЭкологияЭкономикаЭлектроника

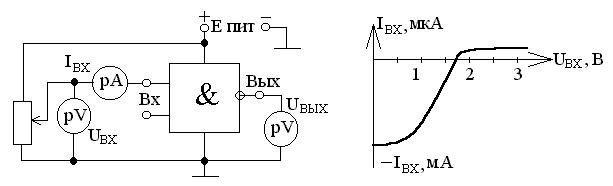

Характеристики ДТЛ

Схема для снятия входной характеристики IВХ= F(UВХ) и характеристики прямой передачи UВЫХ = F(UВХ) приведена на рисунке а. Входная характеристика приведена на рисунке 1.7б, а характеристика прямой передачи на рисунке 1.9а. При нулевом напряжении на входе через диод VD 1 протекает ток IВХ=(ЕПИТ- UА)/R1 (поскольку он вытекает, то он отрицательный). Транзистор закрыт, ток коллектора отсутствует и на выходе напряжение равно напряжению источника питания. При увеличении входного напряжения диод VD 1 закрывается и входной ток уменьшается.

а) б)

Рисунок 1.7

При напряжении равном примерно 1,8 В ток начинает протекать по цепи VD 3, VD 4 и эмиттерный переход транзистора (ток через эти переходы начинает протекать, когда напряжение на каждом их них достигнет 0,6 В, см. ВАХ кремниего диода). Через диод VD1 в этом случае начинает протекать обратный ток. Ток базы транзистора равен IБ=(EПИТ-UА)/R1. Транзистор в этом случае переходит в режим насыщения и напряжение на выходе снижается до уровня 0,1 В.

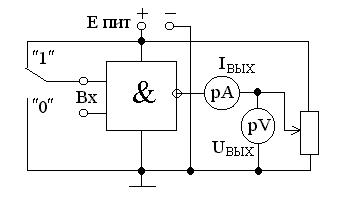

Схема для снятия выходной характеристики приведена на рисунке 1.8.

Рисунок 1.8

а) б)

Рисунок 1.9

Характеристики снимаются в двух случаях: на вход ИМС подается напряжение логического ²0² (можно подать 0 В) и напряжение, соответствующее логической ²1² (5 В). В первом случае транзистор закрыт и при напряжении, которое подается на выход ИМС с потенциометра, равное 0 В, ток будет равен ЕПИТ/R3, ток вытекает, поэтому он отрицательный. При подаче напряжения равного 5 В выходной ток будет равен 0.

Во втором случае, хотя транзистор открыт, он шунтируется милли -амперметром, и ток также будет равен ЕПИТ/R3. При увеличении напряжения, когда оно сравняется с напряжение насыщения транзистора (0,1 В) ток будет равен 0. При дальнейшем увеличении выходная характеристика ИМС будет повторять выходную характеристику транзистора. (Она показана пунктиром, так как мощность рассеивания на коллекторе превышает допустимую).

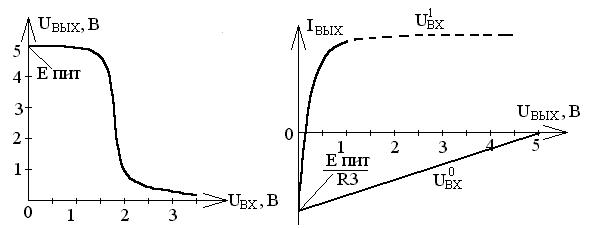

1.4 Транзисторно – транзисторная логика.

На рисунке 1.10а представлена структура диодов VD1-VD3 схемы ДТЛ. В интегральном исполнении области р можно объединить, и тогда получится структура изображенная на рисунке 1.10б. Эта структура представляет собой транзистор с двумя эмиттерами (двухэмиттерный транзистор).

а) б)

Рисунок 1.10

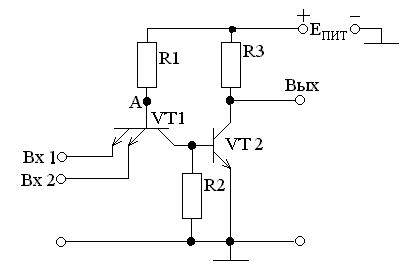

Если в предыдущей схеме ДТЛ диоды VD 1, VD 2 и VD 3 заменить на двухэмиттерный транзистор, то получится транзисторно – транзисторная логика (ТТЛ), принципиальная схема которой приведена на рисунке 1.11.

Рисунок 1.11

В качестве VT1 можно использовать транзистор с большим числом эмиттеров, схема в этом случае будет иметь соответствующее число входов.

Принцип работы, таблица истинности и характеристики ТТЛ такие же, как у ДТЛ.

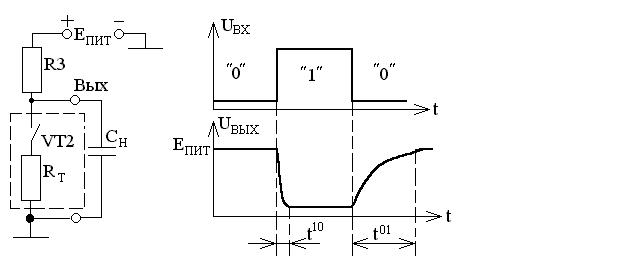

Недостаток предыдущих схем заключается в следующем. Заменим транзистор VT2 ключом с сопротивлением RТ (рисунок 1.12а).

В исходном состоянии (на входе схемы логический ²0²), транзистор закрыт (ключ разомкнут), на выходе напряжение равно напряжению питания ЕПИТ (рисунок 1.12б). При подаче на вход логической ²1²ключ замыкается. В этом случае ёмкость нагрузки СН разряжается через малое сопротивление ключа RT и время включения будет составлять t10. При подаче на вход логического²0² ключ вновь размыкается и, в этом случае, ёмкость СН будет заряжаться через сопротивление R3, которое намного больше, чем RT и время выключения будет t01> t10, из-за этого быстродействие схемы будет низким.

а) б)

Рисунок 1.12

Кроме того между точкой А и общим проводом находятся два pn-перехода, следовательно на эмиттерном переходе при подаче на вход логического ²0² напряжение будет составлять 0,4 В и для того, чтобы открыть транзистор надо приложить меньшее напряжение, т.е. помехо-устойчивость схемы снижается.

Задача состоит в том, чтобы снизить t01 (t01» t10) и повысить помехоустойчивость.

Date: 2015-05-09; view: 739; Нарушение авторских прав; Помощь в написании работы --> СЮДА... |